Journal of Electrical Engineering

Vol.03 No.04(2015), Article ID:16487,8

pages

10.12677/JEE.2015.34013

Modeling and Analysis of a Novel All-Digital Phase-Locked Loop Based on FPGA

Bin Yi, Feng Pan, Guoying Lin, Wei Zhao

Electric Power Research Institute of Guangdong Power Grid Corporation, Guangzhou Guangdong

Received: Nov. 16th, 2015; accepted: Dec. 1st, 2015; published: Dec. 8th, 2015

Copyright © 2015 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

This paper proposed a novel all-digital phase-locked loop (ADPLL). By using the self-sampling PI control method, it can obtain a phase-locked output signal without steady-state error and with less jitter. The designed ADPLL is able to adjust the mode number of the digital loop filter according to the phase error between the two input signals of the digital phase detector. In this way, the ADPLL can optimize the lock-in speed when the system stability is also guaranteed. The paper establishes the mathematical model of the ADPLL based on the analysis of the operating characteristic of each module. Using the obtained system transfer function, the paper analyzes the performance parameters of the ADPLL, and provides the guiding principle of the parameters design. The validity of theoretical analysis is verified by experimental test in the final of this paper.

Keywords:All-Digital Phase-Locked Loop, PI Control, Mathematical Modeling, Parameter Analysis

一种基于FPGA的新型全数字锁相环的建模 与分析

易斌,潘峰,林国营,赵伟

广东电网有限责任公司电力科学研究院,广东 广州

收稿日期:2015年11月16日;录用日期:2015年12月1日;发布日期:2015年12月8日

摘 要

提出了一种新型的全数字锁相环,其采用自采样比例积分控制,使得锁相输出无静差,输出抖动小,并能根据数字鉴相器输入信号间相位误差的大小,调节数字环路滤波器的计数模数,在保证锁相环稳定性的同时,提高了锁相环锁定速度。本文基于该全数字锁相环各模块工作特性的分析,建立了全数字锁相环的数学模型,利用所得到的锁相环系统传递函数进行了性能参数分析,并给出了锁相环参数设计指导原则。论文最后通过实验测试验证了理论参数分析的正确性。

关键词 :全数字锁相环,比例积分控制,数学建模,参数分析

1. 引言

锁相环是一种非常简单而又实用的电路,它能使输出信号与输入参考信号在频率和相位上保持同步,在同步状态(或者称为锁定状态),锁相环输出信号和输入信号之间的相位差为零或一个常数[1] 。在电力电子装置中,锁相环技术常被用于位置跟踪、信号同步以及电信号频率和相角参数提取等[2] -[4] 。锁相环按照实现的方式不同可以分成模拟锁相环、数字锁相环和全数字锁相环。随着数字技术的发展,基于FPGA的全数字化解决方案正越来越多地应用到锁相环的设计中,相比其它形式的设计方案,基于FPGA的全数字锁相环具有并行运行、纯硬件化特点,在减少锁相环系统延时和量化误差方面具有突出的优势。

在全数字锁相环中,锁相环的基本组成模块有:数字鉴相器(Digital Phase Detector: DPD)、数字环路滤波器(Digital Loop Filter: DLF)和数字控制振荡器(Digitally Controlled Oscillator: DCO)。DPD、DLF和DCO三个模块的实现分别有多种方式,不同设计方法都将会使得锁相环系统性能存在一定的差异。一个性能优越的锁相环应当具备锁定速度快、捕捉范围宽、锁定误差小和抗干扰能力强等特征。一般来说,通过选择含积分量的DLF能较好地控制系统的稳态锁定误差,但对于脉冲输入的全数字锁相环,为了抑制输入信号抖动带来的不良影响,通常需要在环路正向通道中加入脉冲序列低通滤波模块来消除DPD输入信号抖动的影响,其中“N先于M”环路滤波较为常用。然而,常用的脉冲序列低通滤波模块只能对DPD输出相位误差脉冲的个数计数,无法像文献[5] 那样利用相位误差信号脉宽与相位误差大小之间的关系,在提高锁相速度的同时保证锁定状态的稳定性。此外,全数字化后的锁相环虽然具有性能稳定、集成度高和设计灵活等优点,但由于DPD、DLF和DCO三个模块的数字化和非线性特性,使得全数字锁相环的数学建模变得十分困难,因此在许多文献中都未对所设计的全数字锁相环进行数学建模和参数性能分析,也未能给出所提出的全数字锁相环参数设计的指导原则。

针对以上问题,本文提出了一种基于随机游走滤波器的全数字锁相环。在设计的锁相环中,随机游走滤波器的模数可以根据相位参考信号和相位反馈信号之间相位差的大小自动变化,使得随机游走滤波器不仅可以有效抑制DPD输入信号抖动的干扰,而且可以在相位误差大是减小控制周期来提高锁定速度,在相位误差小时增大控制周期来提高锁定的稳定性和精度。此外,本文基于所设计的全数字锁相环各模块的工作特性的分析,建立了该全数字锁相环的Z域线性模型,基于性能参数分析给出了参数设计指导原则,并使用Verilog HDL硬件描述语言在FPGA上完成了该锁相环的设计,通过实验验证了设计的正确性和有效性。

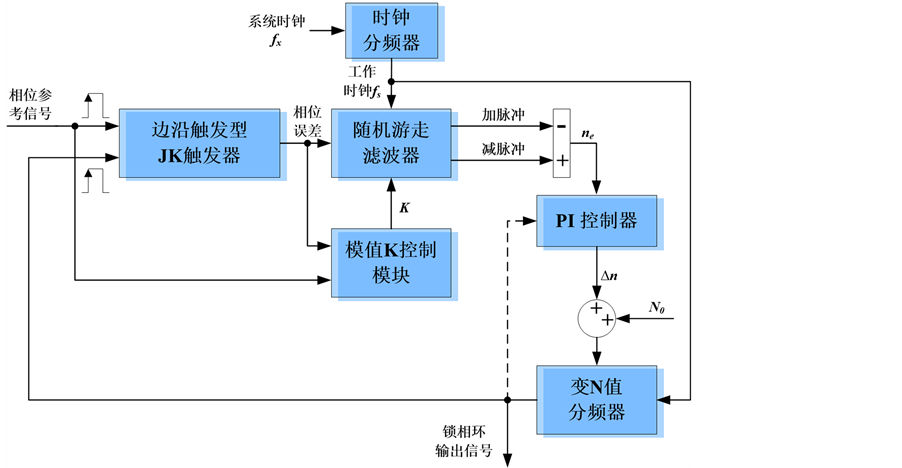

2. 全数字锁相环的构成及其工作原理

本文提出的全数字锁相环结构框图如图1所示。在图1中,fx是FPGA芯片输入的晶振源时钟,fs是经过时钟分频器分频之后的锁相环电路的参考时钟。本文设计的全数字锁相环选用边沿触发型JK触发器作为数字鉴相器环节,JK触发器的两个输入分别是前面提到的相位参考信号(即被锁定信号)和相位反馈信号(即锁相环输出信号),这两个信号都是逻辑值为1或0的脉冲信号,高低电平的占空比相等。JK触发器在检测到相位参考信号的上升沿时输出置位(输出逻辑1),在检测到相位反馈信号的上升沿时输出复位(输出逻辑0)。JK触发器输出的逻辑脉冲信号的占空比即反映了相位参考信号和相位反馈信号之间的相位差。当相位反馈信号和相位参考信号相位相反时,JK触发器输出的相位误差脉冲信号是一个频率与相位参考信号频率相等的对称方波,把这种情况视作相位反馈信号与相位参考信号的相位误差为零;当JK触发器输出脉冲信号逻辑高的占空比为100%时,认为相位反馈信号与相位参考信号的相位误差为180˚;当JK触发器输出脉冲信号逻辑高的占空比为零时,认为相位反馈信号与相位参考信号的相位误差为−180˚。

鉴相器输出的相位误差信号输入到随机游走滤波器(Random Walk Filter),随机游走滤波器的主要作用是根据输入的相位误差信号进行向上或向下的加或减计数,并输出加脉冲和减脉冲 [6] 。假设计数器的初值为K,当滤波器输入的相位误差信号为逻辑1时,计数器在参考时钟的控制下向上进行加法计数,计数器计数到2K时,滤波器会输出一个加脉冲信号,同时计数器的计数值复位为K;当滤波器输入的相位误差信号为逻辑0时,计数器在参考时钟的控制下向上进行减法计数,计数器计数到0时,滤波器会输出一个减脉冲信号,同时计数器的计数值复位为K。随机游走滤波器就是这样根据输入相位误差信号进行加或减计数,并输出相应的加/减脉冲。由随机游走滤波器的工作过程可知,当相位误差信号的占空比等于50%时,加脉冲和减脉冲的个数相等;当相位误差信号的占空比大于50%时,加脉冲的个数大于减脉冲的个数;相位误差信号的占空比小于50%时,加脉冲的个数小于减脉冲的个数。随机游走滤波器不仅将相位误差信号进行了量化,而且能够有效地抑制输入信号的抖动。随机游走滤波器中的计数器的K值由模值K控制模块进行控制。模值K控制模块基于对相位误差信号反映的相位差值大小的估计对输出K值进行控制,当相位差值较大时,该模块为随机游走滤波器选择适当较大的K值,以加快锁相环的跟踪锁定过程;当相位差值较小时,该模块为随机游走滤波器选择适当较小的K值,以减小锁相环锁定状态下的相位控制静态误差。

随机游走滤波器输出的加脉冲和减脉冲通过计数综合处理之后,鉴相器输入信号的相位误差被量化为数值ne,量化后的相位误差经过全数字锁相环内部的比例积分控制器后得到控制量Δn。控制量Δn与锁相环中心频率分频值N0的和控制着变N值分频器的分频值,变N值分频器即为全数字锁相环的数字控制振荡器,改变该模块的分频计数值就可以改变其输出信号的频率。变N值分频器只有在上一个分频计数周期结束之后才会更新分频计数值N,因此其输出信号是逐周期变频的。变N值分频器输出逻辑脉冲信号实际上是一个对称的方波信号,该信号一方面被向锁相环外部输出,另一方面作为内部反馈信号控制加脉冲和减脉冲的计数综合。

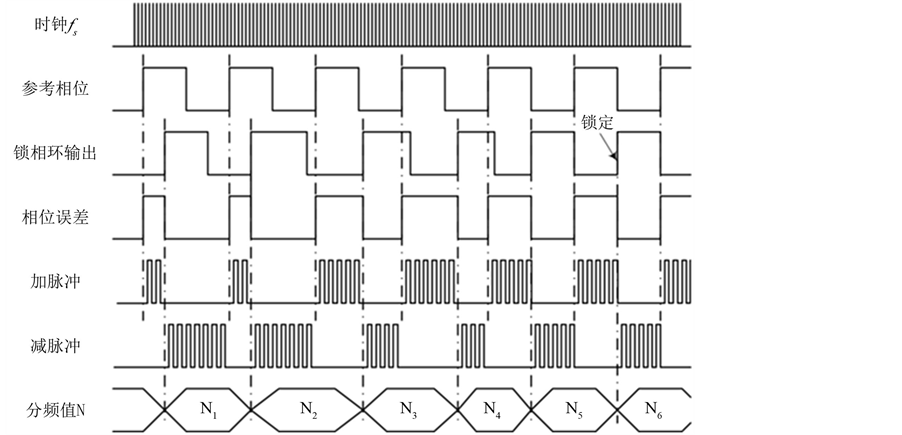

为了更清晰地表示全数字锁相环工作原理,当模值K控制模块输出K值固定,且开关网络将变N值分频器输出信号选作数字鉴相器的相位反馈信号时,所设计的全数字锁相环的一组工作波形图如图2所示。从图中可以看出,起初变N值分频器输出信号不与相位参考信号的相位相反,鉴相器输出的相位误差信号的占空比小于50%,锁相环经历一个暂态的锁定跟踪过程,在第5个控制周期结束后,实现变N值分频器输出信号与相位参考信号的同步。如前所述,N值分频器在每一个分频计数周期结束之后才更新计数分频值N。本文所设计的全数字锁相环在变N值分频器输出信号的上升沿对上一个控制周期内加

Figure 1. Block diagram of the proposed all-digital phase-locked loop

图1. 提出的全数字锁相环结构框图

Figure 2. Operation waveform of the proposed all-digital phase-locked loop

图2. 全数字锁相环工作波形示意图

脉冲和减脉冲的个数进行计数综合,通过计算得到变N值分频器新周期的分频值,并对加脉冲和减脉冲的计数进行清零,因此,全数字锁相环实质上采用了自采样的比例积分控制[7] 。锁相环输出信号相位锁定之后,输出信号的频率等于相位参考信号的频率和相位一致。

3. 全数字锁相环建模及性能参数分析

3.1. 数学建模

为了对锁相环的特性进行研究,并进行锁相环的参数设计,首先需要对所设计的新型全数字锁相环进行建模分析。然而,全数字锁相环自身的数字化和非线性特征使得其系统建模非常困难,而且目前对于锁相环的数学建模都没太好的办法 [3] [8] 。本文将基于所设计的全数字锁相环各模块的工作特性的分析,建立锁相环的线性模型。

显然,相位参考信号的相位θr可以用相位参考信号的频率ωr的时间积分来表示,在离散时间域,可以用如下方程来表达

(1)

(1)

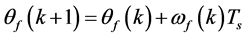

其中,Ts=1/fs是系统采样时间周期。那么同样地,相位反馈信号的相位θf也可以用相位反馈信号的频率ωf进行类似的表示,即

(2)

(2)

图1中的沿触发型JK触发器可以被建模为一个减法器。因此,在每一个系统采样周期内,相位反馈信号与相位参考信号之间的相位差可以表示成

(3)

(3)

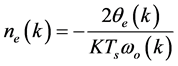

按照随机游走滤波器的工作原理,加脉冲和减脉冲计算综合输出的误差值ne与鉴相器输出的相位差之间关系可以近似表示成

(4)

(4)

其中,ωo是变N值分频器输出信号的频率,K为随机游走滤波器中计数器的模值。在实际应用中,不管相位反馈信号是负载电流相位信号,还是变H值分频器输出信号,都有ωo = ωf成立。图1中比例积分模块输出和输入之间的数学关系为

(5)

(5)

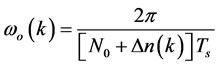

变N值分频器输出信号的频率为

(6)

(6)

在实际应用中,全数字锁相环的中心频率通常可以设置为与被跟踪相位参考信号的频率一致,这样全数字锁相环在完成参数配置之后,全数字锁相环输出将很快完成相位的跟踪锁定过程。一般情况下,可以近似认为全数字锁相环一直工作在中心频率点附近,则可以据此对式(1)至式(6)进行线性化简。

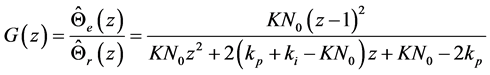

假设离散时间序列x(k)的Z变换用X(z) = Ƶ[x(k)]来表示,图3给出了全数字锁相环Z域线性模型框图。利用该线性模型,可以得到相位误差角θe对相位参考信号相位θr的误差传递函数

(7)

(7)

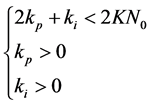

为了保证用式(7)表示的闭环系统稳定,依据Jury稳定性测试[9] ,必须保证以下等式组成立,即

(8)

(8)

从式(7)可以发现,当锁相环的系统采样时钟确定后,锁相环的动静态性能由三个参数决定:比例系数kp、积分系数ki和随机游走滤波器计数模值K。N0是变N值分频器的初始分频值,它对应锁相环的中

心频率,不同的N0代表了锁相环不同的中心频率,也暗示了锁相环输入的相位参考信号频率不同。

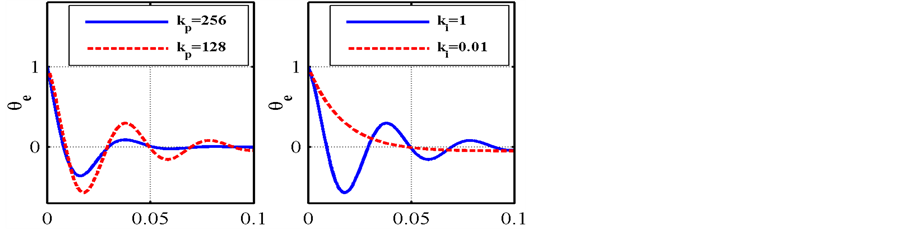

3.2. 系统性能参数分析

图4给出了不同参数下误差传递函数G(z)的单位阶跃响应,从图中的结果可以得出如下结论:1) kp越大,相位误差θe振荡的幅度越小且衰减至零的速度越快,即锁相环的锁定速度越快、稳定性越好;2) ki越小,锁相环系统的阻尼系数越大,θe越不容易振荡,即增加了锁相环的稳定裕度,却减缓了系统的响应速度;3) 如果随机游走滤波器计数模值K减小,锁相环系统的响应速度变快,系统相位锁定跟踪的过程变短,这与前面介绍模值K控制器模块的功能时的描述一致;4) 当N0值越大,即相位参考信号的频率越低时,锁相环系统相位锁定跟踪的过程越长。

4. 系统实现及性能测试

为了验证以上设计和理论分析的正确性,本文采用Verilog HDL 硬件描述语言在FPGA上完成了所提出的全数字锁相环的系统设计,FPGA芯片采用型号为Cyclone II EP2C35F672C6芯片。测试时,全数字锁相环的系统时钟为50 MHz,输入相位参考信号的频率为4 kHz,PI控制器的积分参数ki取值为1,锁相环模值K控制模块输出固定K值为32。由于设计的锁相环选用边沿触发型JK触发器作为数字鉴相器,当锁相环输出信号与相位参考信号的相位相反时,锁相环进入锁定状态。

Figure 3. The block diagram of the linear model for the proposed ADPLL

图3. 全数字锁相环的线性模型框图

(a) 时间(ms) (b) 时间(ms)

(a) 时间(ms) (b) 时间(ms) (c) 时间(ms) (d) 时间(ms)

(c) 时间(ms) (d) 时间(ms)

Figure 4. Step response of error transfer function G(z) with different parameters

图4. 不同参数条件下误差传递函数G(z)的单位阶跃响应

(a) 动态特性 (b) 稳态特性

(a) 动态特性 (b) 稳态特性

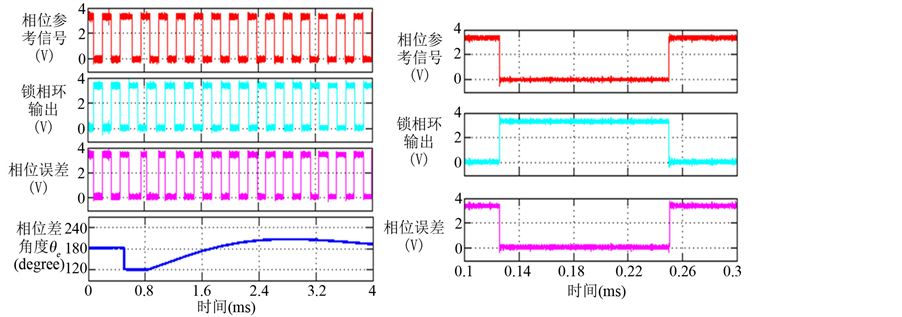

Figure 5. Dynamic-state and steady-state performance with a phase jump of −60˚ when kp = 4

图5. 当kp = 4时发生−60˚相位差阶跃的锁相环动态和稳态性能

(a) 动态特性 (b) 稳态特性

(a) 动态特性 (b) 稳态特性

Figure 6. Dynamic-state and steady-state performance with a phase jump of −60˚ when kp = 16

图6. 当kp = 16时发生−60˚相位差阶跃的锁相环动态和稳态性能

图5和图6分别给出了全数字锁相环PI控制器的比例系数kp取不同值时,锁相环的相位差阶跃动态响应性能和稳态性能。如图5和图6所示,两组参数设置条件下,锁相环的稳态相位误差几乎可以忽略。当输入相位参考信号的相位发生−60˚的相位阶跃时,锁相环鉴相器输出相位误差也将发生−60˚的相位阶跃,锁相环将经历一个相位跟踪的暂态过程。对比图5和图6的测试结果可以发现,锁相环PI控制器的比例系数kp取值越大时,锁相环的动态响应速度越快,锁定跟踪的时间更短,这一测试结果与建模分析的结论一致。通过这种测试,可以进一步验证系统其它参数性能特征也与理论分析一致。

5. 结论

本文提出了一种基于随机游走滤波器的全数字锁相环,该锁相环可以根据相位参考信号和相位反馈信号之间相位差的大小动态改变随机游走滤波器的模数,在提高锁相环锁定速度的同时,也能很好地保证锁相环锁定的稳定性和精度。并通过自采样比例积分控制获得了较好的无静差控制性能。论文通过线性化近似获得了全数字锁相环的离散域数学模型,给出了锁相环系统参数特性及系统参数设计指导原则,并通过实验进行了验证。所提出的全数字锁相环具有锁定范围大、锁定速度和锁定精度高等优点,能很方便地应用到基于FPGA的数字控制器中,适用于频率和相位需要快速同步跟踪控制的应用场合。

基金项目

国家高技术研究发展计划(863计划资助项目) (2015AA050404);南方电网公司项目(K-GD2013-0473)。

文章引用

易 斌,潘 峰,林国营,赵 伟. 一种基于FPGA的新型全数字锁相环的建模与分析

Modeling and Analysis of a Novel All-Digital Phase-Locked Loop Based on FPGA[J]. 电气工程, 2015, 03(04): 99-106. http://dx.doi.org/10.12677/JEE.2015.34013

参考文献 (References)

- 1. Best, R.E. 锁相环设计, 仿真与应用[M]. 第5版. 李永明, 王海永, 肖珺, 等, 译. 北京: 清华大学出版社, 2007.

- 2. Guan-Chyun, H. and Hung, J.C. (1996) Phase-Locked Loop Techniques: A Survey. IEEE Transactions on Industrial Electronics, 43, 609-615. http://dx.doi.org/10.1109/41.544547

- 3. Geng, H., Sun, J.B., Xiao, S., et al. (2013) Modeling and Implementation of an All-Digital Phase-Locked-Loop for Grid-Voltage Phase Detection. IEEE Transactions on Industrial Informatics, 9, 772-780. http://dx.doi.org/10.1109/TII.2012.2209666

- 4. Kim, N.G. and Ha, I.J. (1999) Design of ADPLL for Both Large Lock-In Range and Good Tracking Performance. IEEE Transactions on Circuits and Systems II-Analog and Digital Signal Processing, 46, 1192-1204. http://dx.doi.org/10.1109/82.793709

- 5. 肖帅, 孙建波, 耿华, 等. 基于FPGA实现的可变模全数字锁相环[J]. 电工技术学报, 2012, 27(4): 153-158.

- 6. Shiga, N. (1988) Digital Phase-Locked Loop with Random Walk Filter. US Patent, 4791386.

- 7. 李亚斌, 彭咏龙, 李和明, 等. 自采样比例积分控制全数字锁相环的性能分析和实现[J]. 中国电机工程学报, 2005, 25(18): 64-69.

- 8. 庞浩, 俎云霄, 王赞基. 一种新型的全数字锁相环[J]. 中国电机工程学报, 2003, 23(2): 37-41.

- 9. Astrom, K.J. and Wittenmark, B. 计算机控制系统: 原理与设计[M]. 第三版. 周兆英, 林喜荣, 刘中仁, 译. 北京: 电子工业出版社, 2001.