Open Journal of Circuits and Systems

Vol.04 No.02(2015), Article ID:15383,8

pages

10.12677/OJCS.2015.42004

Design of Driving Linear CCD in Laser Displacement Sensor

Minjie Yuan, Ji Chen

Union College of Biomedical Engineering, Chongqing University, Chongqing

Email: cixiyuanminjie@163.com

Received: May 20th, 2015; accepted: Jun. 2nd, 2015; published: Jun. 9th, 2015

Copyright © 2015 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

A design of driving linear CCD based on CPLD was proposed, which was fit for laser displacement sensor. A unique timing generation method was proposed through the analysis of timing of TCD1703C. The scanning frequency can be changed, which is different from the past. There are four scanning frequencies to choose and the highest is 10 MHz. The timing code was written in Verilog language. Modelsim, Timequest and other EDA tools were used to constrain timing and optimize it. A circuit based on programmable amplifier was designed for signal processing. A test system was established and this driving method was tested on it. The result showed that the test system worked normally with all scanning frequencies and the signal from CCD was excellent. This design is suitable for CCD laser displacement sensor.

Keywords:Laser Displacement Sensor, CCD, CPLD, Drive, TCD1703C, Signal Processing

激光位移传感器中线阵CCD驱动方法的设计

袁敏杰,陈骥

重庆大学生物医学工程联合学院,重庆

Email: cixiyuanminjie@163.com

收稿日期:2015年5月20日;录用日期:2015年6月2日;发布日期:2015年6月9日

摘 要

针对CCD在激光位移传感器中的应用,介绍了一种基于CPLD的线阵CCD驱动方法。对TCD1703C型号的CCD工作时序做了分析,设计了独特的时序产生方法,使CCD的扫描频率可在四种频率间切换,最高达10 MHz。采用Verilog语言编写了驱动代码,结合Modelsim、Timequest等EDA工具进行时序检查与约束。针对CCD信号峰值随扫描频率变化而变化的特点,设计了基于程控放大器的信号处理电路。最后搭建了测试系统,对该驱动方法进行实验验证。实验结果表明测试系统在四种扫描频率下都能正常工作,获得的CCD信号合适,满足激光位移传感器的应用需求。

关键词 :激光位移传感器,CCD,CPLD,驱动,TCD1703C,信号处理

1. 引言

激光位移传感器以其高精度、高效率、高可靠性等优点,应用于精密零件的形位和位置公差的检测中[1] 。CCD (电荷耦合器件)是激光位移传感器的主要部件之一,其性能直接影响到系统的测量结果。只有符合激光位移传感器工作要求的CCD驱动方法才能保证测量结果准确。

在驱动CCD时要解决的两个主要问题分别是驱动时序的产生和输出信号的采集处理[2] 。在驱动时序产生方面,以往的研究大多只以成功驱动CCD为目的,因此扫描频率不高,一般采用器件的典型频率1 MHz或者更低[3] -[5] 。偶有专门研究讨论高速驱动CCD的方法,但多是在面阵CCD上进行验证[6] 。以往的驱动方法一般只针对一种扫描频率,而激光位移传感器要求在不同工作模式下CCD扫描频率要改变。在输出信号的采集处理方面,除了信号反相放大和滤波这些常见的处理外,以往一般研究的是如何消除CCD的复位噪声和暗电流噪声[7] [8] 。但在激光位移传感器的应用中,实验结果表明复位噪声和暗电流噪声对测量的影响并不明显。以往的研究中CCD受到的光照一般较强,但激光位移传感器中CCD接收的是漫反射的弱光,当扫描频率较高时输出信号急剧衰减,如何处理好不同扫描频率下的CCD信号是必须解决的问题之一。综上所述,有必要设计一种针对在激光位移传感器中应用的线阵CCD驱动方法。

2. 总体设计

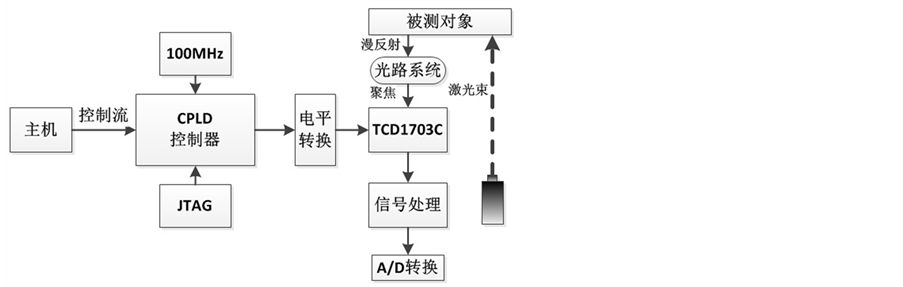

目前常见的CCD驱动时序产生方法主要有EPROM法、专用IC法、单片机法以及可编程逻辑器件法[9] 。其中可编程逻辑器件法是利用CPLD (复杂可编程逻辑器件)或FPGA (现场可编程门阵列)等可编程逻辑器件来产生驱动时序信号,具有速度快、灵活性高、调试容易等特点。激光位移传感器中要求CCD扫描频率最高达到10 MHz,并且扫描频率视工作模式可变换,因此可编程逻辑器件法是最佳选择。本设计选用Altera公司的MAX II系列CPLD来产生所需时序信号,采用100 MHz有源晶振作为外部时钟源,可以轻松产生10 MHz扫描频率。采用Verilog语言编写驱动代码并根据情况进行时序优化,用Modelsim以及Quartus II集成的Timequest进行时序约束与检查。系统工作时,由CPLD实时接收主机发来的控制指令并根据指令切换CCD扫描频率。为了提高激光位移传感器的分辨率,CCD采用了包含7500个有效像元的TCD1703C。针对CCD在激光位移传感器中的应用特点设计了信号处理电路,使信号适合模数转换。该驱动方法的工作原理如图1所示。

3. 驱动时序设计

3.1. TCD1703C时序分析

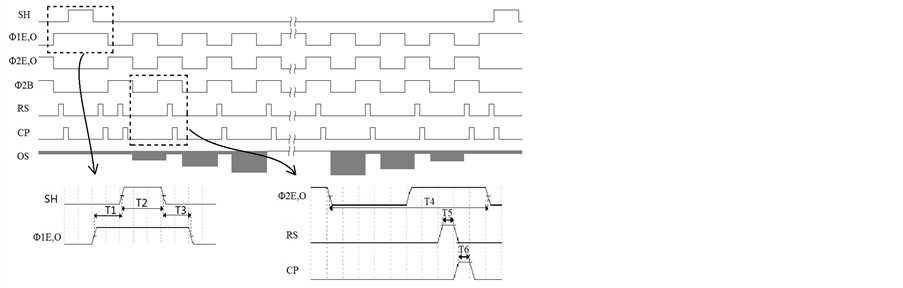

图2所示为TCD1703C的时序图,除OS是CCD输出信号外,其余6个都是需要输入的驱动脉冲。

这6个驱动脉冲的作用和特点如下所述:

SH:转移脉冲。在光积分阶段,SH为低电平;当SH为高电平时,光积分阶段产生的电荷被存入模拟移位寄存器,以便在相位脉冲驱动下被取出。值得注意的是SH的低电平持续时间应根据光亮度和扫描频率进行适当选择。

Ф1E,O:相位脉冲1。该脉冲是模拟移位寄存器的驱动信号,每输入一个脉冲则从OS引脚移出一位信号,直至将所有信号移出。

Ф2E,O:相位脉冲2。由于TCD1703C是两路输出的CCD芯片,因此有Ф1E,O和Ф2E,O两个相位信号,分别负责两路信号的移位。Ф1E,O和Ф2E,O相位差180˚。

Ф2B:最终阶段脉冲。与Ф2E,O一致。

RS:复位脉冲。用于清除模拟移位寄存器中的残留电荷。

CP:钳位脉冲。将输出信号钳位在零信号电平[10] 。

从时序图中可以看出,Ф1E,O和Ф2E,O是完全反相的,因此只要设计出Ф1E,O的时序,然后通过一个求反逻辑就可以得到Ф2E,O。Ф2E,O和Ф2B时序完全相同,可以直接替代。RS和CP在相位上相差了一个高电平时间,因此可以通过将RS延迟一个高电平的时间来得到CP。如此一来产生六个信号缩

Figure 1. The principle of work

图1. 驱动工作原理

Figure 2. TCD1703C timing

图2. TCD1703C时序图

减为产生SH、Ф1E,O和RS这三个信号。

TCD1703C的驱动时序中有两处时序关系是相当重要的,直接影响CCD正常工作与否。它们分别是SH高电平阶段,SH与Ф1E,O的时序关系;以及SH低电平阶段,Ф2E,O与RS、CP的时序关系。放大后如图2下部分所示,其中各时间的约束如表1所示。

3.2. 基于Verilog的TCD1703C时序设计

从数据手册可知RS和CP的典型占空比为1/10。假如要求CCD扫描频率为1 MHz,令时钟频率为10 MHz,那么RS和CP的高电平持续时间就是一个时钟周期,RS通过一个时钟周期的延迟就能得到CP。可见将时钟频率取为扫描频率的10倍可以简化时序设计。CCD激光位移传感器中要求CCD的扫描频率为1 MHz、2 MHz、5 MHz和10 MHz,分别需要10 MHz、20 MHz、50 MHz和100 MHz的时钟。CPLD的外部时钟源为100 MHz,设计一个分频模块CLKDIV对外部时钟分频得到上述四种内部时钟。

每两个SH高电平之间需要3825个Ф1E,O脉冲,如果定义一个寄存器CNT1对Ф1E,O脉冲进行计数,那么可以将整个时序分成两种情况:CNT1 = 0和CNT1 > 0。CNT1 = 0对应SH高电平即电荷转移阶段,CNT1 > 0对应SH低电平即光积分阶段。定义一个寄存器CNT2在每一个CNT1周期对内部时钟进行计数,分CNT1 = 0和CNT1 > 0两种情况,当CNT2计数到相应值时对SH、Ф1E,O和RS的电平进行翻转,就可以得到所需SH、Ф1E,O和RS的时序。

上述是一种比较通用的方法,适合单一频率驱动TCD1703C,只要稍加修改就能用于驱动其他型号的线阵CCD。然而本设计中要求扫描频率可变,由于描频率对应的内部时钟频率是不同的,如果仍然按照相同的CNT2计数值来对SH、Ф1E,O和RS的电平进行翻转,必定造成时序错误。以产生SH高电平为例,假如CNT = 0时SH高电平持续30个内部时钟,由于2 MHz扫描频率对应内部时钟为20 MHz,所以SH高电平持续典型值1500 ns。然而如果扫描频率为10 MHz,其对应时钟频率为100 MHz,则SH高电平只能持续300 ns,将不符合表1的时间约束。所以不同扫描频率下CNT2的计数值应分别选取。产生CNT1和CNT2的关键代码如下所示,代码中的X要根据不同的扫描频率合理设置。

if(CNT1==0) begin

if(freqsel==0) begin

if(CNT2

CNT2<= CNT2+1'b1;

else begin

CNT1<= 1'b1;

CNT2<=0;

end

end

else if(freqsel==1) begin

……

else if(CNT1 <3825) begin

if(CNT2 <9)

CNT2 <= CNT2 +1'b1;

else begin

CNT2 <=0;

CNT1 <= CNT1 +1'b1;

end

else

CNT1<=0;

end

产生Ф1E,O的关键代码如下所示,代码中的Y要根据不同的扫描频率合理设置。产生SH和RS的方式与产生Ф1E,O的方式类似。

if(CNT1==0) begin

if(freqsel==0) begin

if(CNT2

else a_r<=1;

end

else if(freqsel==1) begin

……

end

else begin

if(cnt1<5) a_r<=0;

else a_r<=1;

end

此外,上述方法中如果扫描频率为10 MHz,那么RS和CP的高电平持续时间(T4)和信号偏移(T5)理论上为10 ns,达到了它们的最小允许值。由于信号传输过程中有延迟,并且信号本身存在建立和保持时间,导致T4和T5可能小于10 ns。所以在10 MHz扫描频率时将RS和CP的高电平持续时间改为两个时钟周期(20 ns)是比较稳妥的。

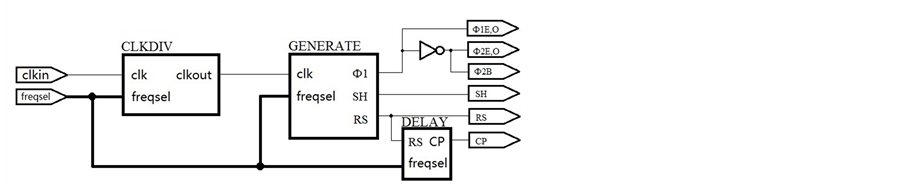

图3所示是连接起来的顶层模块示意图。

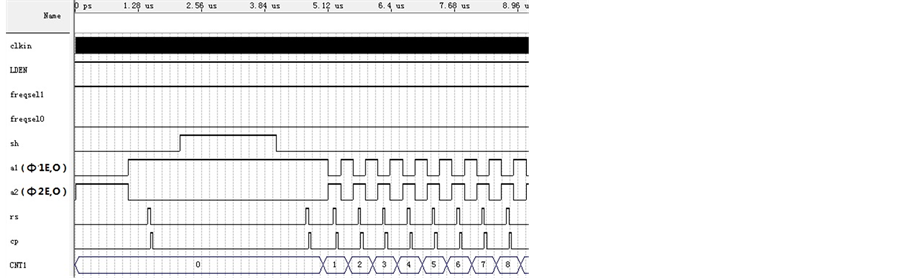

最后利用Modelsim进行时序仿真,CCD扫描频率设定为2 MHz,得到图4所示的时序波形。LDEN控制使能,freqsel [1:0]选择扫描频率。图中SH、Ф1E,O、Ф2E,O、RS和CP的时序基本满足TCD1703C数据手册的要求。CNT1在起始阶段为0,随后每来一个扫描脉冲就自增1,直至自增到3825后复位归零。

4. 硬件电路设计

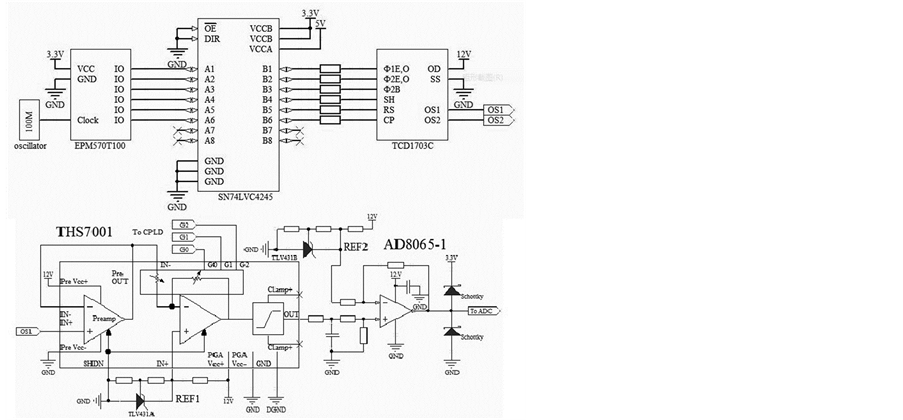

选用Altera公司的MAX II系列芯片EMP570T100来产生所需时序信号,CCD传感器则采用东芝公司的高灵敏度、低暗电流器件TCD1703C。由于EMP570T100的IO接口采用3.3V CMOS逻辑,而TCD1703C采用5V逻辑,因此在EMP570T100与TCD1703C之间使用一片SN74LVC4245进行电平转换。

因为涉及到100 MHz高速信号,所以利用Quartus II自带的时序约束工具Timequest进行了时序约束

Table 1. Timing constraints

表1. 信号的时间约束

与检查。已知外部的晶振时钟频率为100 MHz,分频模块产生的时钟频率最高为100 MHz,因此将外部时钟源和分频时钟分别约束为100 MHz。已知EPM570T100有三种速度等级,从高到低分别为C3、C4和C5。对EPM570T100的这三种速度等级芯片分别进行检查,编译后发现Setup Time Slack (建立时间余量)存在表2所示的差异。

从表2可知,C5速度等级芯片的建立时间余量小于零,不符合要求,因此必须选用C3或C4等级的芯片。在时序仿真中也发现,若扫描频率为10 MHz且选用C5等级芯片,则时序波形偶尔出现混乱的情况,印证了上述结论。本设计从器件的获得难易程度考虑,最终选择了EPM570T100C4芯片作为时序产生芯片。

从数据手册可知,CCD的原始输出信号是反相的;从实验中发现,设定亮度范围的激光照射在被测物面上形成的光点漫反射后,通过物镜聚焦照射在CCD上,CCD的原始输出信号幅值只有数十至数百毫伏。为了获得合适的CCD信号,设计了一个信号预处理电路,主要起到反相放大、低通滤波和钳位二极管保护功能。反相放大采用二级放大结构,在下一段详述。低通滤波采用一阶无源阻容电路,能有效减少信号中的高频噪声。当CCD处于上电状态但无驱动时钟时,其输出电压并不是直流偏置电压5.5 V,而是0 V。经过预处理电路后将产生高达12 V的信号,这是模数转换芯片所不能承受的,因此在最后加了钳位二极管保护电路,使信号保持在一个安全的范围内。

Figure 3. Top module

图3. 顶层模块

Figure 4. Result of simulation

图4. 时序仿真波形

Table 2. Setup time slack

表2. 建立时间余量

实验前期用设定亮度的激光照射,发现CCD信号幅值将随扫描频率的提高而减小,当扫描频率为10 MHz时信号幅值几乎为零。从CCD的原理可知,CCD的输出信号大小与光亮度和曝光时间的乘积呈正比。CCD激光位移传感器中CCD接收的是漫反射的弱光,而随着扫描频率提高,像元每次曝光的时间缩短,导致光积分阶段产生的电荷量减少,最终使CCD信号幅值减小。为了克服这一问题,有三种解决办法:第一种是增强激光亮度,即当扫描频率提高时适当地增强激光二极管的功率;第二种是增加曝光时间,即当扫描频率提高时适当地增加两SH高电平之间的光积分时间;第三种是从硬件上改进,在CCD信号预处理电路和模数转换器之间增加一个程控放大器,对不同的扫描频率选择不同的放大倍数。本设计选择了硬件改进的方法,用−3 dB带宽达100 MHz的程控放大器THS7001对信号进行选择性放大,以获得合适幅值的CCD信号。由于TCD1703C的OS引脚输出阻抗高达1 KΩ,所以THS7001的第一级普通放大器部分接成缓冲器结构以获取足够的原始信号。THS7001的第二级程控放大器部分接成反相放大结构,有−22 dB~20 dB之间的8种放大倍数可供选择,在四种扫描频率下分别设置四种不同的放大倍数。THS7001的输出信号由AD8065进行进一步同相放大,放大倍数设置为5。AD8065的−3 dB带宽达145 MHz,并且由于AD8065支持轨至轨输出,因此最终信号的最低电压能达到地电平,适合模数转换。图5所示为硬件电路图。

5. 实验验证

最后,为了验证本设计的合理性,按图1的原理搭建了测试系统。测试过程中,由5 mW激光头产生的激光束照射到被测物表面,其漫反射回来的光被光学系统聚焦后投射到CCD上。

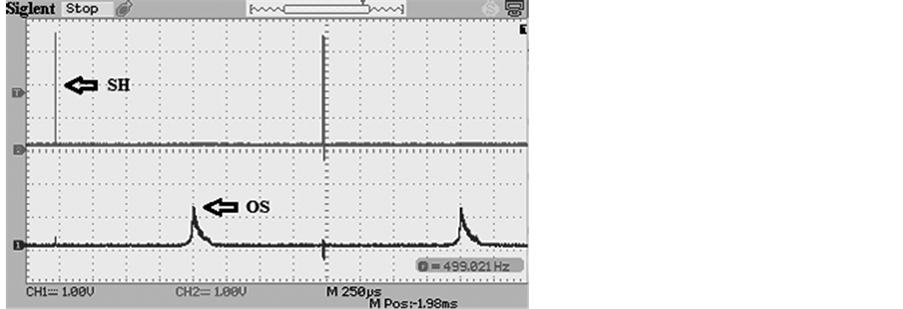

图6是通过示波器获得的CCD输出信号,扫描频率为2 MHz。两个SH高电平分别代表CCD的第一个像元位置和最后一个像元位置。OS信号幅值1.3 V左右,可以明显见到信号的波峰,其顶点就代表了CCD接收到的激光光点中心位置。经过后续模数转换等处理后得到该峰值点对应的位置,再通过数学运算就能得到被测物的距离。

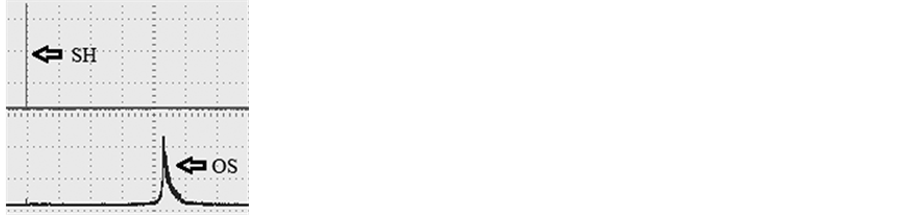

图7为1 MHz扫描频率和10 MHz扫描频率的输出对比。可以发现10 MHz时信号波峰更尖锐,这是因为10 MHz时OS信号衰减严重,波峰中较宽的下面部分湮灭在噪声中,程控放大器选择更大的放大倍数才使其获得与1 MHz时相同的幅值。然而在激光位移传感器中,这一现象并不会影响测量结果,只

Figure 5. Hardware circuit

图5. 硬件电路图

Figure 6. Output of 2 MHz scanning frequency condition

图6. 2 MHz扫描频率的输出信号

Figure 7. Comparison of 1 MHz and 10 MHz scanning frequency condition

图7. 1 MHz和10 MHz扫描频率的输出信号对比

是主机要处理的数据量可能会有所差别。

6. 结语

本文提出了一种用于激光位移传感器中的线阵CCD驱动方法,并根据理论和 前期实验数据进行优化设计。主要解决了传统CCD驱动方法无法连续切换扫描频率并且扫描频率普遍偏低的问题。实验结果表明该方法能在1 MHz、2 MHz、5 MHz和10 MHz扫描频率间切换并且都能正常驱动TCD1703C,输出信号符合激光位移传感器的需求。目前该设计已经应用于一种激光位移传感器的研制中。

基金项目

国防科工局技术基础“十二五”科研项目(J102013B003)。

文章引用

袁敏杰,陈 骥, (2015) 激光位移传感器中线阵CCD驱动方法的设计

Design of Driving Linear CCD in Laser Displacement Sensor. 电路与系统,02,23-31. doi: 10.12677/OJCS.2015.42004

参考文献 (References)

- 1. 张忠捷, 韩焱 (2009) 激光位移传感器在零件圆度公差检测中的应用. 硅谷, 15, 21, 54.

- 2. 田小超, 李忠科 (2014) 基于双单片机的线阵CCD驱动及信号处理系统. 现代电子技术, 20, 59-61.

- 3. 郭焱 (2013) 基于CPLD的线阵CCD的驱动电路设计与实现. 电子质量, 10, 13-16, 27.

- 4. 杨少鹏, 高美凤 (2014) 一种高速线阵CCD采集系统的设计. 电子设计工程, 11, 126-129.

- 5. 常丹华 (2001) 基于CPLD技术的CCD驱动时序产生方法. 仪表技术与传感器, 3, 26-28.

- 6. 沙涛, 刘栋铖, 汪海洋, 等 (2013) 基于FPGA的高速CCD工业相机系统设计. 电子器件, 1, 28-32.

- 7. 梁忠望, 曾云, 江晓山, 等 (2010) 高速线阵CCD数据采集电路的设计与研究. 核电子学与探测技术, 5, 661- 665.

- 8. 王世峰, 赵馨, 佟首峰, 等 (2007) CCD输出信号处理电路的研究. 红外与激光工程, 36, 311-313.

- 9. 张智辉, 田地, 杨义先 (2004) 线阵CCD驱动电路设计的几种方法. 仪表技术与传感器, 6, 32-33, 52.

- 10. 黄文林, 杨光永, 胡国清 (2012) 基于CPLD和Verilog的高精度线阵CCD驱动电路设计. 科学技术与工程, 30, 8053-8057.