Open Journal of Circuits and Systems

Vol.

09

No.

02

(

2020

), Article ID:

35999

,

10

pages

10.12677/OJCS.2020.92003

Fast Load Transient Response LDO with Slew Rate Enhancement Circuit

Jinliang Yang1, Tiansheng Li2

1Ganzhou Teachers College, Ganzhou Jiangxi

2HUAWEI Technology Co., Ltd. Chengdu Research Institute, Chengdu Sichuan

Received: May 2nd, 2020; accepted: Jun. 2nd, 2020; published: Jun. 9th, 2020

ABSTRACT

Because of the rapid development of SoC (System on a Chip), the requirements to LDO (Low Dropout Linear Regulator) chip become more and more rigorous. Lower power consumption, fewer peripheral devices, faster response speed, higher conversion efficiency and power supply rejection ratio have become hotspot of LDO chip. In this paper, a large capacitance free LDO is proposed, which uses slew rate enhancement technology and dynamic bias techniques to optimize slew rate of the LDO, so the transient response of the output voltage becomes fast enough when the load current changes.

Keywords:System on a Chip, Low Dropout Linear Regulator, SRE, Fast Load Transient Response

带摆率增强电路的快速负载瞬态响应LDO研究

杨金亮1,李天生2

1赣州师范高等专科学校,江西 赣州

2华为技术有限公司成都研究所,四川 成都

收稿日期:2020年5月2日;录用日期:2020年6月2日;发布日期:2020年6月9日

摘 要

片上系统SoC (System on a Chip)的快速发展,对低压差线性稳压器LDO (Low Dropout Linear Regulator)芯片的性能要求更加苛刻。更低静态功耗、更少外围器件以及更高转换效率和电源抑制比、更快响应速度已经成为LDO芯片的研究热点和发展趋势。提出了一种带有摆率增强电路的快速负载瞬态响应无片外大电容LDO,用摆率增强技术及动态偏置技术来优化LDO的摆率,在负载发生跳变时能够快速响应。

关键词 :片上系统,低压差线性稳压器,摆率增强,快速负载瞬态响应

Copyright © 2020 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

1. 引言

近年来,随着便携式产品的普及和节能环保理念的提出,电源管理芯片发挥着越来越大的作用,广泛应用于计算机网络、无线电通信、工业制造、医疗设备以及生活基础设施等众多领域 [1] [2],然而无论何种电子设备,都需充足的电能为其提供动力,因此电源管理芯片作为电能和电子设备之间的一个桥梁,它担负起对电能的转换、分配以及稳压等作用,这都为电源管理芯片提供了足够的市场空间 [1] [2] [3] [4]。

随着片上系统的发展,手持设备中的系统芯片集成了越来越多的功能,使得对为内部功能模块供电的电源模块的设计要求也越来越高。传统LDO架构已经不能满足SoC的需求 [5] [6] [7],本文提出一种带有摆率增强电路的快速负载瞬态响应无片外大电容LDO,用摆率增强技术及动态偏置技术来优化LDO的摆率,在负载发生跳变时能够快速响应,更适合应用于SoC系统中。

2. 电路架构及工作原理

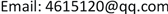

LDO电路架构如图1所示。其中电阻R1~R4及功率管M0、电容C1、误差放大器EA组成主环路,SRE模块为摆率增强电路模块,输出电压发生变化时,该模块会输出一股电流对功率管的栅极进行充电或者放电操作,加快功率管栅极电压的变化,从而提高LDO的负载瞬态响应能力 [1]。另外该SRE电路具有很好的移植性,可以应用于所有其他LDO电路之中。

Figure 1. Fast load transient response without external large capacitance LDO architecture with swing rate enhancement circuit

图1. 带有摆率增强电路的快速负载瞬态响应无片外大电容LDO架构图

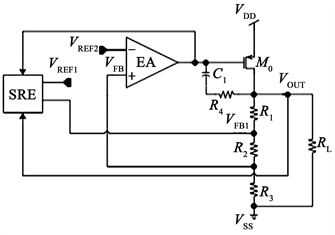

摆率增强电路结构如图2所示。稳态情况下,设置M3电流略大于M4电流,所以M3工作于线性区,M9、M10工作于亚阈值区,因此M10输出电流可忽略,同理,设置M6电流略大于M5电流,所以M6工作于线性区,M7、M8工作于亚阈值区,因此M8电流可忽略,此时M8、M10上均无电流,SRE电路对LDO的主环路静态工作点无影响;当LDO的负载电流突然增大时,由于LDO的输出无储存电荷的负载电容,且LDO摆率的限制功率管栅极电压不能快速降低,因此输出电压会产生较大的下冲电压,此时因C3和R5组成的高通滤波器作用,M3、M5的栅极降低,其电流随之减小,因为VFB1电压为输出电压的分压,所以VFB1电压也降低,通过跨导放大器对基准电压VREF1和VFB1进行比较,使M4的电流增大,当M4电流大于M3电流时,M9有电流流过,且 ,而M6仍工作于线性区,所以M7、M8工作于亚阈值区,M10输出一股功率管栅极到地的电流,加快功率管栅极电压的降低,从而增大功率管的输出电流能力,加快输出电压的调节;相反,当LDO的负载电流突然减小时,LDO的输出电压产生向上的过冲电压,M3、M5电流会瞬间增大,而M4由于跨导放大器的作用电流会减小,因此M9、M10仍工作于亚阈值区,无电流流过,而M7电流为M5电流与M6电流的差值,所以M8输出一股到功率管栅极的电流,加快功率管栅极电压的增大,从而减小功率管的输出电流能力,加快输出电压的恢复,实现快速的负载瞬态响应。

Figure 2. Specific circuit diagram of swing rate enhancement circuit

图2. 摆率增强电路具体电路图

3. 要点分析和具体实现

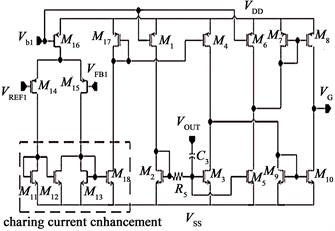

由图2可知,由R5和C3组成的高通滤波器角频率应尽量小,以保证SRE电路能监测到输出电压的跳变,但因R5和C3为片上集成,小的角频率要求大的R5和C3,易造成大的版图面积的浪费。LDO的瞬态响应由摆率和环路带宽共同决定,低频的跳变电压可以通过LDO本身环路进行调节,而高频的跳变电压信号可通过LDO提高摆率进行调节。所以在设计该高通滤波器角频率时存在一个折中关系,保证最小的版图面积下,具有最好的瞬态响应能力。因此在设计时,高通滤波器的角频率与LDO的带宽存在部分交叠,如图3所示,似于扩展了LDO的环路带宽,从而提高LDO瞬态响应的能力。类似于扩展了LDO的环路带宽,从而提高LDO瞬态响应的能力。

Figure 3. Relation between angular frequency and loop bandwidth of high pass filter

图3. 高通滤波器角频率与环路带宽关系图

另外在设计由M11~M18组成的跨导放大器中,为了得到输出电压跳变时M17具有更大的电流变化,跨导放大器反相输入端未使用与运算放大器相同的VFB电压,而是通过分压网络重新得到的一个较高电压,这是由于反馈电压为输出电压的分压,且:

(1)

(1)

由式(1)可看出,R2和R3越大所产生的反馈电压也变化越大,这样通过跨导放大器放大后M17才能具有更大的电流,但为了保证M11~M18所构成的跨导放大器具有合适的共模输入范围,VFB1并没有选择直接使用VOUT,而是跨导放大器最大的共模输入电压值。此外,M11~M13和M18组成跨导电流增强电路,为便于说明,设跨导放大器中M16提供的尾电流为I,M11~M13的宽长比比例为(n + 1):n:1。在稳定情况下差分对M14、M15上电流相等,则流过M11~M13的电流分别为 、 、 ;当LDO输出电流从重载突变到轻载时,输出电压会产生向上的过冲,此时VFB1电压突然变大,假设M14电流变大为原来的1.5倍,则M15电流变小为原来的0.5倍,流过M13的电流减小为原来的 ,因此,相比于不带有跨导电流增强电路的跨导放大器而言,该跨导放大器的跨导变大了原来的n + 1倍;同理输出电流从轻载突变到重载时,输出电压VOUT会产生向下的过冲,此时VFB1电压突然减小,通过分析可得跨导仍增大了原来的n + 1倍。

为保证SRE模块不对LDO主环路静态工作点产生影响,在设计过程中必须保证稳态时M8和M10上无电流流过,这就要求设计过程中设置M3电流要大于M4,M6电流要大于M5,这样才能使M7~M10工作于关断状态。但如果其电流差值较大,在负载发生跳变时,需要一段时间才能使M8或者M10上有电流产生,LDO将不能快速响应负载的瞬态变化,所以在设计过程中需要对该点进行折中,在保证较大电流差值的同时,保证负载瞬态响应的速度足够快。

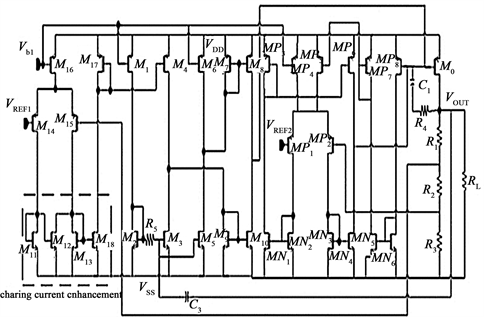

具有快速负载瞬态响应的无片外电容LDO整体电路如图4所示,其中MP1~MP7及MN1~MN5构成该LDO的误差放大器,VREF1和VREF2为基准电压VREF的分压,MP5、MP7、MP8、MN5、MN6组成自适应动态偏置电路,该部分可以在重载时提高误差放大器的尾电流,从而增大LDO的瞬态响应能力。为了降低功耗,在轻载下该部分支路无电流流过,重载时该电流也不应过大,否则会造成误差放大器电压增益过低,LDO的输出精度不够,设计过程中需要对该点进行折中考虑。

Figure 4. Overall circuit diagram of off-chip capacitive LDO for fast load transient response

图4. 快速负载瞬态响应的无片外电容LDO整体电路图

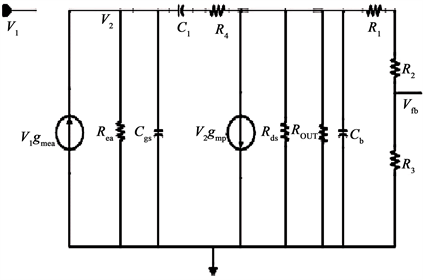

4. 稳定性分析

LDO由两级放大器构成环路,其中第一级为MP1~MP6及MN1~MN4构成的误差放大器EA,第二级为由功率管及输出电阻构成的功率管级,他们连同由R1~R3组成的反馈网络构成LDO的主环路。为了实现该LDO的稳定性,该LDO采用密勒补偿的方法,将主极点设置在功率管的栅极,并且采用调零电阻对环路相位裕度进行优化,从而实现环路高带宽。该环路的小信号等效电路如图5所示。

Figure 5. Small external capacitance LDO signal equivalent circuit with fast load transient response

图5. 快速负载瞬态响应的无片外电容LDO小信号等效电路

其中gmea和gmp分别为误差放大器和功率管的跨导,Cb为LDO输出端寄生电容,v1为断环后所加的测试信号。计算中忽略高频的零极点,则环路传递函数为:

(2)

其中RO_ALL为输出节点总的阻抗大小,F为反馈网络的反馈系数,且

;

(3)

;

(3)

由式(2)可知,环路中有两个低频极点,一个低频零点,低频极点位置分别为:

, (4)

(4)

低频零点位置为:

(5)

通过密勒补偿技术,主极点p1位于功率管的栅极,次级点p2位于输出端,当输出负载电阻较大时,次级点p2向低频方向移动,为了保证环路的稳定性,调零电阻R4产生的零点对LDO的输出极点进行补偿,从而实现环路全负载范围内稳定。由于输出电容较小,负载电阻过大时,输出极点p2会在环路带宽以内,导致环路不稳,所以一般无片外电容LDO具有一个最小的负载,本设计最小负载为100 μA。摆率增强电路SRE的加入,在瞬态时会影响LDO的环路稳定性,针对摆率增强电路,在输出电压发生跳变时,RC高通滤波器仅在高频时有作用;而跨导放大器在低频和高频时均会有作用,且当摆率增强电路开始有电流输出时,LDO环路跨导增大,因此对于瞬态情况下电路稳定性的分析是必不可少的。由于LDO

的带宽为 ,所以,在摆率增强电路开始工作时,由于摆率增强电路参与输出电压的调节,会

增大LDO的带宽,在轻载跳重载时,由于ROUT变小,次极点位置比较高,在摆率增强电路工作时,稳定性没有问题,因此此时可以使RC高通滤波器与跨导放大器均起作用;但在重载跳变轻载时,ROUT变大,次极点位置较低,可能造成环路不稳定,由于在重载跳变轻载时上拉电流随输出电压变化幅度的增大而增大,没有摆率的限制,所以即使跨导放大器不参与调节,通过RC高通滤波器也能够快速的调整LDO的输出电压,提高响应速度,因此为了得到更为稳定的系统环路稳定性,未将M6的栅极连接到M17的栅极,这样可以保证负载跳变时系统不发生震荡。

5. 仿真与分析

快速负载瞬态响应LDO采用中芯国际SMIC 0.35 μm CMOS工艺进行仿真验证,其输入电压范围为2.7 V~3.3 V,最小负载电流100 μA,最大负载电流100 mA,输出电压2.5 V。

5.1. 直流特性仿真与分析

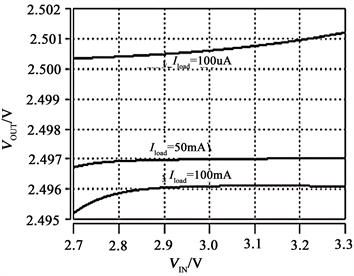

图6为快速负载瞬态响应LDO的线性调整率仿真波形图。电源电压在2.7 V~3.3 V之间变化时,无论是重载100 mA,还是轻载100 μA,LDO的输出电压维持在2.5 V左右,输出电压随电源电压的变化较小,重载时输出电压变化最大,变化了1 mV。负载电流分别为100 μA、50 mA、100 mA时,输出电压的变化大小分别为1 mV、0.5 mV、1 mV,根据线性调整率计算公式可得不同负载下线性调整率分别为0.67 mV/V、0.34 mV/V、0.67 mV/V。另外,100 mA时输出电压误差较大,与2.5 V输出电压相差5 mA左右,这主要是功率级增益减小,使环路增益变小,所以与标准的2.5 V输出电压相差较多。

Figure 6. Simulation wave map of linear adjustment rate of fast load transient response LDO

图6. 快速负载瞬态响应LDO的线性调整率仿真波形图

图7为该快速负载瞬态响应LDO的负载调整率仿真波形图。与LDO的线性调整率类似,当负载电流发生变化时,输出电压的变化量较小。在不同的电源电压下,随着负载电流的增大,输出电压与标准输出值误差变大,这是由于功率管级的输出电阻减小,该级增益也减小,从而导致环路增益的降低,因此造成输出电压误差逐渐增大。从轻载100 μA变化到重载100 mA过程中输出电压最大变化5 mV。在不同的电源电压2.7 V、3 V、3.3 V下,该LDO的输出电压变化分别为5 mV、4 mV、4 mV,因此由负载调整率公式可得,负载调整率分别为0.02 V/V × A、0.016 V/V × A、0.016 V/V × A。

设计过程中为提高LDO的效率,除动态偏置电路外,各条支路电流均较小,最大电流支路电流为4μA,通过仿真得到轻载情况下的静态电流大小为32 μA,可以实现低功耗的特点。

Figure 7. Simulation wave map of load adjustment rate of fast load transient response LDO

图7. 快速负载瞬态响应LDO的负载调整率仿真波形图

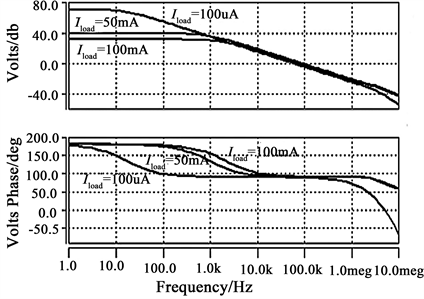

5.2. 交流特性仿真与分析

为保证LDO能够在各种外界噪声干扰情况下正常工作,环路稳定性仿真是必不可少的工作。图8为不同负载情况下所设计快速负载瞬态响应LDO的主环路的幅频和相频特性曲线,其中电源电压为2.7 V,为了模拟输出寄生等效应,仿真时输出端加100 pf电容。从图8可知,在轻载100 μA、中等负载50 mA及重载100 mA三种情况下,环路具有带宽GBW均为80 KHz,而相位裕度90˚。另外,不同负载下主极点位置有所不同,这是由于随着输出电流的变大,输出电阻变小,功率级增益减小,则密勒电容在功率管的栅极等效电容变小,从而使主极点位置右移;而次级点为LDO的输出,可以看到随着负载电阻的变大,次级点位置向左移动,在瞬态时该环路增益会变大,稳定性变差,所以在设计过程中次级点远大于LDO环路带宽GBW。

Figure 8. Spectrum frequency and phase frequency characteristic curves of fast load transient response LDO under different load conditions

图8. 不同负载下快速负载瞬态响应LDO的幅频和相频特性曲线图

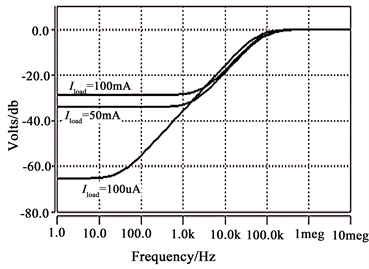

图9为LDO在不同负载下的PSRR仿真结果,其中电源电压为3 V。从图9可知,负载电阻越小,LDO的低频PSRR越差,这是由于环路增益随着负载电阻的减小而减小,由前文的分析知PSRR也会随之变差。另外随着频率升高,LDO的PSRR逐渐变差,这是由于该LDO过了主极点后环路增益20 db/dec下降,所以PSRR 20 db/dec增加。另外由于电源端和输出电压端寄生电容的作用,使得在高频出,电源电压上的纹波能够全部耦合到LDO的输出,所以高频处该LDO的PSRR近似为0。

Figure 9. PSRR simulation curve of fast load transient response LDO under different loads

图9. 不同负载下快速负载瞬态响应LDO的PSRR仿真曲线图

5.3. 瞬态特性仿真与分析

瞬态特性是本设计关注的重点。图10为LDO的在不同负载情况下线性瞬态响应能力。从图10可以看到,在轻载100 μA、中等负载50 mA及重载100 mA三种负载电流情况下,输入电压VIN在2.5 V与3.3 V电压间进行跳变,跳变时间为0.5 μS,LDO的输出电压均变化较小,最大下冲电压为40 mV,最大上冲电压为90 mV,并且恢复时间均在10 μS以内。

Figure 10. Linear transient simulation of rapid-load transient response to LDO under different loads

图10. 不同负载下快速负载瞬态响应LDO的线性瞬态仿真曲线图

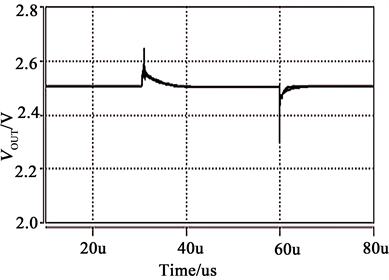

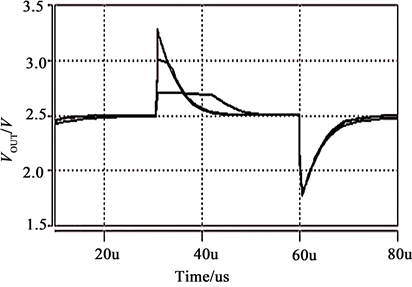

图11为负载瞬态响应曲线图,在不同电源电压2.7 V、3 V、3.3 V下,0.5 μS内负载电流在轻载100 μA与重载100 mA之间进行跳变时,在2.7 V情况下最大下冲电压为200 mV,而在3 V、3.3 V情况下,最大下冲电压为150 mV,恢复时间均在2 μS之内;而在三种不同电源电压下最大上冲电压为150 mV,但是恢复时间较长,约8 μS,这是由于输出电压上冲后,由于负载电流为100 μA,此时输出电容上电荷只能通过负载电流,因此上冲恢复时间较下冲时间长。

Figure 11. Load transient simulation curve of fast load transient response to LDO under different power supply voltage

图11. 不同电源电压下快速负载瞬态响应LDO的负载瞬态仿真曲线图

为了更进一步的说明所设计摆率增强电路及动态偏置电路的作用,设计去掉摆率增强电路及动态偏置电路后的LDO负载瞬态响应曲线(图12),从图12可知,电压上冲或者下冲均较大,且恢复时间也较长,从而可知所设计的LDO具有较好的瞬态响应能力。

Figure 12. Load transient simulation curve of different power supply voltage-free rate enhancement circuits and dynamic bias circuits LDO

图12. 不同电源电压无摆率增强电路及动态偏置电路LDO的负载瞬态仿真曲线图

6. 结论

本文提出了一种带有摆率增强电路的快速负载瞬态响应无片外大电容LDO。该LDO在通过采用摆率增强电路与动态偏置电路来改善LDO负载瞬态变化时的摆率,从而加快功率管栅极的电压的变化,使功率管输出相应的电流,从而调整输出电压到稳定值。与传统无摆率增强电路和自动偏置电路的LDO相比,该LDO的输出电压最大上冲电压均在150 mV左右,而最大下冲电压有所变化,在2.7 V时为200 mV,在3 V、3.3 V时为150 mV,其恢复时间都非常快,很好地优化了无片外电容LDO的负载瞬态响应问题。

文章引用

杨金亮,李天生. 带摆率增强电路的快速负载瞬态响应LDO研究

Fast Load Transient Response LDO with Slew Rate Enhancement Circuit[J]. 电路与系统, 2020, 09(02): 18-27. https://doi.org/10.12677/OJCS.2020.92003

参考文献

- 1. 葛瑞. 低过冲电压LDO线性稳压器的设计和研究[D]: [硕士学位论文]. 成都: 电子科技大学, 2012: 1-5.

- 2. 范东风. 高性能LDO线性稳压器的设计[D]: [硕士学位论文]. 大连: 大连理工大学, 2008: 1-3.

- 3. 马勋. LDO线性降压变换器的研究[D]: [硕士学位论文]. 成都: 电子科技大学,2004: 1-5.

- 4. 王忆. 高性能低压差线性稳压器研究与设计[D]: [博士学位论文]. 杭州: 浙江大学, 2010: 1-2.

- 5. Lau, S.K., Mok, P.K.T. and Leung, K.N. (2007) A Low-Dropout Regulator for SoC with Q-Reduction. IEEE Journal of Solid-State Circuits, 42, 658-664. https://doi.org/10.1109/jssc.2006.891496

- 6. Man, T.Y., Leung, K.N., Leung, C.Y., et al. (2008) Development of Single-Transistor-Control LDO Based on Flipped Voltage Follower for SoC. IEEE Transactions on Circuits and Sys-tems I: Regular Papers, 55, 1392-1401. https://doi.org/10.1109/tcsi.2008.916568

- 7. Hazucha, P., Karnik, T., Bloechel, B.A., et al. (2005) Area-Efficient Linear Regulator with Ultra-Fast Load Regulation. IEEE Journal of Solid-State Circuits, 40, 933-940. https://doi.org/10.1109/jssc.2004.842831