Journal of Sensor Technology and Application

Vol.04 No.02(2016), Article ID:17448,7

pages

10.12677/JSTA.2016.42010

Study and Design of Fast Synchronization in Phase Based on FPGA

Zhi Wang, Gongming Zheng*

Electronics & Information School, Yangtze University, Jingzhou Hubei

Received: Apr. 9th, 2016; accepted: Apr. 24th, 2016; published: Apr. 27th, 2016

Copyright © 2016 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

To achieve signal synchronization in synchronism system, an algorithm based on FPGA was designed to do it. On the basis of oscillator with high precision and temperature offset, further, the system measures its real-time frequency, then provides system with correctional clock. The utilization of glide average method and Real time monitoring system in algorithm in Verilog make error decrease to 5 ns. The experiment shows that: with the high speed of FPGA and the high precision of crystal oscillator, the algorithm makes signal synchronization quickly as well as accurately. The algorithm is applied to BeiDou and GPS synchronized clock system successfully.

Keywords:Signal Synchronization, Digital Phase-Shift, High Precision

基于FPGA的相位同步快速算法研究与设计

王智,郑恭明*

长江大学电子信息学院,湖北 荆州

收稿日期:2016年4月9日;录用日期:2016年4月24日;发布日期:2016年4月27日

摘 要

为实现同步系统中的信号相位同步,设计了一种基于FPGA的相位同步快速算法。在恒温晶振高精度低温漂的基础上,进一步实时测量恒温晶振频率,矫正后提供系统时钟,采用Verilog语言,算法中利用输入信号实时监听系统,使用的滑动平均滤波法,进一步使误差降低到5 ns。实验结果表明:结合FPGA的高速度,恒温晶振的高精度,该算法可以快速的精确的实现信号快速同步。此算法已在北斗/GPS授时同步系统中应用成功。

关键词 :信号同步,数字移相,高精度

1. 引言

目前,相位同步技术已广泛应用于导航定位,电力,高精度时间同步系统等领域。当今,相位同步的技术普遍存在软化程度低,移植性低,成本高等问题 [1] - [3] 。目前实现相位同步相对先进的技术有锁相环技术 [4] 、基于精密时间数字转换器、复杂可编程逻辑电路和硅延迟线技术的精密秒脉冲同步 [5] 。这两种技术实现的同步,依赖硬件电路,且误差均超过100 ns。采用的锁相技术设计的同步电路虽然精度高,但设计的电路复杂。方法二中,当相位差低于硅延迟线DS1023的分辨率或者相位差过大时,DS1023调节的延迟步进量,不能满足延迟要求。由于相位差的值是由输入信号决定,随机。DS1023调节的延迟步进量会产生量化误差,导致误差增大。电路复杂,成本高。为避免这些问题,满足信号相位同步的高速度高精度要求,本算法中剔除误差产生的伪信号和使用校频的恒温晶振提供系统时钟信号,在鉴相器中测量相位差,通过相位调整器,调整初始相位。结合FPGA的高速度,可以高精度高速度同步信号。本算法无外部硬件干扰,成本低,算法可靠,移植性好。

2. 算法设计

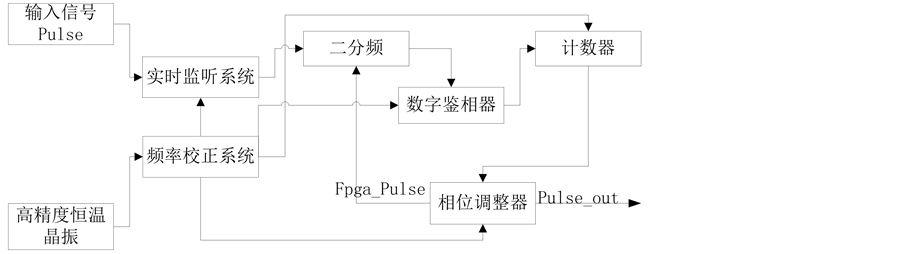

算法原理如图所示(见图1):算法中主要由输入信号实时监听和系统时钟校正模块,数字鉴相器模块,信号同步模块组成。输入为周期秒脉冲信号Pulse,信号实时监听系统对该输入信号进行监听,分析判断,一旦检测伪信号,则剔除该信号。频率校正系统通过不断校正恒温晶振频率,提供稳定精确的系统时钟信号。Pulse和Fpga_Pulse经过分频器产生占空比为50%的周期2S的信号。分频信号在数字鉴相器中,得出相位关系,并通过计数器测量相位偏差。在相位调整器中对Fpga_Pulse脉冲信号不断进行相位调整,经过数字鉴相器后,输出同步信号Pulse_out。

3. 实现原理

3.1. 实时监听系统

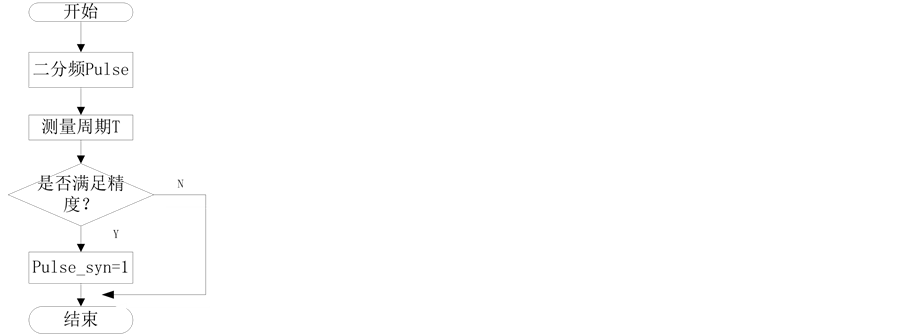

在工程应用中,信号会受到各种电磁干扰,所以同步信号之前,必须保证信号的质量;这些干扰会使脉冲信号产生跳变,从而无效。在大量统计的意义下,计数值的偏差近似服从正态分布,算法中采用滤波的门限值为5,也就是当计数值偏差大于5,识别输入的脉冲为伪脉冲,舍弃不用,并且后面算法中涉及到该信号的算法在下一个时钟时,相关变量全部清零。程序设计流程图如图2所示。

Figure 1. System flow chart

图1. 系统流程图

Figure 2. Input signal monitoring system

图2. 输入信号监听系统

3.2. 系统时钟的校正

算法中输入信号质量检测,相位差的测量,初始相位调整均是以系统时钟为标准,因此对恒温晶振的稳定与准确要求十分高。为保证整个算法的精确性和稳定性,需要对恒温晶振的频率的进行测量和校正 [6] 。

用Pulse秒脉冲提供测频率的门信号,长度为T。分别在t1,t2时刻对门信号内的频率进行测量,根据频率精确度公式得:

(1)

(1)

根据准确度,即可求出真实频率 。

。

测量 的过程中,计数器的量化误差比被测量频率标准的准确度高以一个数量级。已知晶振的较频准确度是10−10,即量化误差Δα = 10−11,求出恒温晶振频率测量中T的取值:

的过程中,计数器的量化误差比被测量频率标准的准确度高以一个数量级。已知晶振的较频准确度是10−10,即量化误差Δα = 10−11,求出恒温晶振频率测量中T的取值:

(2)

(2)

3.3. 数字鉴相原理

当周期脉冲信号Pulse为真信号时,周期脉冲信号的二分频信号Pulse_div与Fpga-Pulse_div相异或后,得出相位差对应的高电平门信号,异或门信号内,若Fpga_Pulse为高电平,则判断出Fpga_Pulse超前周期脉冲Pulse信号。反之,Fpga_Pulse滞后周期脉冲Pulse信号。在异或门内,记录系统时钟sys_clk的脉冲个数syn_cnt。syn_cnt即为对应的相位偏差。由于测量一个异或门的系统时钟脉冲数,即测量一次周期脉冲Pulse和周期脉冲Pulse的相位差,存在比较大的偏差,为了降低误差,通过计数器1测量连续8个异或门的系统时钟脉冲数,再以平均8次的计数值作为相位偏差,滑动平均法可以减小偶然误差,提高精度。在测量过程中,一旦出现伪周期脉冲Pulse信号,则清零系统时钟脉冲计数值和sum_syn_cnt和异或次数average_cnt,确保数据有效性。把测量的相位偏差syn_cnt送至相位调整器时,同时存在一个对其清零过程。由于FPGA的高速度,verilog语言并行处理语句的特点,容易出现先清零后送出去的问题,所以,在算法中设计另一个计数器2计数clear_syn_cnt,在异或门低时,先等待5个脉冲,把syn_cnt送出去后,清零。此计数器2可以提高算法的稳定性,精度。

3.4. Fpga_Pulse相位调整

鉴相器中分析相位关系原理如下,在周期脉冲Pulse信号为真信号时,对于周期脉冲Pulse信号与Fpga_Pulse信号关系,超前或滞后进行判断,从而采取不同算法,得出精确的相位调整值Cnt_shift。通过相位偏差调整Fpga_Pulse的初始相位,使其与周期脉冲Pulse的初始相位更接近,直到到达同步精度误差范围内。f_p_flag为Fpga_Pulse的相位标志,f_p_flag = 1时,Fpga_Pulse滞后于周期脉冲Pulse,反之,则为超前。相位调整值在一个周期内,可以使算法稳定,简单,快速。所以,相位差在一个周期内和超过一个周期时,分别对应不同的算法。整个相位差测量模块和相位调整模块的程序流程图如图3所示。

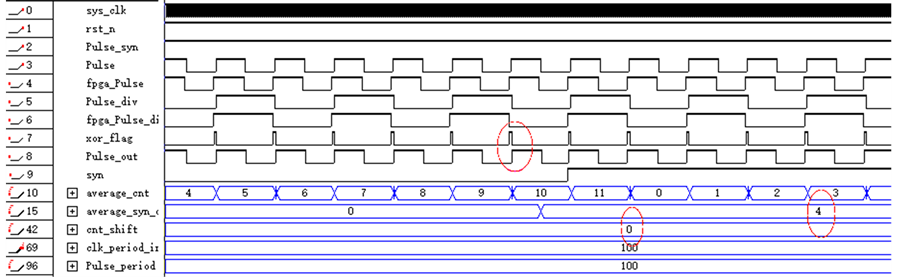

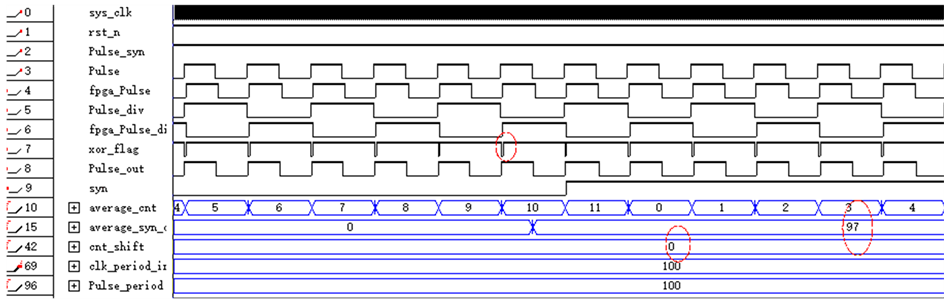

3.5. 信号相位同步

鉴相器中测量的相位偏差反馈至相位调整器中,调整Fpga_Pulse的上升沿,在允许误差范围内,xor_flag == 1或者xor_flag == 0时,即说明了周期脉冲Pulse与Fpga_Pulse同步。经过数据统计,允许误差为5个脉冲之内,即可视为二者信号同步。仿真如图4,图5所示。

4. 系统实现

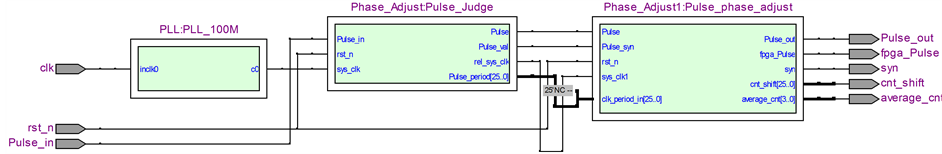

根据以上原理,选用ALTERA生产的Cyclone 2 EP2C35F672C6芯片,结合Verilog语言 [7] ,设计该系统。系统分为3个模块:输入信号实时监听和系统时钟校正模块,相位差测量模块,信号同步模块。对输入信号的实时监听和对系统时钟的校正在Pulse_Judge模块中实现。对输入信号Pulse_in实时频率测量,对测量的频率结果分析,一旦检听到输入信号误差超过5 ns。即判断为伪信号,输出的Pulse,Pulse_val,Pulse_period全部清零,达到无累积误差,提高算法的精度。同时,以输入的秒脉冲信号为时间标准,对恒温晶振的频率进行测量,校正。输出稳定,高精度的系统时钟信号rel_sys_clk。Pulse_phase_adjust是本算法的核心模块,利用校正的高精度的系统时钟频率,先后进行相位差的测量,初始相位的测量,输出相位同步的信号Pulse_out。见图6。

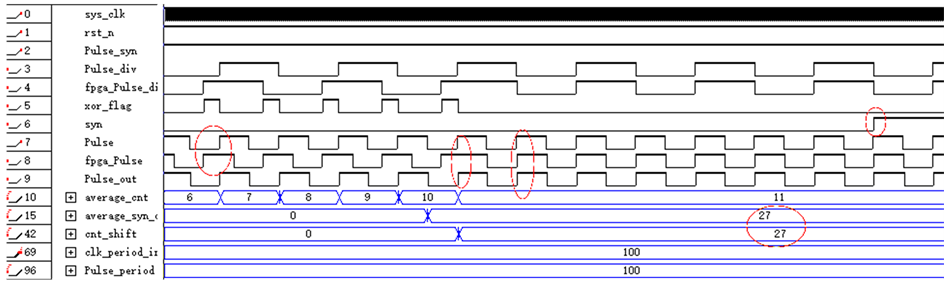

见图7,周期脉冲Pulse滞后于Fpga_Pulse,相位差为27个系统时钟脉冲,小于period100。输出的Fpga_Pulse信号在average_cnt = 10时,相位做出调整,xor_flag = 0、syn = 1,即达到了与周期脉冲Pulse同步。见图8,周期脉冲Pulse超前于Fpga_Pulse,相位差为89个系统时钟脉冲,小于period100。average_cnt = 10时,输出的Fpga_Pulse信号相位做出了调整,xor_flag = 1、syn = 1,达到了与周期脉冲Pulse同步。其他两种情况,即相位差超过period100时,先移到主值周期,再调整相位,实现原理一样。仿真中周期脉冲Pulse信号均为真信号,所以Pulse_out与周期脉冲Pulse始终同步,但是在第十个xor_flag时,Fpga_Pulse信号也与Pulse_out一致。说明若周期脉冲Pulse出现伪信号,Pulse_out即输出的是不断校正同步的Fpga_Pulse信号,从而实现整个算法的功能。

Figure 3. Program flow chart

图3. 软件程序流程图

Figure 4. Synchronization in phase

图4. 相位同步

Figure 5. Synchronization in phase

图5. 相位同步

Figure 6. System architecture of phase synchronization algorithm

图6. 相位同步算法系统结构

Figure 7. Timing simulation of signal phase synchronization

图7. 信号相位同步时序仿真

Figure 8. Timing simulation of signal phase synchronization

图8. 信号相位同步时序仿真

5. 小结

本算法的信号鉴别模块,确保了输出的周期脉冲Pulse的高质量,巧妙使用计数器,去掉了累积误差,保证了数据的精确和数据传输的稳定。利用滑动平均法,降低了周期脉冲Pulse随机波动性对测量结果的干扰,精确测量了二者信号的相位差,并且在FPGA中快速精确的调整了FPGA_Pulse相位,输出同步于周期脉冲Pulse的信号。此算法稳定性高,精确度高,速度快,不仅可以用在同步信号源系统中,而且可以用在其它需要移相的系统中。

基金项目

湖北省大学生创新创业训练计划项目(项目编号:2014011)。

文章引用

王智,郑恭明. 基于FPGA的相位同步快速算法研究与设计

Study and Design of Fast Synchronization in Phase Based on FPGA[J]. 传感器技术与应用, 2016, 04(02): 85-91. http://dx.doi.org/10.12677/JSTA.2016.42010

参考文献 (References)

- 1. 任强, 李尚柏. 基于FPGA的GPS同步时钟装置的设计[J]. 微计算机信息, 2007, 23(3-1): 261-263.

- 2. 郝洪亮, 刘遵义. 基于GPS和FPGA的便携式高精度同步时钟的研制[J]. 电力系统保护与控制, 2009, 37(2): 80-82.

- 3. 徐彦凯, 双凯, 单纪文. 基于FPGA快速位同步的实现[J]. 微计算机信息, 2008, 24(10-2): 173-175.

- 4. 才滢, 崔保健, 赵海鹰. GPS 授时信号同步方法研究与应用[J]. 计测技术, 2013, 33(Z): 62-64.

- 5. 马芸, 郭芃. 基于FPGA延迟时间插入法实现精密时间测量[J]. 现代导航, 2015(5): 317-322.

- 6. 郑恭明, 沈媛媛. 基于FPGA的GPS同步时钟系统设计[J]. 桂林理工大学学报, 2015, 35(1): 198-201.

- 7. Zainalabedin Navabi. Verilog数字系统设计[M]. 李广军, 等, 译. 北京: 电子工业出版社, 2007.

*通讯作者。