Optoelectronics

Vol.06 No.04(2016), Article ID:19140,8

pages

10.12677/OE.2016.64019

Design and Optimization of Resonant Cavity Structure of SOI-Based RCE Photodetectors

Caili Cheng, Qianwen Liu

School of Electric Information, Hangzhou Dianzi University, Hangzhou Zhejiang

Received: Nov. 14th, 2016; accepted: Nov. 28th, 2016; published: Dec. 5th, 2016

Copyright © 2016 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

Due to the functional problems of CMOS photodetectors such as low quantum efficiency, narrow bandwidth and so on, this paper proposed a new resonant cavity structure compatible with SOI CMOS process to fabricate the CMOS photodetector with a higher quantum efficiency based on process optimization. By adopting the SiO2 with the thickness of odd number of a layer of 1/4 wavelength (850 nm optical wavelength) as the bottom DBR mirror, and using the SiO2 mirror with the thickness of an even multiple of 1/4 wavelength as the top DBR mirror, the SOI resonant cavity structure was prepared and demonstrated being suitable for the PD RCE device with the optical communication wavelength of 850 nm. Numerical simulation results showed that the PD RCE device could improve the quantum efficiency effectively compared with the PD CMOS device, which verifies the correctness of the resonant cavity structure.

Keywords:RCE Photodetector, SOI, Resonant Cavity, Quantum Efficiency

SOI基RCE光电探测器谐振腔结构的 设计与优化

程彩莉,刘倩文

杭州电子科技大学电子信息学院,浙江 杭州

收稿日期:2016年11月14日;录用日期:2016年11月28日;发布日期:2016年12月5日

摘 要

由于CMOS光电探测器存在量子效率低、工作带宽窄等性能问题,为实现更高量子效率的CMOS光电探测器,结合工艺实现性,本文构建了一种新型的SOI CMOS工艺可兼容的光电探测器谐振腔结构。基于底镜采用一层1/4波长(850 nm光波长)奇数倍厚度SiO2,顶镜采用1/4波长偶数倍厚度SiO2的DBR反射镜,形成的SOI基谐振腔结构适用于光通信850 nm光波长的RCE PD器件。数值仿真结果表明,RCE PD器件比CMOS PD器件提高了量子效率,验证了谐振腔结构的正确性。

关键词 :RCE光电探测器,SOI,谐振腔,量子效率

1. 引言

随着光电探测器在光通信系统、成像系统及军事等领域的广泛应用,光电探测器件正向着高灵敏度、高性能和高集成度的方向发展。近年来,一系列高性能的PD (Photodetector)结构被研制出来,实现了很高的响应带宽、量子效率等性能 [1] ,其中高性能PD器件结构大多与CMOS (Complementary Metal Oxide Semiconductor)工艺完全不兼容或者只能部分兼容,这严重制约光电探测器的可集成性,为光电集成电路(Opto Electronic Integrated Circuit, OEIC)的发展带来很大的困难。另一方面,光电探测器在高量子效率和高响应速度之间存在相互制约的问题。

谐振腔增强型光电探测器(resonant cavity enhanced photodetector, RCE PD)的出现,为光电探测器在高量子效率和高响应速度方面提供了一条很好的思路 [2] [3] ,它在响应速度快、波长选择性和保证高带宽的基础上可以获得高量子效率等优势。目前,对RCE PD的研究仍是热点之一,且研究成果显著:利用RCE结构的sehottkyPD的3 dB响应带宽已做到100 GHz;Massimo Ghioni等人研制出的基于绝缘体上硅(Silicon-on-insulator, SOI)的谐振腔增强型单光子雪崩探测器(RCE-SPAD),在780 nm共振波长处,其最大探测效率可达可42%,但时间分辨率就不太理想。随着RCE光电探测器的不断发展,其结构更优,性能更好。为了更好的应用谐振腔结构,本文以提高CMOS工艺可兼容的PD的量子效率等性能问题为出发点,提出了将F-P谐振微腔引入到SOI CMOS工艺中,构建一种新型的SOI基CMOS可兼容的谐振腔增强型光电探测器结构,从而为获取高响应速度、高量子效率和波长选择性探测的CMOS可集成光电探测器提供一种新的手段。

2. SOI基光电探测器谐振腔结构

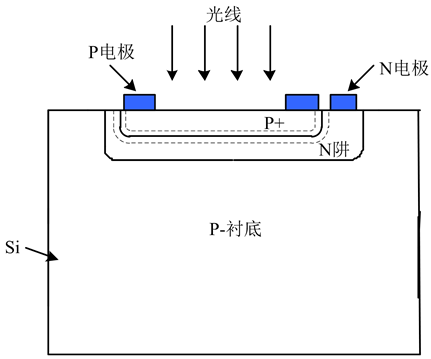

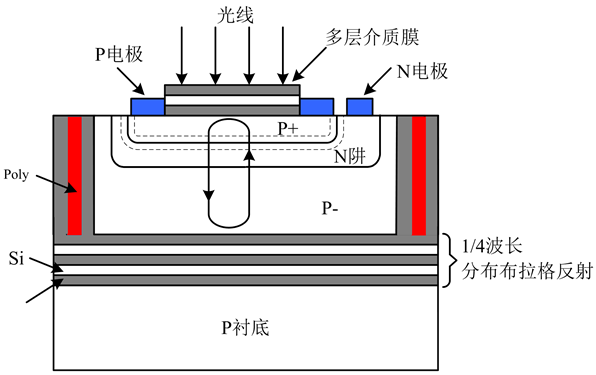

常见的CMOS光电探测器结构如图1所示 [4] 。光从顶层射入,由于PN结耗尽层为光的吸收层,所以利用效率很低。针对这种情况,本文提出了如图2所示的SOI基光电探测器谐振腔结构。谐振腔由反射底镜和反射顶镜构成,反射镜采用DBR (Distributed Bragg Reflector)结构。为更好实现谐振腔和CMOS工艺的兼容性,降低工艺难度和节约成本,选择工艺比较成熟的Si-Air、Si-SiO2多层介质膜体系。

图2中,反射底镜多层介质膜采用SiO2-Si-SiO2多层薄膜来构成,反射顶镜多层介质膜采用SiO2-Si- SiO2多层薄膜构成,这样可以极大保证反射镜与CMOS工艺的兼容性。置于PD两端的上、下DBR反射镜构成了F-P谐振微腔即RCE光电探测器的谐振腔 [5] 。

Figure 1. PD CMOS structure diagram

图1. CMOS PD结构图

Figure 2. PD RCE technology based on CMOS SOI

图2. 基于SOI CMOS工艺的RCE PD

3. DBR结构优化

良好的DBR结构可以有效的提高PD器件性能。DBR反射镜的品质对整个器件的性能有决定性影响,其材料、结构等因素直接决定器件的光谱响应。因此,在DBR的结构优化过程中要考虑反射谱的中心波长与RCE腔的谐振波长是否匹配,以获得合适的反射率保证器件性能。因本文采用的堆栈结构由Si-SiO2

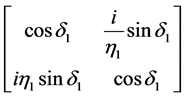

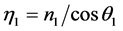

对组成,运用光学传输矩阵法对反射镜的光学特性展开分析研究,矩阵 称为单层膜的特征矩阵,它包含了薄膜的全部有用的参数,其中

称为单层膜的特征矩阵,它包含了薄膜的全部有用的参数,其中 ,

, 。由矩阵表达式可知,当薄膜的有效光学厚度为1/4波长的整数倍时,即

。由矩阵表达式可知,当薄膜的有效光学厚度为1/4波长的整数倍时,即 (

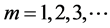

( )在参考波长处会出现极值。对于多层膜的反射率,如公式(1)所示。

)在参考波长处会出现极值。对于多层膜的反射率,如公式(1)所示。

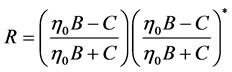

(1)

(1)

式中R为反射率, 为空气折射率,膜系的特征矩阵为

为空气折射率,膜系的特征矩阵为

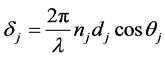

(2)

(2)

(2)式膜层的位相厚度是 ,

, ,矩阵

,矩阵 为第j层膜的

为第j层膜的

特征矩阵(nj是j层膜的折射率)。在对反射镜反射率理论分析的基础上,开展对反射底镜和反射顶镜多层介质膜结构分析,包括SiO2-Si-SiO2薄膜层数、薄膜厚度等数值仿真分析。

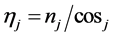

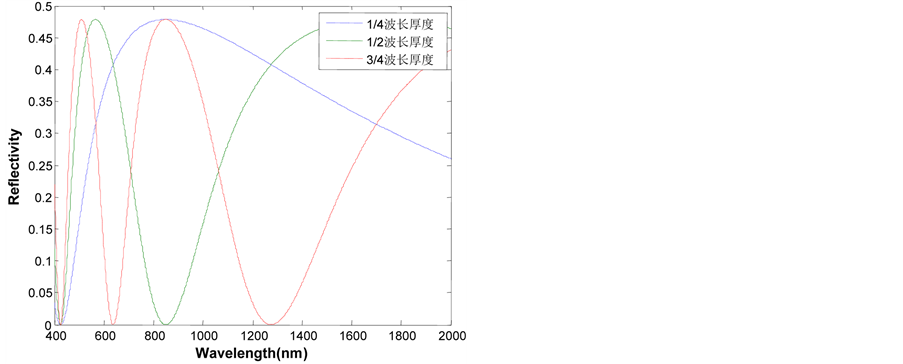

3.1. DBR底镜

图3给出单层SiO2作为底镜的反射率与SiO2厚度的数值仿真结果。随SiO2底镜厚度随1/4波长的倍数增加,底镜反射率在1/4波长奇数倍厚度时取到极大值,1/4波长偶数倍厚度时取到极小值,这与单层介质膜的反射率随其光学厚度的变化关系表现的趋势保持一致,但随SiO2底镜厚度增加,中心波长附近的响应谱变窄。图4给出了多层SiO2-Si作为底镜的反射率与SiO2-Si层数的关系。随Si-SiO2对数的增加,反射镜的反射率增加,同时中心波长附近的响应谱变宽。考虑到在DBR反射镜工艺实现过程中,对生长SiO2和Si层的厚度有严格要求,反射镜的每一层在生长过程中都会存在误差,生长的厚度及层表面均匀性、平整性等都是难以得到精确控制。因此,若顶镜和底镜的Si-SiO2层的对数较多,其将对工艺提出更高的要求才可实现,且误差也会加大。本设计主要考虑如何在SOI工艺基本流程不改变的情况下,通过适当改变一些工艺参数,从而达到适合于SOI CMOS工艺的最优化RCE光电探测器结构。综合考虑,本设计中反射底镜在工艺可实现情况下可选取一对Si-SiO2膜。

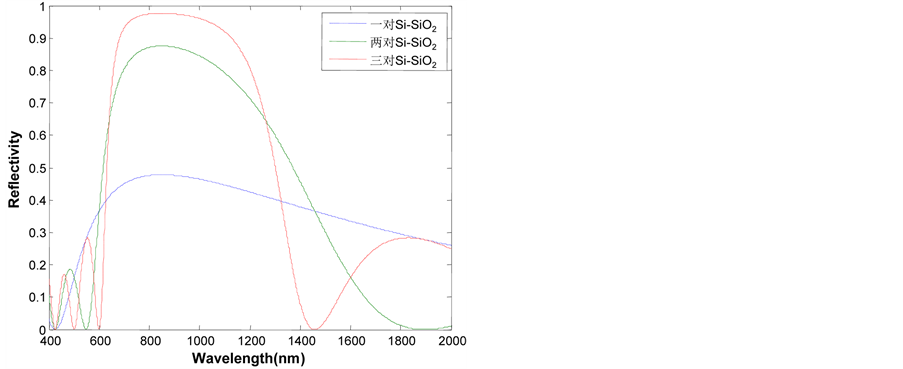

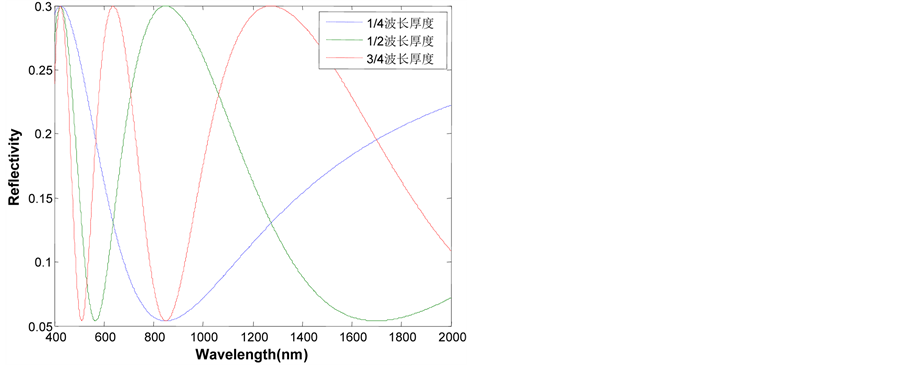

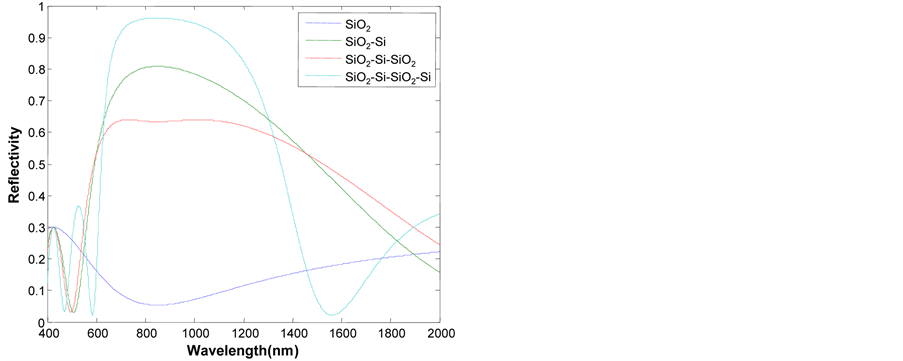

3.2. DBR顶镜

图5给出单层SiO2作顶镜时,顶镜反射率与单层SiO2厚度的关系。从图5中可看出,1/4、1/2和3/4波长厚度的SiO2反射顶镜的反射率分别为5.4% (850 nm光波长)、30.0%和5.4%。随着SiO2顶镜厚度增加,中心波长附近的响应谱变窄了。由于顶镜上面为空气层,当多层SiO2-Si作顶镜时,需考虑多层结构的最上层既可是SiO2也可是Si材料。图6给出了顶镜反射率与SiO2-Si层数的关系,可看出在中心波长为850 nm处,一对SiO2-Si构成的DBR反射镜为80.1%,比单层SiO2的反射率大大提高,而SiO2-Si-SiO2构成的DBR反射镜的反射率下降至63.4%,多层SiO2-Si结构最上层为1/4波长厚度SiO2会对中心波长的反射率起到抑制作用。考虑到入射光要通过顶镜进入谐振腔,顶镜要具有半反半透的特性,因此反射率不能取太高,这里选择一层SiO2作为顶镜,厚度为1/4波长偶数倍厚度,反射率为30.0%。

4. 优化的谐振腔结构

由上节可知,RCE PD中DBR反射镜反射率与各层膜厚度、膜层数等有密切的关系。考虑SOI工艺兼容性,本设计中底镜只能采用一层SiO2,所以厚度为1/4波长奇数倍厚度,反射率为47.8% (在850 nm光波长处);同时选择一层SiO2作为顶镜,厚度为1/4波长偶数倍厚度,反射率为30.0%。该SOI RCE光电探测器的谐振腔示意图如图7所示。

Figure 3. The bottom mirror reflectivity with the thickness of SiO2 single-layer

图3. 底镜反射率与单层SiO2厚度关系

Figure 4. The bottom mirror reflectivity and SiO2-Si logarithmic relationship

图4. 底镜反射率与SiO2-Si对数的关系

Figure 5. The top mirror reflectivity with the thickness of SiO2 single-layer

图5. 顶镜反射率与单层SiO2厚度关系图

Figure 6. The top mirror reflectivity and SiO2-Si layer diagram

图6. 顶镜反射率与SiO2-Si层数的关系图

Figure 7. Resonator structure in CMOS-based CMOS RCE photodetectors

图7. 以CMOS为主的CMOS RCE光电探测器的谐振腔结构

量子效率体现了器件光电转换的效率。可以从以下两点提高量子效率:提高耗尽层的吸收效率(如加入谐振腔结构);增加少子寿命以减少电子空穴对的复合。文中提出了SOI基谐振腔,可以有效的提高耗尽层的吸收效率。通过理论推导和整理,量子效率可表示为

(3)

(3)

(3)式中β为传输常数;φ1、φ2,r1、r2分别为上、下反射镜的反射相移和反射率;L为吸收层厚度。推导过程忽略了薄膜材料折射率的色散问题以及在谐振腔的不同区域折射率及吸收系数的不同。

以普通CMOS光电探测器为分析对象,进行了有/无谐振腔的性能对比。这里硅膜取186.4 nm (3/4个波长),埋氧厚度取140 nm (1/4波长),介质层厚度取280 nm (1/2波长),耗尽层厚度由标准SOI CMOS工艺掺杂注入确定,不做调整,最大可能性的保证工艺兼容性。图8给出了耗尽层宽度0.03 µm时,(SiO2)- (SiO2)谐振腔PD器件量子效率随波长的关系图。

Figure 8. (SiO2)-(SiO2) cavity PD device quantum efficiency with the relationship between the wavelength (depletion layer width 0.03 µm)

图8. (SiO2)-( SiO2)谐振腔PD器件量子效率随波长的关系(耗尽层宽度0.03 µm)

Table 1. Performance comparison of PD CMOS devices with standard PD RCE devices

表1. RCE PD器件与标准CMOS PD器件性能对比

表1给出谐振腔PD器件与标准CMOS PD器件的量子效率对比数据,其中标准CMOS PD器件和谐振腔PD器件的硅膜CMOS加工工艺一致,可认为两者的工作带宽一致。从表中数据分析可得,谐振腔PD器件比CMOS PD器件的量子效率提高了五倍左右,实现了谐振腔PD器件相较于标准CMOS PD器件提高光电探测器量子效率的性能,证明了谐振腔结构的正确性。

5. 结论

本文提出了一种新型的SOI CMOS工艺可兼容的(SiO2)-(SiO2)谐振腔结构。利用不同厚度的SiO2薄膜作为DBR反射镜构建谐振腔结构的物理模型,通过理论仿真计算了其反射率特性和量子效率。在考量工艺实现性的基础上,最终确定器件结构为:底镜采用一层1/4波长(850 nm光波长)奇数倍厚度SiO2,顶镜采用1/4波长偶数倍厚度SiO2,该新型的SOI基谐振腔可用于实现高量子效率的SOI基RCE光电探测器。数值仿真结果表明基于优化DBR结构的RCE PD器件比CMOS PD器件的量子效率提高了五倍左右,验证了谐振腔结构的正确性。

尽管RCE PD比普通PD有优势,但在实际应用中仍有缺陷,主要原因有以下两点:1) 近年研究成果显示,现有的RCE PD已具备高响应度、结构紧凑等特性,但仍有部分特性没有很好体现;2) 高性能RCE光电探测器成本高昂,制作工艺难度比较大,难以实现商业集成化生产。这些问题及挑战构成了RCE光电探测器研究的重点。因此,本文对RCE PD的材料、结构及工艺实现等特性的进一步分析研究具有一定的指导和现实意义。

文章引用

程彩莉,刘倩文. SOI基RCE光电探测器谐振腔结构的设计与优化

Design and Optimization of Resonant Cavity Structure of SOI-Based RCE Photodetectors[J]. 光电子, 2016, 06(04): 131-138. http://dx.doi.org/10.12677/OE.2016.64019

参考文献 (References)

- 1. 江文杰, 曾学文, 施建华. 光电技术[M]. 北京: 科学出版社, 2009: 1-7.

- 2. Li, G., Maekita, K., Mitsuno, H., et al. (2015) Over 10 GHz Lateral Silicon Photodetector Fabricated on Silicon-on- Insulator Substrate by CMOS-Compatible Process. Japanese Journal of Applied Physics, 54. https://doi.org/10.7567/jjap.54.04dg06

- 3. El-Batawy, Y.M. and Medhat, M. (2015) Biasing Dependent Circuit Modeling and Optimization of Resonant Cavity Enhanced PIN Photodetectors (RCE-PIN-PDs). International Symposium on Photonics and Optics, International Society for Optics and Photonics, 9656.

- 4. 陈永权. CMOS兼容光电探测器及接收机模拟研究与设计[D]: [硕士学位论文]. 天津: 天津大学, 2004.

- 5. Knodl, T., Choy, H.K.H., Pan, J.L., King, R., Jager, R., Lullo, G., et al. (1998) RCE Photodetectors Based on VCSEL Structures. IEEE Photonics Technology Letters, 11, 1289-1291. https://doi.org/10.1109/68.789720