Hans Journal of Wireless Communications

Vol.07 No.01(2017), Article ID:19785,8

pages

10.12677/HJWC.2017.71006

The Design and Implementation of Symbol Timing Synchronization Algorithm for MPPSK Digital Receiver

Jun Sha, Lenan Wu

School of Information Science and Engineering, Southeast University, Nanjing Jiangsu

Received: Feb. 4th, 2017; accepted: Feb. 15th, 2017; published: Feb. 23rd, 2017

ABSTRACT

This pager designs a double windows read-time symbol timing synchronization algorithm for the digital receiver of MPPSK modulation communication system. The algorithm is a feedback structure, which consists of timing error detection unit, corrector unit and so on and the timing error is calculated based on the auxiliary data. Compared with the existing symbol timing synchronization algorithm for MPPSK digital receiver, this algorithm has the advantages of short synchronization setup time, independent of impact amplitude and real-time adjustment. Finally we use the system generator development tools of Xilinx FPGA to do design and simulation, and we do hardware co-simulation and verification on MPPSK digital receiver based on Spartan-6 series FPGA design.

Keywords:Efficient Modulation, Symbol Timing Synchronization, Digital Receiver, System Generator, FPGA

MPPSK数字接收机位同步算法设计与实现

沙俊,吴乐南

东南大学信息科学与工程学院,江苏 南京

收稿日期:2017年2月4日;录用日期:2017年2月15日;发布日期:2017年2月23日

摘 要

本文设计了一种用于MPPSK调制通信系统数字接收机的双窗实时位同步算法。该算法是一种反馈结构位同步算法,由定时误差检测单元、校正器等构成,基于数据辅助来计算定时误差。相较于现有的MPPSK接收机位同步算法,该算法具有同步建立时间短、不依赖冲击幅值、实时调整的优点。最后利用FPGA开发环境System Generator系统设计工具进行设计和仿真,并在基于Spartan-6系列FPGA设计的MPPSK数字接收机上进行了硬件协同仿真和验证。

关键词 :高效调制,位同步,数字接收机,System Generator,FPGA

Copyright © 2017 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

1. 引言

随着社会技术和经济的发展,迫切希望能实现多媒体数据高速传输,因而现代通信系统带宽不断增加,随之而来的是无线频谱资源的紧缺。高效调制技术 [1] 能在单位时间内传输更多的信息,同时占用更窄的频带,因此研究高效调制技术具有重大的意义。

位同步 [2] 又称码元同步,是数字通信接收机的重要组成部分。发端的消息是通过一连串码元序列传送的,接收时需要知道每个码元的起始,以便在恰当的时刻进行取样判决。所以接收端必须提供一个位定时脉冲序列,其重复频率与码元速率相同,相位与最佳取样判决时刻一致,提取这种定时脉冲序列的过程称为位同步。

本文首先介绍MPPSK调制与解调原理,再介绍数字接收机中的位同步系统。在分析传统算法后提出双窗实时位同步算法,介绍其实现结构,定时误差 的计算和具体算法的实现流程。最后利用FPGA开发环境System Generator系统设计工具进行设计和仿真,介绍算法的具体Verilog实现,并与数字接收机系统联调,验证算法性能。

的计算和具体算法的实现流程。最后利用FPGA开发环境System Generator系统设计工具进行设计和仿真,介绍算法的具体Verilog实现,并与数字接收机系统联调,验证算法性能。

2. MPPSK系统

2.1. MPPSK调制

多元位置相移键控 [3] (MPPSK:M-ary Position Phase Shift Keying)是一种数字相位调制方式,并通过对于不同符号信息调制出现在载波的不同时间位置来区分不同的码元。经典MPPSK调制在0码元没有跳变,解调端没有幅度冲击,门限选取较为麻烦,文献 [4] 提出了一种改进的MPPSK调制方式,其在一个码元周期[0, NT]中调制波形表达式如下:

(1)

(1)

其中 为载波频率,A,B为载波幅度,

为载波频率,A,B为载波幅度, 为码元周期,

为码元周期, 为调制相位,一个码元周期持续了N个载波周期,其中跳变部分占了K个载波周期。通常取

为调制相位,一个码元周期持续了N个载波周期,其中跳变部分占了K个载波周期。通常取 ,

, 。

。

2.2. MPPSK信号通过冲击滤波器

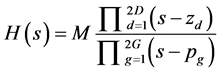

冲击滤波器 [5] 是一类特殊的IIR带通滤波器,由D对共轭零点和G对共轭极点组成,其系统函数如式(2):

(2)

(2)

式中 和

和 分别为冲击滤波器的零点和极点。零点频率低于所有极点频率,而零-极点频率的靠近程度不劣于位于零点频率和极点频率之间的信号载频的

分别为冲击滤波器的零点和极点。零点频率低于所有极点频率,而零-极点频率的靠近程度不劣于位于零点频率和极点频率之间的信号载频的 数量级,从而在其通带内的中心频率处呈现出极窄的陷波-选频特性,使得MPPSK调制信号滤波输出波形在相位跳变处产生明显的寄生调幅冲击,据此可进行同步及判决。

数量级,从而在其通带内的中心频率处呈现出极窄的陷波-选频特性,使得MPPSK调制信号滤波输出波形在相位跳变处产生明显的寄生调幅冲击,据此可进行同步及判决。

文献 [6] 给出了AWGN信道下,EPPSK调制信号通过冲击滤波器后码元0和1的幅度最大值的位置服从广义瑞利分布,其幅值最高点所在区间有明显的区分。推广到MPPSK,对于码元 其经过冲击滤波器之后,码元决定了其幅度最大值所在区间,在此基础上提出了基于位置信息的MPPSK解调方法 [7] 。

其经过冲击滤波器之后,码元决定了其幅度最大值所在区间,在此基础上提出了基于位置信息的MPPSK解调方法 [7] 。

图1是MPPSK调制信号经过模拟冲击滤波器后的信号包络。第一行为MPPSK调制信号,第2行为经过冲击滤波器之后信号,MPPSK信号的相位跳变部分,已经变成了很明显的幅度冲击。

2.3. MPPSK接收机设计

MPPSK调制信号的解调有两种:冲击滤波器 + 积分判决或者抽样判决。文献 [6] 论证了AWGN信道下MPPSK信号的解调性能,所以采用冲击滤波器包络检波和积分判决成了MPPSK调制信号的常用接收结构。图2为MPPSK接收机实现框图,MPPSK调制信号经过冲击滤波器并包络检波后,经由高速AD采样送入全数字接收机。

MPPSK制信号的冲击滤波包络,以满足奈奎斯特采样定理的采样频率 进行采样,采样倍数

进行采样,采样倍数 ,因此一个码元周期内有

,因此一个码元周期内有 个采样点。因此位同步与解调过程是基于一种实时调整的符号判决空间,将冲击幅值最高点记为

个采样点。因此位同步与解调过程是基于一种实时调整的符号判决空间,将冲击幅值最高点记为 ,其理论值满足:

,其理论值满足:

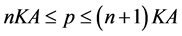

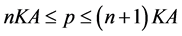

1) 码元的判决区间是指该符号的冲击幅度最高点 的理论取值范围,码元

的理论取值范围,码元 对应的判决区间为

对应的判决区间为 ;

;

Figure 1. MPPSK signal and signal after the impact filter

图1. MPPSK调制信号和经过冲击滤波器之后的信号

Figure 2. Block diagram of digital receiver for MPPSK

图2. MPPSK接收机框图

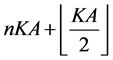

2) 符号的冲击最高点位置 的理论值位于判决区间的中点,码元

的理论值位于判决区间的中点,码元 对应的冲击幅度最高点位置为

对应的冲击幅度最高点位置为 ,其中

,其中 表示向下取整;

表示向下取整;

3) 对于码元n,其冲击幅度最高值 所在区间为

所在区间为 ,理论值为

,理论值为 ,所以连续两个相同码元冲击幅度最高点所在位置

,所以连续两个相同码元冲击幅度最高点所在位置 与

与 之间满足:

之间满足:

(3)

(3)

3. 位同步系统设计

3.1. 位同步结构

数字通信中的位同步结构主要分为两类 [8] :前馈式结构和反馈式结构。位同步其实是一个定时误差 的估计过程,根据误差估计方法的不同,定时误差又可分为数据辅助和非数据辅助法。前馈式全数字位同步结构,所有信号向前流动,这要求定时误差检测能够准确估算

的估计过程,根据误差估计方法的不同,定时误差又可分为数据辅助和非数据辅助法。前馈式全数字位同步结构,所有信号向前流动,这要求定时误差检测能够准确估算 ,并提供给定时校正器进行定时调整。由于前馈结构中没有反馈环路,为了估算出定时误差,需要把输入数据进行分块处理。高速通信系统中数据分块处理是个很复杂的工作。反馈式全数字位同步结构如图3所示,存在一个反馈回路,因此输入信息可以根据定时误差

,并提供给定时校正器进行定时调整。由于前馈结构中没有反馈环路,为了估算出定时误差,需要把输入数据进行分块处理。高速通信系统中数据分块处理是个很复杂的工作。反馈式全数字位同步结构如图3所示,存在一个反馈回路,因此输入信息可以根据定时误差 来进行实时校正,完成闭环的反馈操作。

来进行实时校正,完成闭环的反馈操作。

可以看到在位同步系统中,定时误差 的计算是位同步系统中的重要工作。常用的定时误差检测算法主要有早迟门算法、Mueller&Muller算法、平方律算法和Gardner算法 [9] 。而由于MPPSK调制系统基于位置信息的特殊性,一个码元周期包含了N个载波周期,必须有新的同步算法来确保找到准确的码元开始时刻。因此,本文提出了双窗位同步算法,是一种反馈式的全数字同步,基于数据辅助来计算定时误差

的计算是位同步系统中的重要工作。常用的定时误差检测算法主要有早迟门算法、Mueller&Muller算法、平方律算法和Gardner算法 [9] 。而由于MPPSK调制系统基于位置信息的特殊性,一个码元周期包含了N个载波周期,必须有新的同步算法来确保找到准确的码元开始时刻。因此,本文提出了双窗位同步算法,是一种反馈式的全数字同步,基于数据辅助来计算定时误差 。

。

3.2. 双窗实时位同步算法

所谓双窗位同步算法,就是使用两路相位相差 的位同步信号并行工作,互不影响。使用两路信号的原因是,为了避免同步信号起始时刻正好落在冲击幅度的最大值附近,导致失步现象。使用两路信号,可大大降低失步概率,并缩短同步时间。

的位同步信号并行工作,互不影响。使用两路信号的原因是,为了避免同步信号起始时刻正好落在冲击幅度的最大值附近,导致失步现象。使用两路信号,可大大降低失步概率,并缩短同步时间。

每一路位同步算法是外同步法,外同步法是指在传输信号中插入额外的同步信息。针对MPPSK调制信号的冲击滤波特性,本算法在每帧数据之前添加 个独立的码元“1”。这

个独立的码元“1”。这 个码元经调制、冲击滤波之后其冲击幅度最大值之间间距满足公式(3)。在采样后的冲击信号中,如果连续找到

个码元经调制、冲击滤波之后其冲击幅度最大值之间间距满足公式(3)。在采样后的冲击信号中,如果连续找到 码元满足这样的间距,则说明找到了我们添加的

码元满足这样的间距,则说明找到了我们添加的 个码元“1”,据此求出定时误差

个码元“1”,据此求出定时误差 ,从而确定码元的起始时刻。

,从而确定码元的起始时刻。

算法主要实现步骤如下:

1) 随机生成一路同步信号,其重复频率与码元频率相同,在一个码元周期内有 个采样点。

个采样点。

2) 找到码元周期内采样点的最大值位置 ,与前一窗口的最大值位置

,与前一窗口的最大值位置 比较,如果满足式(3),说明相邻两个码元相同,将计数器加1;否则说明相邻两个码元不同,清零计数器,返回执行2步。

比较,如果满足式(3),说明相邻两个码元相同,将计数器加1;否则说明相邻两个码元不同,清零计数器,返回执行2步。

3) 如果计数器的值不等于收发双发约定的1的个数 ,继续执行步骤2,否则说明已经找到位同步头,可以给出定时误差

,继续执行步骤2,否则说明已经找到位同步头,可以给出定时误差 ,其计算公式如:

,其计算公式如:

(4)

(4)

Figure 3. Block diagram of symbol timing synchronization’s feedback structure

图3. 反馈式全数字位同步结构框图

其中的 为同步头最后一个1在同步窗中的位置,

为同步头最后一个1在同步窗中的位置, 表示向下取整。

表示向下取整。

4) 位同步系统根据该定时误差 将窗口延时相应的采样点,同时输出一个使能信号,让后续的数字解调模块可以开始进行相应的工作。

将窗口延时相应的采样点,同时输出一个使能信号,让后续的数字解调模块可以开始进行相应的工作。

5) 每帧数据的起始时刻,均会执行一次该位同步算法,以实时修正定时误差 ,从而实现了实时位同步,大大减少了失步的概率。

,从而实现了实时位同步,大大减少了失步的概率。

与MPPSK调制系统中常用的数字位同步算法相比,该算法不再依赖冲击幅值,更好地适应了不同信道衰减下的情况;两路同步信号的使用解决了同步信号起始时刻正好落在冲击幅度最大值附近,导致同步系统不工作的问题;而且相比于传统的位同步算法,该算法实现简单,硬件复杂度低,可以实时调整,应用价值高。

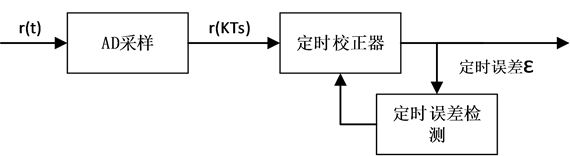

3.3. System Generator硬件仿真

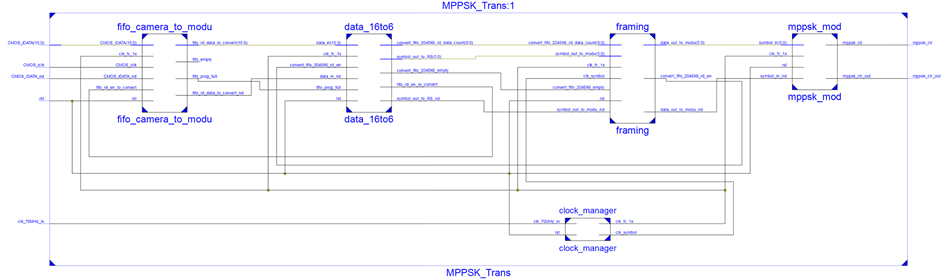

System Generator是Xilinx公司的系统级建模工具,内含Xilinx特有的DSP功能IP,包括基本DSP函数和逻辑算符,例如FIP,FFT、存储器、数学函数、转换器、延时线等,可在Simulink中实现FPGA电路的系统级建模,并自动生成硬件描述语言和Modlsim测试程序,能在Xilinx FPGA上自动实现硬件系统。为了验证上述位同步算法的有效性,我们利用Simulink环境搭建MPPSK通信系统,其设计结构如图4所示。

整个系统 [10] 其实由发射机和接收机组成。发射机用于产生随机码的调制波形;接收机由数字冲击滤波器模块,包络检波模块,位同步模块,数字解调模块组成。

1) 调制模块:传输的信号为M进制的随机码,调制模块;

2) 冲击滤波和包络检波模块:调制信号经过数字冲击滤波器,相位跳变转变为冲击波形,接着进行包络检波(取绝对值再进行低通滤波),送入同步和解调模块;

3) 同步模块:采用3.2所述的双窗位同步算法,求出对应的定时误差 ,实时调整位同步;

,实时调整位同步;

4) 数字解调器:采用文献 [11] 中基于位置信息的解调方案进行解调。

由于实际硬件系统中,冲击滤波和包络检波模块采用模拟方案实现,故该模块均采用simulink模块搭建而成,而同步模块和数字解调器均采用System Generator搭建而成。

单路同步算法利用Verilog实现,其流程为:设置一个计数器作为同步窗,其周期恰好为一个MPPSK码元周期,也就是 ;再设置两个寄存器max_position_in_windows和pre_max_position_in_windows来存放当前窗口的最大值位置和前一窗口的最大值位置。同步窗记满一个周期,就判断两个位寄存器是否满足式(3),如果满足则给同步头计数器sync_symbol_windows加1。当同步头计数器为收发两端约定的值,则同步成功,输出定时误差window0_delay_num反馈给前端,完成位同步,输出一个使能信号judge_start_pos给后续的数字解调电路。

;再设置两个寄存器max_position_in_windows和pre_max_position_in_windows来存放当前窗口的最大值位置和前一窗口的最大值位置。同步窗记满一个周期,就判断两个位寄存器是否满足式(3),如果满足则给同步头计数器sync_symbol_windows加1。当同步头计数器为收发两端约定的值,则同步成功,输出定时误差window0_delay_num反馈给前端,完成位同步,输出一个使能信号judge_start_pos给后续的数字解调电路。

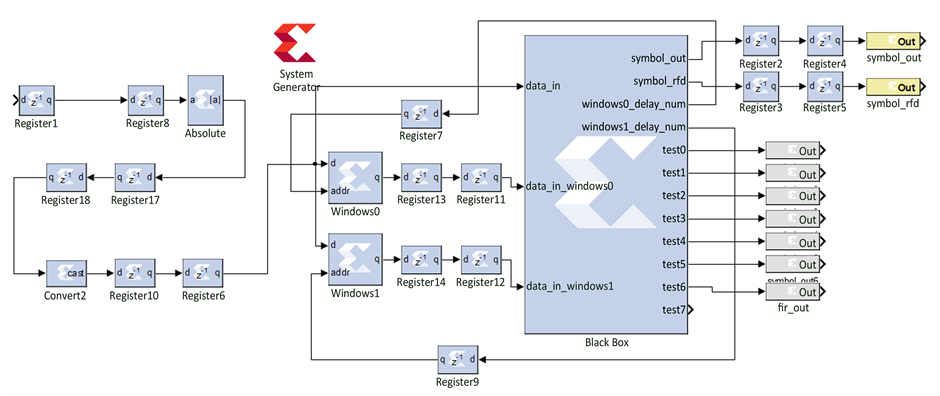

图5反应了位同步的整个过程,第1行为调制信号经冲击滤波器后的波形,第2行和第3行为产生的两路同步信号,第4行为同步头计数器,当其达到预定值3之后,第5行输出一个使能信号,说明位

Figure 4. MPPSK digital receiver structure based on System Generator

图4. 利用System Generator搭建的MPPSK数字接收机

Figure 5. Working process of symbol timing synchronization

图5. 位同步系统工作过程

同步系统正常工作。而同时解调出来的值与发射机发送的值也一致。

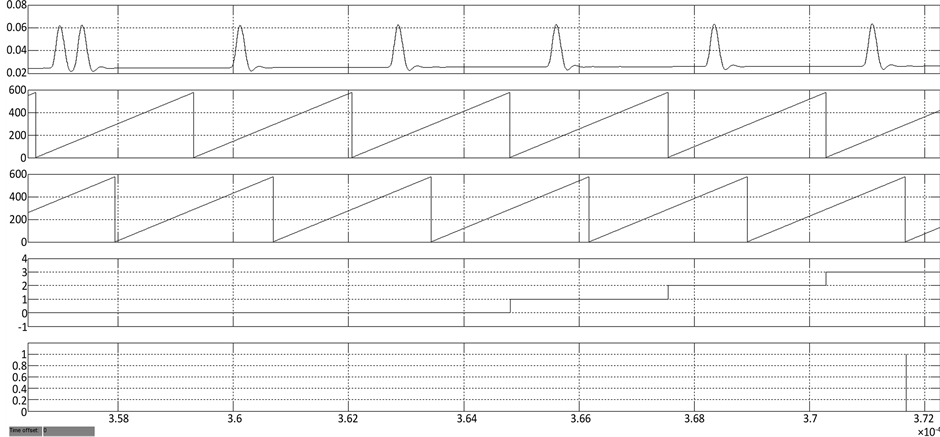

4. FPGA硬件协同仿真

System Generator支持高带宽硬件协同仿真,可以实时地将FPGA内部的信号反馈处理,使得FPGA板级验证更方便。我们已经制作了基于Xilinx的Spartan-6系列FPGA设计的MPSSK系统的发射机及接收机 [10] ,因此可以直接由发射机产生调制信号经信道送至接收机,对位同步系统进行验证。将上述利用System Generator实现的位同步和解调系统产生硬件协同仿真模块,放入设计文件。

本文MPPSK系统采用的参数为:M = 64,位同步头为4个1,帧头采用5 + 7位巴克码,一帧数据有252个码元。数字发射机工作流程为:上位机通过网口芯片W5500 (其内部由TCP/IP协议栈 + MAC + PHY构成,有官方应用库,可以实现10 M/100 M BASE-T)将原始数据传给ARM,ARM将数据送入数字发射机编码组帧后,进行调制和传输。

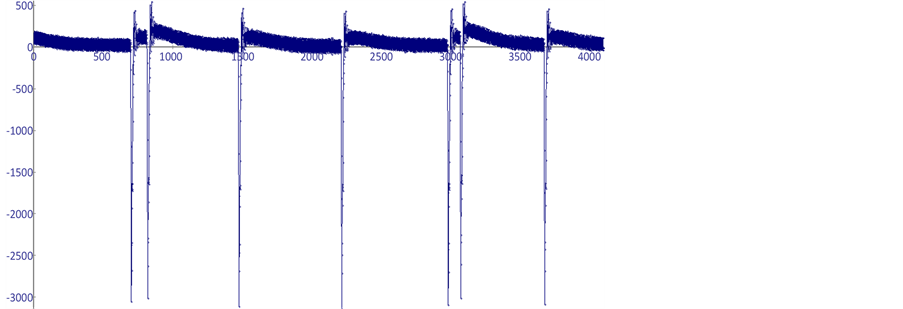

接收信号经冲击滤波和包络检波后由高速采样芯片AD9642 (最高采样频率256 MHz)采样后进入数字接收机进行验证。

图6为数字接收机的RTL结构图,图4所描述的位同步和解调系统被集成在demod模块中。其输入有时钟信号clock,14位高速采样信号ad_in,电源信号ce,输出为解调信号symbol_out和使能信号symbol_rfd。

使用FPGA硬件仿真时,利用Chipscope可以很方便地观察到各信号的值。图7为调制信号经冲击滤波器并包络检波后,由14位高速AD9652采样所得波形。可以看到,MPPSK调制信号相位突变部分已经很明显地变成幅度冲击。

demod模块根据采样信息进行数字位同步和解调工作。在收发端直连的情况下,发送2000帧数据,每帧数据252个码元,共504,000个码元,共测试10次。传统算法平均每次丢帧1.3次,而采用了新的双窗位同步算法,测试10次未发生丢帧现象,错误码元平均14个,误码率达到 量级,位同步系统正常工作,达到了实际使用所需要求。

量级,位同步系统正常工作,达到了实际使用所需要求。

5. 结束语

相较于MPPSK接收机现有的位同步算法,本文设计的双窗实时位同步算法具有同步建立时间短、不依赖冲击幅值、实时调整的优点。该算法已经过System Generator系统设计工具的仿真,和基于XilinxSpartan-6系列FPGA实现的MPPSK数字接收机的硬件协同验证,完成了MPPSK数字接收机的同

Figure 6. Digital receiver’s RTL structure diagram

图6. 数字接收机的RTL结构图

Figure 7. Sampling signal in the receiver

图7. 采样送入接收机的信号

步和解调,验证了该同步算法的可行性。

文章引用

沙 俊,吴乐南. MPPSK数字接收机位同步算法设计与实现

The Design and Implementation of Symbol Timing Synchronization Algorithm for MPPSK Digital Receiver[J]. 无线通信, 2017, 07(01): 37-44. http://dx.doi.org/10.12677/HJWC.2017.71006

参考文献 (References)

- 1. 吴乐南. 超窄带高速通信进展[J]. 自然科学进展, 2007, 17(11): 1467-1473.

- 2. 崔丽娜. 全数字接收机中的位同步技术研究[D]: [硕士学位论文]. 重庆: 重庆大学, 2008.

- 3. 吴乐南, 戚晨皓. 多元位置相移键控调制和解调方法[P]. 中国专利, ZL200710025202.1. 2010-01-27.

- 4. 仲琴, 王继武, 张树林, 等. 改进的MPPSK调制的功率谱和解调性能[J]. Hans Journal of Wireless Communications, 2014, 4(3): 45-56.

- 5. 王继武. 基于冲击滤波器的EBPSK 解调器设计, 优化与应用[D]: [硕士学位论文]. 南京: 东南大学, 2012.

- 6. Wu, L. and Feng, M. (2010) On BER Performance of EBPSK-MODEM in AWGN Channel. Sensors, 10, 3824-3834. https://doi.org/10.3390/s100403824

- 7. 但吉兵, 沈正达, 陈耀闯, 等. 基于位置信息的MPPSK解调方法[P]. 中国专利, CN103139123A. 2013-06-05.

- 8. 王勇. 一种适用于数字卫星接收机的位同步系统的研究与实现[D]: [硕士学位论文]. 北京: 中国科学院空间科学与应用研究中心, 2010.

- 9. 刘磊. QPSK相干光位同步算法研究[D]: [硕士学位论文]. 长沙: 湖南大学, 2013.

- 10. 张小龙. MPPSK调制解调器的改进与实现[D]: [硕士学位论文]. 南京: 东南大学, 2015.

- 11. 但吉兵. 基于FPGA的EBPSK调制解调器数字IC设计[D]: [硕士学位论文]. 南京: 东南大学, 2012.