Open Journal of Circuits and Systems

Vol.06 No.01(2017), Article ID:20089,7

pages

10.12677/OJCS.2017.61001

Low Power Design of TP RAM and Its Application

Qingjun Zhou, Jing Xing

ZTE Telecom College, Xian Peihua University, Xi’an Shaanxi

Received: Mar. 8th, 2017; accepted: Mar. 21st, 2017; published: Mar. 31st, 2017

ABSTRACT

As the area and power consumption of TP RAM in SoC are large, a new design method of optimization is proposed. In order to achieve the function of the original TP RAM and keep the external interface unchanged, TP RAM is replaced with SP RAM, and read-write interface logics of conversion are added around SP RAM. The method discussed in this paper is used in the multi core SoC chip which has been successfully taped out in TSMC 28 nm HPM process. The chip occupies 10.7 mm × 11.9 mm of die area and consumes 19.8 W. The testing results indicate that the area of optimized RAM is reduced by 24.5%, and the power saving is 45.16%.

Keywords:TP RAM, SP RAM, Optimization of Power Consumption, Interface Logics of Conversion

TP RAM的低功耗设计及应用

周清军,邢静

西安培华学院中兴电信学院,陕西 西安

收稿日期:2017年3月8日;录用日期:2017年3月21日;发布日期:2017年3月31日

摘 要

针对SoC中TP RAM的面积及功耗较大问题,提出一种优化设计方法。通过将SoC中的TP RAM替换成SP RAM,并在SP RAM外围增加读写接口转换逻辑,使替换后的RAM实现原TP RAM的功能,保持对外接口不变。将文中方法应用于一款多核SoC芯片,该芯片经TSMC 28 nm HPM工艺成功流片,die size为10.7 mm × 11.9 mm,功耗为19.8 W。测试结果表明:优化后的RAM面积减少了24.5%,功耗降低了45.16%。

关键词 :TP RAM,SP RAM,功耗优化,接口转换逻辑

Copyright © 2017 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

1. 引言

随着芯片集成度越来越高,随机存储器(random access memory, RAM)在片上系统(system on chip, SoC)中的占比也越来越高,因此RAM对SoC的面积及功耗的贡献也越来越大。相同容量的伪双口RAM (two ports RAM, TP RAM)与单口RAM (single port RAM, SP RAM)相比,前者的面积及功耗更大。降低SoC的面积及功耗可以节省成本,延长芯片寿命并进一步提升市场竞争力 [1] [2] [3] 。而TP RAM作为RAM的一种常用类型,在SoC中的比重也很大。因此降低TP RAM的面积及功耗,是降低整个SoC面积及功耗的有效途径。

文献 [4] 提出一款可以工作在极低电源电压条件下,功耗较低的亚阈值SRAM存储单元。为使其设计在极低电源电压条件下依然能够保持足够的鲁棒性,采用差分读出方式和可配置的操作模式。为了降低电路功耗,采用自适应泄漏电流切断机制,可降低动态操作和静态操作时的泄漏电流。文献 [5] 提出一种适用于自旋磁随机存储器的低压写入电路,利用列选和读写隔离相结合的方法,减小写入支路上的电阻,从而降低写入功耗,并可提高自旋转移力矩磁随机存储器的存储可靠性。文献 [4] [5] 中方法都是从RAM存储单元的内部结构进行设计和优化,需要改变RAM模块自身设计。而文中介绍的方法是将TP RAM作为一个整体替换成SP RAM,替换后的RAM可以作为IP直接使用。

为了降低TP RAM的面积及功耗,提出一种TP RAM的优化设计方法。在TP RAM读写时钟相同的情况下,将TP RAM替换成SP RAM,并在SP RAM外围增加读写接口转换逻辑,优化后的RAM对外接口不变,并可实现原TP RAM的功能。该优化方法可使RAM面积减少24.5%,功耗降低45.16%。

2. TP RAM优化设计方法

2.1. TP RAM替换成SP RAM的必要性

SP RAM只有一套地址总线和数据总线,读写不能同时进行。TP RAM指伪双口RAM,有两套地址总线,一套数据总线,一个口只能写,另一个口只能读。RAM的功耗组成包括动态功耗及静态功耗,总功耗等于二者之和。动态功耗大小与逻辑面积,频率及逻辑翻转率成正比。在TP RAM读写时钟相同的情况下,将TP RAM替换成2倍频率的SP RAM来实现原TP RAM的功能。由于频率变成优化前的2倍,原TP RAM的一个周期时间等于优化后的SP RAM的2个周期时间,因此SP RAM逻辑翻转率将降低为原来的一半。而相同容量的SP RAM的逻辑面积比TP RAM的小,所以优化后的SP RAM的动态功耗比TP RAM的小 [6] [7] 。静态功耗大小与逻辑面积成正比,由于相同容量的SP RAM的逻辑面积比TP RAM的小,所以优化后的SP RAM的静态功耗会变小。由于替换成SP RAM需要增加的接口控制逻辑很少,与RAM本身的逻辑面积相比基本可以忽略,因此优化后的SP RAM总功耗及面积均会减小 [8] [9] 。

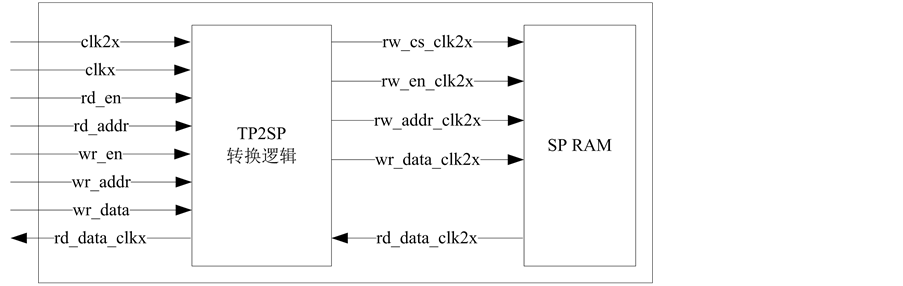

2.2. SP RAM的读写接口转换

项目中需要使用很多读写时钟相同的先进先出存储器(first in first out, FIFO),优化前这些FIFO的RAM都使用了TP RAM,运行频率都是350 MHz。使用TSMC的28 nm HPM的Memory compiler也可以生成相同容量的频率为700 M的SP RAM。将这些TP RAM替换成SP RAM后就可以达到减少面积及降低功耗的目的 [10] 。为了使替换后的SP RAM实现原TP RAM的功能,需要在SP RAM外围增加TP2SP转换逻辑。将TP RAM转换成SP RAM的转换逻辑框图如图1所示。从图1可以看到,350 M时钟域的读写控制信号经过TP2SP转换逻辑后变成了700 M时钟域的SP RAM的读写控制信号,同时SP RAM的读出数据需要转换成350 M时钟域的读出数据,且替换后的TP2SP RAM的对外接口和原TP RAM的一致。表1列出了图1中各个信号的含义,其中有外部接口信号,也有内部接口信号,内部接口信号是直接与替换后的SP RAM连接的信号。

2.3. 优化方法详细设计

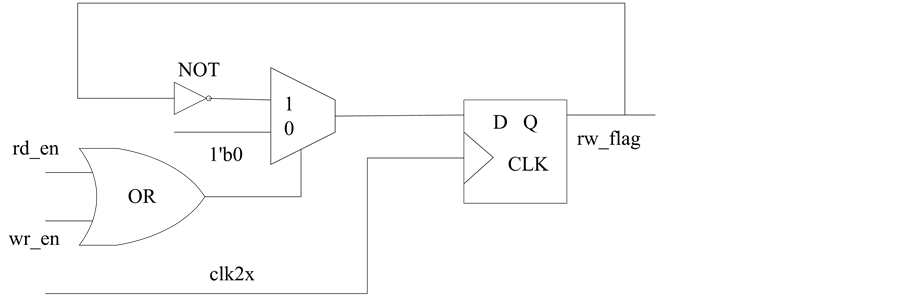

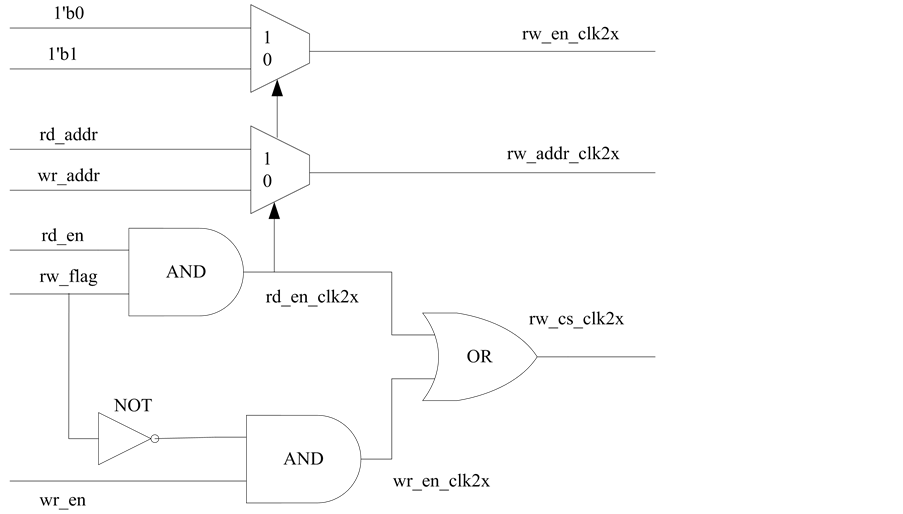

SP RAM只有一组读写控制信号,TP RAM有两组读写控制信号,所以需要将TP RAM的两组读写控制信号转换成SP RAM的一组读写控制信号。clkx是350M的TP RAM的时钟信号,clk2x是700 M的SP RAM的时钟信号,由于TP RAM可能存在读写冲突,而SP RAM不会有读写冲突,因此读写转换逻辑需要支持TP RAM的两种场景:1) 读写冲突时,读出新数据,写入新数据,即先写后读;2) 读写冲突时,读出旧数据,写入新数据,即先读后写。为了控制读写冲突,需要产生一个中间信号rw_flag,逻辑生成电路如图2。先写后读的控制方法是在rw_flag = 0时写,rw_flag = 1时读;如果需要支持先读后写,则控制方法是在rw_flag = 0时读,rw_flag = 1时写。图3列出了先写后读的控制方法的相应信号生成电路,rw_en_clk2x是SP RAM的读写控制信号,当rw_en_clk2x = 1时写,当rw_en_clk2x = 0时读。rw_cs_clk2x是SP RAM的片选控制信号,当rw_cs_clk2x = 1时有效。rw_addr_clk2x是SP RAM的读写地址信号。

Table 1. Interface signals of TP2SP RAM conversion logics

表1. TP2SP RAM转换逻辑框图接口信号列表

Figure 1. Diagram of TP2SP RAM interface

图1. TP2SP RAM转换逻辑框图

Figure 2. rw_flag generation logic

图2. rw_flag控制信号产生逻辑

Figure 3. TP2SP diagram of first writing and after reading

图3. TP2SP先写后读控制逻辑生成示意图

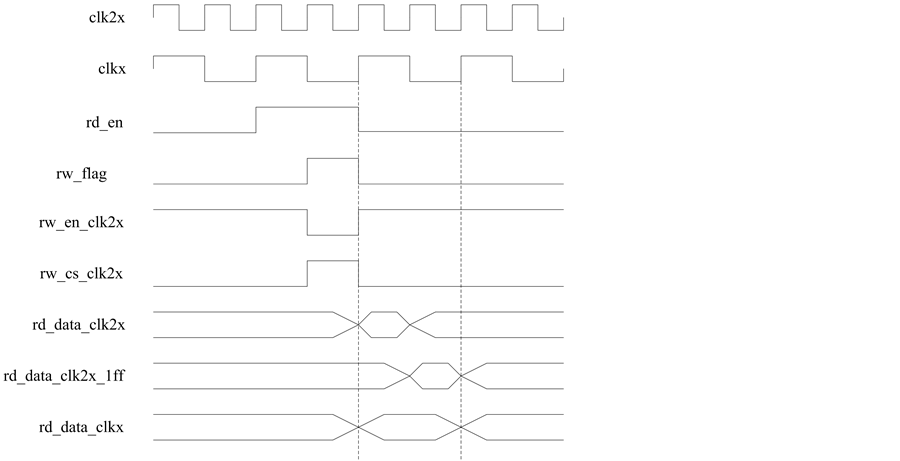

图4画出了SP RAM读出的数据转换成保持一个TP RAM时钟周期数据的时序图,clkx是350 M的TP RAM的时钟信号,clk2x是700 M的SP RAM的时钟。rd_en是外部输入的350 M时钟域的读控制信号,rd_data_clk2x_1ff是SP RAM的输出数据rd_data_clk2x延迟一个clk2x后的数据,最终输出是能够保持一个clkx时钟周期的rd_data_clkx数据。

3. 优化方法在芯片中的应用

芯片中总共使用了86M bits memory,优化前TP RAM共计37.45 M bits,其余48.55 M bits均为SP RAM。优化前的TP RAM包括2种长宽类型,一种是768*49,另一种是320*64。使用本文的优化方法将所有TP RAM替换成倍频的SP RAM。表2及表3列出了芯片中使用的TP RAM及优化后的SP RAM的规格及相应面积和功耗数据。其中功耗是指动态功耗与静态功耗之和,由于动态功耗大小与读写翻转率成正比 [11] [12] ,所以表中也列出了相应的读写翻转率数据。由于优化后TP RAM变成了频率翻倍的SP RAM,所以读写翻转率均变成优化前的一半。表中TP指TP RAM,SP指SP RAM;Compiler Lib是指生成memory时的compiler library类型,rf-2p-uhde是指register file two port ultra-high density;由于功耗还与温度及电压有关,所以表中也列出了工艺Corner: TT/0.9V/85C [13] [14] 。数量是指这种memory在芯片中使用的个数,768*49的memory使用了706个,320*64的memory使用了530个。

4. 实验结果及分析

优化前所有的TP RAM和SP RAM的面积总和为31.75 mm2,功耗为0.465 W;优化后的面积总和为23.97 mm2,功耗为0.255 W。优化后memory面积减少24.5%,功耗减少45.16%。表4列出了优化前后芯片memory面积及功耗对比数据.优化前TP RAM容量占比 = 37.42M/86M = 43.5%,如果TP RAM占所有memory的比例越高,则优化后面积减少比例越多,效果也越明显 [15] [16] 。为了测试memory的功耗,每个memory都设计成具有旁路功能,当开启某memory旁路功能后,该memory的输入直接穿透到输出,此时测试的芯片功耗中该memory的功耗为0;当关闭该memory旁路功能后测试的芯片功耗就包含了该memory的功耗。该memory旁路前后测试的芯片功耗之差就等于该memory的功耗。

Figure 4. Timing diagram of conversion logic for output data

图4. 输出数据转换时序图

Table 2. Data comparison between TP RAM and SP RAM in size 768*49

表2. 768*49的TP RAM与SP RAM对比

Table 3. Data comparison between TP RAM and SP RAM in size 320*64

表3. 320*64的TP RAM与SP RAM对比

Table 4. Area and power comparison between before optimization and after

表4. 优化前后芯片memory面积及功耗对比列表

Table 5. Main features of SOC after tape-out

表5. 流片后的SOC主要特征列表

优化后的芯片经TSMC 28nm HPM工艺成功流片,封装类型是FCBGA33*33,芯片die size是10.710 mm*11.907 mm,使用了8个ARM Cortex-A15核,CPU运行最高频率为1.4 GHz。芯片测试平台是93 K,在TT/0.9V/85C时测试功耗为19.8 W,成品率为73.6%。表5列出了该芯片的一些主要特征。

5. 结语

本文通过将读写时钟相同的TP RAM替换成倍频的SP RAM,并在SP RAM外围增加读写接口转换逻辑,使替换后的RAM实现原TP RAM的功能,从而达到减少面积及降低功耗的目的。将优化后的SP RAM应用于一款多核SoC芯片,该芯片经TSMC 28nm HPM工艺成功流片,封装类型是FCBGA33*33,芯片die size是10.710 mm*11.907 mm。芯片测试结果表明:优化后的RAM面积减少了24.5%,功耗降低了45.16%。

基金项目

国家自然科学基金项目(61376099, 6143000024),陕西省教育厅专项基金项目(16JK2138)。

文章引用

周清军,邢 静. TP RAM的低功耗设计及应用

Low Power Design of TP RAM and Its Application[J]. 电路与系统, 2017, 06(01): 1-7. http://dx.doi.org/10.12677/OJCS.2017.61001

参考文献 (References)

- 1. Chiu, P.-F. (2012) Low Store Energy, Low VDDmin, 8T2R Nonvolatile Latch and SRAM with Vertical-Stacked Resistive Memory (Memristor) Devices for Low Power Mobile Applications. IEEE Journal of Solid-State Circuits, 47, 1483-1496. https://doi.orgg/10.1109/JSSC.2012.2192661

- 2. Lutkemeier, S., Jungeblut, T., Berge, H.K.O., et al. (2013) A 65 nm 32 b Subthreshold Processor with 9T Multi-Vt SRAM and Adaptive Supply Voltage Control. IEEE Journal of Solid-State Circuits, 48, 8-19. https://doi.orgg/10.1109/JSSC.2012.2220671

- 3. Aghamohammadi, M.R. and Abdolahinia, H. (2014) A New Approach for Optimal Sizing of Battery Energy Storage System for Primary Frequency control of Islanded Microgrid. International Journal of Electrical Power and Energy Systems, 54, 325-333.

- 4. 柏娜, 冯越, 龙肖虎, 等. 极低电源电压和极低功耗的亚阈值SRAM存储单元设计[J]. 东南大学学报: 自然科学版, 2013, 43(2): 268-273.

- 5. 张丽, 庄奕琪, 赵巍胜, 等. 一种适用于自旋磁随机存储器的低压写入电路[J]. 西安电子科技大学学报: 自然科学版, 2014, 43(3): 131-136.

- 6. Yu, H.Z., Wang, P.J., Wang, D.S., et al. (2013) Discrete Ternary Particleswarm Optimization for Area Optimization of MPRM Circuits. Journal of Semiconductors, 34, 118-123. https://doi.orgg/10.1088/1674-4926/34/2/025011

- 7. 高闯, 吴利华, 刘海南, 等. 一种用于FPGA的可配置存储器设计[J]. 固体电子学研究与进展, 2016, 36(1): 67-70.

- 8. Peng, S.-Y., Huang, T.-C., Lee, Y.-H., et al. (2013) Instruction-Cycle-Based Dynamic Voltage Scaling Power Management for Low-Power Digital Signal Processor with 53% Power Savings. IEEE Journal of Solid-State Circuits, 48, 2649-2661. https://doi.orgg/10.1109/JSSC.2013.2274885

- 9. Sheng, D., Chung, C.-C., Lee, C.-Y., et al. (2011) A Low-Power and Portable Spread Spectrum Clock Generator for SoC Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19, 1113-1117. https://doi.orgg/10.1109/TVLSI.2010.2044903

- 10. Hemalatha, A.A. (2011) Shanmugam.Computer Aided Design for Low Power Fir Processor on System On-Chip Platform Architecture for High Performance DSP Applications. International Journal of Computer Science and Network Security, 11, 38-42.

- 11. Rick, P. and Aurangzeb, K. (2014) Design for Data-Center, Low-Power and SoCs. 2014 IEEE Proceedings of the Custom Integrated Circuits Conference, San Jose, California, 15-17 September 2014, 1-1.

- 12. Jain, A., Subramanian, S., Parekhji, R.A., et al. (2011) Design Techniques with Multiple Scan Compression Codecs for Low Power and High Quality Scan Test. Journal of Low Power Electronics, 7, 502-515. https://doi.orgg/10.1166/jolpe.2011.1161

- 13. Ward-Foxton, S. (2012) Wireless SoCs Use Cortex-MO Core To Slash Power Consumption. Microwaves & RF, 51, 36.

- 14. Mahdoum, A. (2012) Combined Heuristics for Synthesis of SOCs with Time and Power Constraints. Computers and Electrical Engineering, 38, 1687-1702.

- 15. 沈玲羽, 庞屹林, 范阳, 等. 红外读出电路中低功耗列读出级电路的设计[J]. 固体电子学研究与进展, 2015, 35(4): 378-382.

- 16. Lakdawala, H., Schaecher, M., Fu, C.-T., et al. (2013) A 32 nm SoC with Dual Core ATOM Processor and RF WiFi Transceiver. IEEE Journal of Solid-State Circuits, ,48, 91-103. https://doi.orgg/10.1109/JSSC.2012.2222812