Computer Science and Application

Vol.

12

No.

05

(

2022

), Article ID:

51907

,

9

pages

10.12677/CSA.2022.125138

基于FPGA的AES加密算法优化设计

刘政文,赵曙光

东华大学信息科学与技术学院,上海

收稿日期:2022年4月26日;录用日期:2022年5月24日;发布日期:2022年5月31日

摘要

现如今随着网络技术的不断发展,网络设备的数据处理速度变得越来越快,与此同时,信息安全相关的问题也逐渐显现了出来。针对高速网络信息的报文加密的优化问题,提出了一种AES加密的优化方法。通过对明文的识别、分组加密和替换,有效地隐藏了明文序列,提高了网络报文的保密性和安全性。经测试,优化后的AES加密算法可以正确有效地完成高速网络报文的加解密部分的工作。

关键词

FPGA,AES加密算法,信息安全

Optimization Design of AES Encryption Algorithm Based on FPGA

Zhengwen Liu, Shuguang Zhao

College of Information Science and Technology, Donghua University, Shanghai

Received: Apr. 26th, 2022; accepted: May 24th, 2022; published: May 31st, 2022

ABSTRACT

Nowadays, with the continuous development of network technology, the data processing speed of network equipment is becoming faster and faster. At the same time, the problems related to information security have gradually emerged. Aiming at the optimization problem of packet encryption in high-speed network, an optimization method of AES encryption is proposed. Plaintext identification, packet encryption and replacement can effectively hide plaintext sequence and improve the confidentiality and security of network messages. After testing, the optimized AES encryption algorithm can correctly and effectively complete the encryption and decryption of high-speed network packets.

Keywords:FPGA, AES Encryption Algorithm, Information Security

Copyright © 2022 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

1. 引言

目前计算机技术与网络技术都在迅猛地发展,网络数据的交互也日趋频繁与复杂。随着网络电子设备的不断更新升级,用户在享受着网络带来的便利时也开始对网络安全、信息窃取等问题感到担忧 [1]。维护信息安全的方法中,一个重要的方法是使用密码学中的加密算法,对传输的数据进行替换,使用密钥序列和数据变换方法,将明文隐藏起来,从而对重要信息进行保护,增强数据的安全性和保密性 [2]。

高级加密标准(Advanced Encryption Standard, AES)加密算法是分组加密算法的一种,是目前美国联邦政府采用的一种加密技术 [3]。近年来,许多学者都对AES算法加以研究。Soltani Abolfazl提出以电子密码本和计数器模式提高AES的吞吐量,并结合内存和非内存的方法实现算法中的S盒结构,提高AES在应用时的性能 [4]。Syed Shahzad Hussain Shah提出了一种基于混沌的AES算法实现架构,由混沌映射生成密钥,同时使用并行RAM实现字节替代环节,以优化AES算法的执行结构 [5]。戴强等人提出了改进后的CSE算法对AES算法中S盒的电路结构进行优化 [6]。

针对高速网络报文的信息安全问题,本文提出了一种AES加密算法的设计方案,将网络报文中的数据识别分组并进行加密替换以隐藏明文。同时优化了AES算法使用时的工作流程和工作模式,使AES算法能够有效地应用在高速网络报文的场景中,提高网络报文的保密性和安全性。

2. AES算法原理

AES加密算法是分组加密算法中的一种,它是在Rijndael加密算法的基础上,做出了一定程度的简化而设计的 [7]。AES规定了加解密流程中的数据和密钥的长度,每个分组的数据长度为128 bit,而密钥的长度可以设置为128 bit,192 bit或是256 bit,然后依据不同的密钥长度,算法执行相应的迭代轮数。

2.1. 算法描述

AES加密算法的每一步都是作用于矩阵的形式进行变换,每次输入的数据为128 bit,以字节为单位分成16个字节,将其排列为4*4的矩阵,AES的每一轮变换都是由四个步骤组成,分别是字节替代,行移位,列混淆和轮密钥加,AES-128加密算法的流程图如图1所示。

AES-128算法在加密迭代前使128 bit的明文数据与初始密钥进行一次异或再进入迭代程序,加密时每次迭代时每轮有四个步骤,即字节替代、行移位、列混淆和与扩展好的密钥异或计算,最后一轮加密时移除列混淆步骤,最终输出的结果即为128 bit的密文数据。解密时的步骤与加密时相反,密文输入先与密钥扩展的最后4个双字密钥异或后启动解密算法迭代,每次迭代依次进行四个解密步骤,分别是逆列混淆、逆行移位、逆字节替代和轮密钥加,完成所有的迭代轮数就可以完成解密算法与输出128 bit的明文数据 [8]。

Figure 1. AES-128 algorithm flow chart

图1. AES-128算法流程图

2.2. 字节替代

字节替代是一种非线性变换,将一个8 bit的数据通过变换用另一个与之唯一相互对应的另一个8 bit的数据替换掉原始数据,并且要求能够通过逆变换使新数据恢复成原始数据。

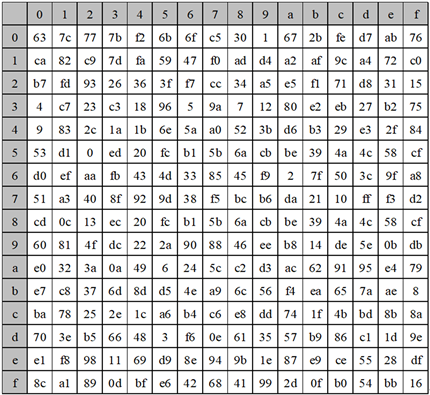

AES加密算法定义了S盒和逆S盒,两个表均占用了16*16的存储空间,用于完成算法加密和解密中的字节替代工作。S盒使用查表法的方式执行,旧数据以8 bit为单位输入,高4 bit数据作为行系数查表,低4 bit作为列系数查表,以此将输入的数据变换为8 bit的新数据输出,即为字节替代的结果。S盒内容如图2所示。

Figure 2. S-box

图2. S盒

2.3. 行移位

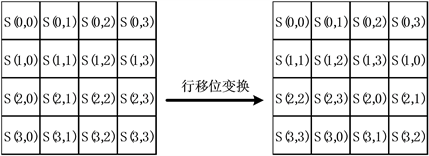

行移位变换是加密算法对输入数据矩阵以每一行为单位做移位变换,矩阵的第一行做变换,第二行到第四行分别左移1~3字节。行移位的操作不会改变每个字节的数值,而是将矩阵的每一列重新对齐,使数据排列更加的无序,增强了加密算法的复杂度。在解密过程中使用的是逆行移位变换,同样第一行不做变换,2~4行分别右移1~3字节。行移位变换步骤模型如图3所示。

Figure 3. Schematic diagram of row shift transformation

图3. 行移位变换原理图

2.4. 列混淆

列混淆是对数据矩阵进行列方向的变换,变换的矩阵乘法表达示如下:

(1)

式中矩阵里的每个元素都是对应位置元素的乘积之和,其中矩阵中的乘法与加法均为基于有限域GF(28)上的二元运算。在GF(28)中加法运算表示为不进位的异或运算,乘法运算为则是对移位、异或、取模的结合,在GF(28)中取模运算的标准为 。在解密过程中,逆列混淆的操作不变,仅将解密中间矩阵替换为加密的逆矩阵。逆列混淆表达式下:

(2)

2.5. 轮密钥加

轮密钥加时将准备好的数据与经过密钥扩展提取后的密钥按位进行异或运算,运算的结果作为下一次加密迭代的输入,或是在最后一轮直接成为最终的输出。轮密钥加的过程减弱了明文与密文之间的直接联系,增强了数据与密钥之间的联系,使破解密码的难度大大提升。

2.6. 密钥扩展

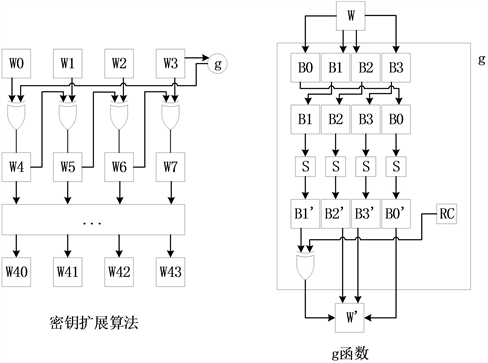

AES算法每一轮都需要使用密钥与数据进行异或运算,所以输入的密钥长度是不足够算法所使用的,在迭代的过程中相应的要对密钥进行扩展工作。AES-128的密钥扩展算法原理图如图4所示。

Figure 4. Key extension schematic diagram

图4. 密钥扩展原理图

将密钥以1个字节为一组分割成16个部分,排列组成一个4*4的矩阵。每一列用4维向量所表示,注为[w0, w1, w2, w3],其中位于w3位置的4字节数据需要进行一次g函数的运算,g函数会输入进来4字节的数据,分成四份,每份一个字节,4字节的数据排列好后左循环1字节,并带入S盒中进行字节替代,经过以上流程w3替换成了w’。生成的w’输入进原矩阵依此进行一系列的异或运算以生成本轮的密钥。

3. AES模块设计与分析

为了将AES加密算法的数据处理速度能够与高速网络报文传输速度相匹配,需要合理设计算法内部执行模块的连接结构,以保证模块内部的数据流不会丢失或是存在逻辑冲突,使数据流能够互不影响的完整各自的阶段性变换。AES工作流程的设计还要兼顾占用资源的多少以及是否容易实现的问题。

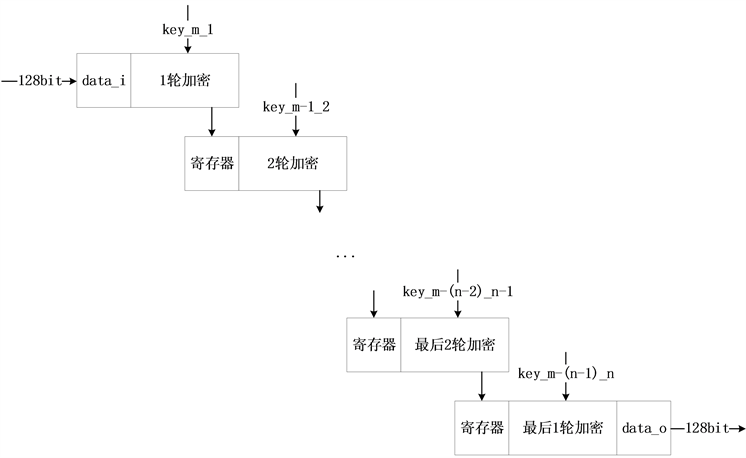

AES-128加密算法中,每个加密分组要迭代10次,若采用环展开结构在一个时钟周期完成10次迭代的全部流程,需要设计出一个巨大的组合逻辑电路,对FPGA内部电路,造成巨大的时序压力,性价比不高,因此需要通过流水线的结构完成AES中迭代算法的连接。流水线化的设计是对于比较复杂的结构进行分解,分成多个层次分成多个周期执行,这种设计模式适用于同一组程序需要反复执行的情况。流水线化的设计在每个层级都要设置寄存器来暂存数据的状态,在下个时钟周期会被下一个层级抽取,而上一个层级同时也会被新的数据填充,像流水线一样将顺序程序一层一层的串联起来,并以此完成数据的并行处理。AES-128算法流水线化的设计中,第一组数据输入进模块完成一轮加密,下一个周期这一组数据进行第二轮加密,同时第二组数据输入进模块完成第一轮加密,经过十个周期的迭代,此时第一组数据完成了AES的加解密,而第二组数据的加解密流程也即将完成。流水线结构完成AES加密的结构示意图如图5所示。

Figure 5. AES-128 pipeline structure design

图5. AES-128流水线结构设计

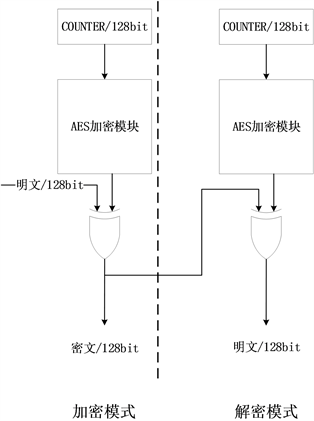

AES-128的输入模式选取了计数器(Counter, CTR)模式,CTR模式支持AES算法的流水线结构设计,使AES加密算法的加密速度可以与高速网络报文的数据处理效率所匹配。CTR模式中加密数据由计数器生成,加密数据通过10次迭代加密生成加密的结果,此时取出网络报文的明文数据,与加密结果异或,得到密文数据,在解密操作中,同样需要通过计数器生成一个相应额序列,并使用AES加密算法进行解密,加密后的结果与密文异或即可生成网络报文明文。使用CTR加密模式的优点是有效解决了报文拉长的问题,AES算法的最小单位是128 bit,不能保证网络报文长度是128 bit的倍数,使用CTR模式,网络报文数据只在加密结束时参与加密计算,多余的密文或原文长度的舍弃不影响加解密的结果,有效的解决了报文拉长的问题 [9]。CTR模式的AES加解密算法示意图如图6所示。

Figure 6. CTR mode AES encryption and decryption algorithm

图6. CTR模式的AES加解密算法

4. AES算法的仿真

本文使用了Verilog HDL硬件描述语言在FPGA上对AES加解密流程进行了设计,并使用了ModleSim 10.4仿真软件来验证程序逻辑的正确性。

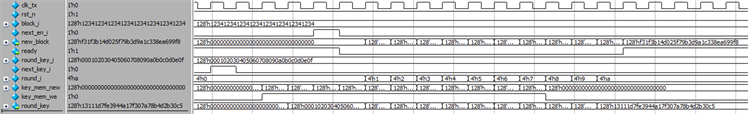

对AES-128模块的加密逻辑进行验证时,要输入初始的密钥和待加密的数据,再由系统自动扩充密钥,将密钥与待加密的数据进行迭代运算,最终输出加密好的密文,加密仿真图如图7所示。

Figure 7. AES-128 encryption simulation diagram

图7. AES-128加密仿真图

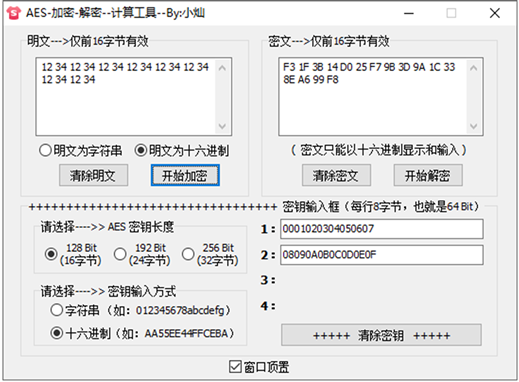

仿真激励将初始明文信号设为0x12341234_12341234_12341234_12341234,也给出了128bit的初始密钥0x00010203_04050607_08090a0b_0c0d0e0f,用来对明文进行加密。128 bit的初始密钥要对AES模块完成10轮的加密迭代,在迭代之前要对初始明文和初始密钥先完成一次轮密钥加的运算,之后在迭代中要分别完成字节替代、行移位变换、列混淆变换和与扩展后的密钥完成轮密钥加变换,除最后一轮不必完成列混淆变换。仿真图表明经过10轮迭代后得到最终的密文序列为0xf31f3b14_025f79b3_3d9a1c33_8ea699f8。使用第三方软件设置相同的初始状态,以对AES加密模块的功能逻辑正确性进行验证,第三方的加密结果如图8所示。通过将AES加密模块的结果和第三方的128 bit输入密钥的AES加密结果进行对比,两者的解密结果是完全一样的,可以证明AES加密功能是正确的。

Figure 8. Third-party software verifies the AES encryption algorithm

图8. 第三方软件验证AES加密算法

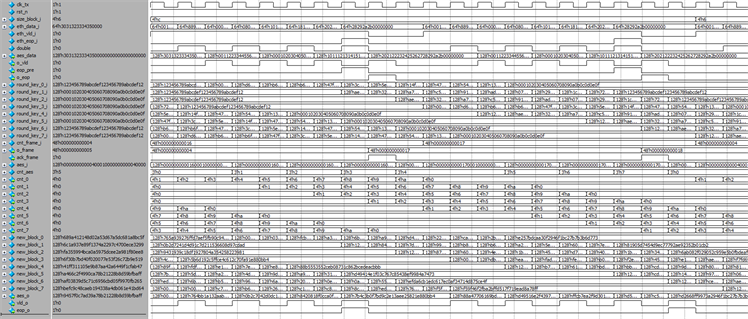

Figure 9. Network packet encryption process simulation diagram

图9. 网络报文加密流程仿真图

将经过优化后的AES加密流程应用在10 G以太网的环境中,系统搭建了仿真平台验证网络报文高速加解密功能的有效性。在设计高速加解密的流程时,先要每两个发送周期采集一次10 G以太网帧格式的网络报文,生成128 bit的明文序列,再根据报文的发送状态生成CTR工作模式下的AES加密模块的输入,完成加密后序列与128 bit的明文相加,即可得到密文序列,生成的128 bit密文序列再按时序进行分解,变成每个周期64 bit的密文序列,再重新校验以及组装成以太网报文的格式,即完成了对网络报文进行高速加解密的功能。网络报文加密流程仿真图如图9所示。

图中使用了仿真激励模拟生成了以太网报文待加密的数据的时序逻辑,将网络报文内容输入进模块中,最终以流水线的形式得到加密好的128 bit密文序列。通过仿真实验模拟了真实连续发送高速网络报文的情况,验证了连续工作状态下AES加密模块的工作状态,经过多次以及多种情况的仿真实验,实验结果表明模块能够正确有效的完成高速网络报文的加解密部分的工作,证明了设计模型是先进且可靠的。

5. 总结

本文通过对AES加密算法的输入模式和工作流程进行了优化,使其能够应用于高速网络报文的加密和解密工作,完成了网络报文的明文提取加密和密文替换报文内容的工作,为高速网络报文的信息安全工作提供了解决思路。本文通过仿真实验模拟了算法在10 G以太网报文中的表现结果,证明了方案的有效性。

文章引用

刘政文,赵曙光. 基于FPGA的AES加密算法优化设计

Optimization Design of AES Encryption Algorithm Based on FPGA[J]. 计算机科学与应用, 2022, 12(05): 1389-1397. https://doi.org/10.12677/CSA.2022.125138

参考文献

- 1. 李炽阳, 雷倩倩, 杨延飞. 全通用AES加密算法的FPGA实现[J]. 计算机工程与应用, 2020, 56(10): 83-87.

- 2. 窦贤振. 基于FPGA的AES加密算法设计与实现[J]. 科技风, 2019(36): 64.

- 3. 王常磊. 基于FPGA的数据加密算法设计与实现[D]: [硕士学位论文]. 哈尔滨: 黑龙江大学, 2020.

- 4. Soltani, A. and Sharifian, S. (2015) An Ultra-High Throughput and Fully Pipelined Implementation of AES Algorithm on FPGA. Microprocessors and Microsystems, 39, 480-493.

- 5. Shah, S.S.H. and Raja, G. (2015) FPGA Implementation of Chaotic Based AES Image Encryption Algorithm. 2015 IEEE International Conference on Signal and Image Processing Applications (ICSIPA), Kuala Lumpur, 19-21 October 2015, 574-577. https://doi.org/10.1109/ICSIPA.2015.7412256

- 6. 戴强, 戴紫彬, 李伟. 基于增强型延时感知CSE算法的AES S盒电路优化设计[J]. 电子学报, 2019, 47(1): 131-138.

- 7. 钱浩. 基于FPGA的千兆网络安全通信研究与实现[D]: [硕士学位论文]. 杭州: 杭州电子科技大学, 2017.

- 8. 赵新杰, 郭世泽, 王韬, 刘会英. 针对AES和CLEFIA的改进Cache踪迹驱动攻击[J]. 通信学报, 2011, 32(8): 101-110.

- 9. 阮景林, 刘林. GPON中的AES加密[J]. 中国集成电路, 2007(12): 32-35.