Applied Physics

Vol.4 No.05(2014), Article ID:13562,8 pages

DOI:10.12677/APP.2014.45011

The Influence of Different Gate Oxide Thickness on Carbon Nanotube Transistors

Faculty of Science, Ningbo University, Ningbo

Email: yuwj88666@126.com

Copyright © 2014 by author and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received: Apr. 12th, 2014; revised: May 2nd, 2014; accepted: May 10th, 2014

ABSTRACT

In this thesis, non-equilibrium Green function theory is applied to calculate random-telegraphsignal (RTS) noises caused by a single defect in gate oxide of carbon nanotube field-effect (CNFET) transistors. We investigate systematically how RTS noises depend on gate oxide thickness and discuss the RTS noises with two different situations: a single layer and a composite layer.

Keywords:Carbon Nanotube, Field Effect Transistor, Non-Equilibrium Green Function, Random Telegraph Signal Noise

介质厚度不同对碳纳米管场效应晶体管的影响

余文娟

宁波大学理学院,宁波

Email: yuwj88666@126.com

收稿日期:2014年4月12日;修回日期:2014年5月2日;录用日期:2014年5月10日

摘 要

本文运用非平衡格林函数理论,计算碳纳米管场效应晶体管栅极氧化层中由一个缺陷电荷引起的无规则电报信号杂音。文章模拟计算了该杂音强弱与栅极氧化层厚度的依赖关系,研究单层和复合绝缘层两种不同情况下碳纳米管场效应晶体管中的无规则电报信号杂音。

关键词

碳纳米管,场效应晶体管,非平衡格林函数,无规则电报信号杂音

1. 引言

碳纳米管具有高强度和稳定性,依据其手性角和半径可以呈现出金属性或半导体性[1] ,由于这些电学性能,很多研究都预期碳纳米管会在场效应晶体管中有新的应用前景。通过不断地对尺寸和电极进行改进,实验室已制备高性能的碳纳米管场效应晶体管[2] [3] 。

一般各种电子材料都观测到无规则电报信号杂音[4] ,这种杂音其实是在两种或多种电流值之间随机变换。实验中已经观察到碳纳米管中由于个别缺陷引起的无规则电报信号杂音[5] ,而且已经观察到其强度高达60%以上[6] 。理论研究同样也发现在碳纳米管场效应晶体管栅极氧化层中由缺陷电荷引起的大幅度电流变化[7] [8] 。一些实验甚至在50 mV的偏压下观测到[9] [10] ,杂质离子在碳纳米管与绝缘介质的界面附近和碳纳米管与晶体管的电极接触处附近引起的无规则电报信号杂音。在一定程度上,该杂音不可避免的会阻碍碳纳米管场效应晶体管的产业化进程。

传统的金属氧化物半导体场效应晶体管(MOSFETs)和碳纳米管场效应晶体管(CNFETs)一般都用SiO2作为栅极绝缘层的介质。为了不断提高场效应晶体管的性能,SiO2的厚度已将近达到极限,简单地采用薄的、介电常数大的材料并不是减小杂音的最好方法,因为很薄的且介电常数大的绝缘层可能会导致栅极漏电流[11] 。最近,已有人尝试用复合电介质作为栅极氧化层,克服栅极漏电问题[12] [13] 。

在参考文献[14] 中提到,使用单层介电常数比较大的电介质或介质层的厚度比较薄,都可以有效减小无规则电报信号杂音的强度。然而杂音的强度与复合介质的厚度有怎样的关系是目前不得而知的。在这篇文章中,我们研究单层和复合绝缘层两种不同情况下碳纳米管场效应晶体管中的无规则电报信号杂音。

2. 理论计算部分

2.1. 碳纳米管中电流的计算

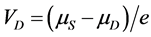

在适当的栅极电压下,如果施加漏极偏压,源极和漏极之间就会产生电流。漏极电压与源极和漏极的费米能级有关,表达式为 。散射区的推迟格林函数可以表示为[15]

。散射区的推迟格林函数可以表示为[15]

(1)

(1)

其中I为单位矩阵,H是碳纳米管散射区的哈密顿量, 为源极或漏极的推迟自能。我们用紧束缚近似描述碳纳米管的哈密顿量,通过求解有限偏压时的泊松方程可以得到沿纳米管方向的势能。势能被包含在碳纳米管的哈密顿量H中,由方程(1)可以看出,势能发生变化,格林函数

为源极或漏极的推迟自能。我们用紧束缚近似描述碳纳米管的哈密顿量,通过求解有限偏压时的泊松方程可以得到沿纳米管方向的势能。势能被包含在碳纳米管的哈密顿量H中,由方程(1)可以看出,势能发生变化,格林函数 也会相应地发生变化。因此,散射区的格林函数

也会相应地发生变化。因此,散射区的格林函数 、碳纳米管上的电荷分布以及沿碳纳米管方向的势能必须通过自洽运算得到。

、碳纳米管上的电荷分布以及沿碳纳米管方向的势能必须通过自洽运算得到。

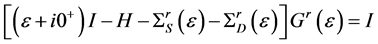

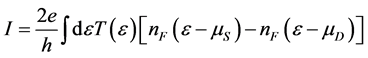

自洽计算出格林函数 后,可以通过

后,可以通过 方程[16] 计算通过碳纳米管的电流

方程[16] 计算通过碳纳米管的电流

(2)

(2)

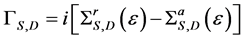

上式中的2是由于自旋简并得到的, 为费米函数。方程(2)中的

为费米函数。方程(2)中的 表示穿透系数,可以通过下面方程计算得到[15]

[17]

表示穿透系数,可以通过下面方程计算得到[15]

[17]

(3)

(3)

其中 。

。

2.2. 无规则电报信号杂音的表达式

如果一个电量为Q = +1e的缺陷电荷出现在P型碳纳米管场效应晶体管的栅极氧化层中,那么碳纳米管上的空穴载流子在输运过程中会受到势能散射。由于散射作用,此时的穿透系数与没有缺陷电荷时相比明显降低了,因此体系的电流IQ比没有缺陷情况下的电流I0小。缺陷可能释放一个空穴给碳纳米管,这样缺陷就变为中性,这时通过体系的电流为I0。然后,中性缺陷可能又从碳纳米管中俘获一个空穴,缺陷带电量又变为Q = +1e,由于散射作用,通过碳纳米管场效应晶体管的电流又变为IQ[18] -[20] 。

因此,空穴的释放和俘获会导致电流在I0和IQ = +1之间无规则的变化,这就导致无规则电报信号杂音。由于缺陷电荷导致的这种无规则电报信号杂音强度定义为电流变化的相对变化值

(4)

(4)

其中IQ和I0分别为碳纳米管场效应晶体管中有缺陷电荷和无缺陷电荷时的电流强度。

3. 介质中缺陷引起的无规则电报信号杂音

3.1. 杂音与单层介质厚度的关系

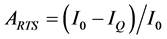

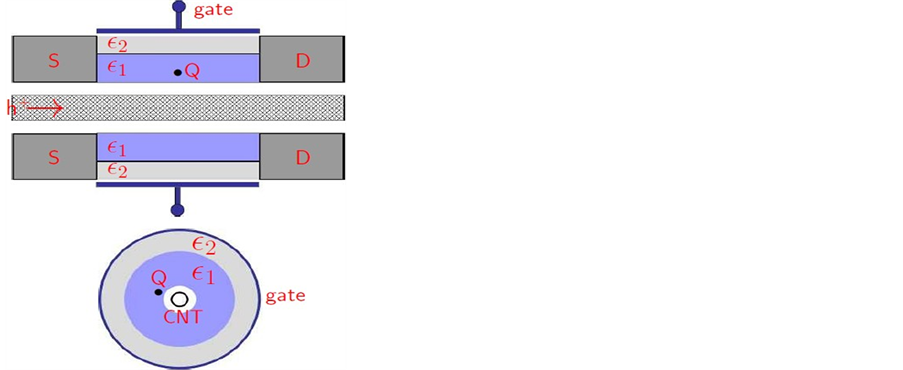

在这篇文章中我们选取锯齿型(n, 0)半导体碳纳米管,纳米管由绝缘介质氧化层包围,如下图1所示,碳纳米管被分为三部分:电势相同的半无限长的源极和漏极以及自洽的散射区。碳纳米管在源极和漏极中的散射区长度为24 nm,源极和漏极之间的沟道长度取为200 nm。栅极氧化层与碳纳米管之间有0.3 nm(即范德瓦耳斯半径)的间隙,因此,氧化层厚度tox与栅极半径Rg和碳纳米管半径RNT的关系如下:tox = Rg − RNT − 0.3 nm。两电极(源极和漏极)的功函数比碳纳米管的费米能大1 eV,这样就形成了P型欧姆接触。

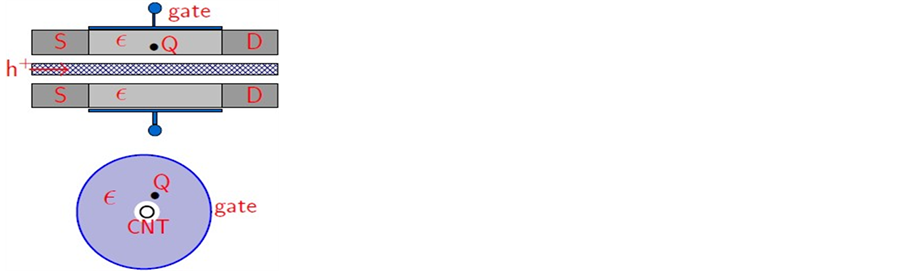

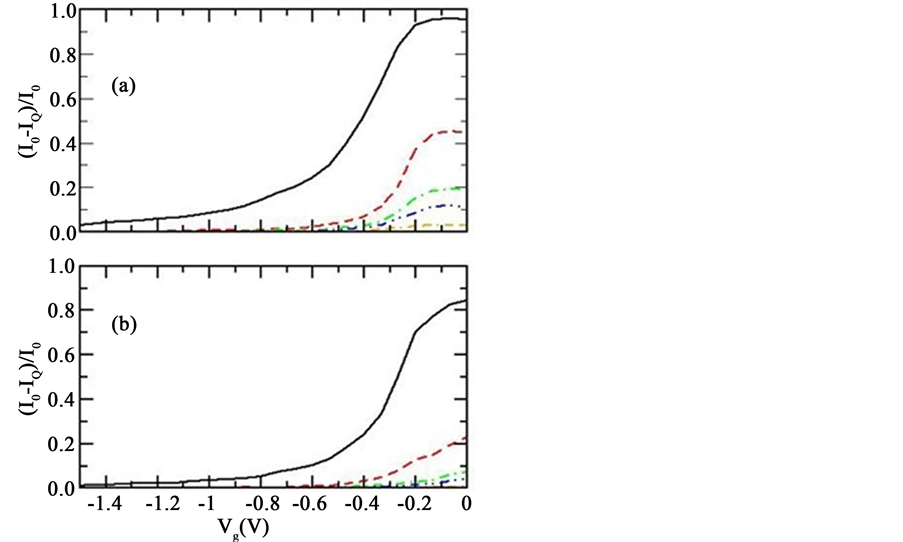

为了知道单层介质层的厚度与电杂音的关系,我们计算了栅极半径分别为2 nm,4 nm,8 nm,16 nm,32 nm时,通过场效应晶体管的电流。对于(17, 0)型碳纳米管,氧化层厚度可按下式来计算tox = Rg − RNT − 0.3 nm = Rg − 1 nm。所以,上述各栅极半径对应的介质厚度分别为1 nm,3 nm,7 nm,15 nm,31 nm。由此得到的电报信号杂音强度如图2所示。

Figure 1. The cylindrical geometry of a CNFET

图1. 碳纳米管场效应晶体管(CNTs)的横截面图

Figure 2. The amplitude of the RTS noise at Vd = −50 mV due to an impurity charge of Q = +1e inside the gate oxide of SiO2 and at 0.4 nm away from the nanotube wall. The calculation is performed for different gate radii, from right to left, of 2 nm (black solid curve), 4 nm (red dashed curve), 8 nm (green dot-dashed curve), 16 nm (blue double dot-dashed curve), and 32 nm (orange double dash-dotted curve)

图2. 在Vd = −50 mV,栅极介质为SiO2的情况下,一个带正电的缺陷电荷在距纳米管壁0.4 nm处引起的无规则电报信号杂音幅度。从右往左各曲线对应的门极半径分别为2 nm(黑色实线),4 nm(红色虚线),8 nm(绿色点虚线),16 nm(蓝色双点虚线),32 nm(橘色双虚点线)的计算结果

由图2我们可以看出,随着栅极氧化层厚度的增加,无规则电报信号杂音强度也增大。这是因为栅极越远离杂质离子,栅极电荷对杂质离子的屏蔽作用越小,杂质离子对载流子的散射作用越强,故无规则电报信号杂音的强度越大。

无规则电报信号杂音与介质层介电常数也有一定的依赖关系[14] 。下面我们同样选取(17, 0)锯齿形碳纳米管。选择六种不同的栅极绝缘层,其介电常数分别为3.9、10、20、30、40、80,研究杂质离子在栅极氧化层中离碳纳米管壁0.4 nm时引起的无规则电报信号杂音与绝缘层介电常数的依赖关系。得到的计算结果如下图所示。

很明显由图3(c)可以看出随着介电常数的增大,电报信号杂音相应减小。当介电常数增大到80,启动状态时的电报信号杂音强度减小到30%,而在工作状态杂音强度不到0.1%。

为了知道通过减小介质厚度和增大介电常数,该杂音可以减小到何种程度,我们计算了氧化层厚度为1 nm,介电常数分别为3.9、16、30、40、80时无规则电报信号杂音强度;以及氧化层厚度为2 nm,介电常数为3.9、16、30、40、80时的无规则电报信号杂音强度,由此得到的杂音强度随栅极电压的变化关系曲线如图4所示。

对比图4(a),图4(b)发现要有效地减小杂音强度不仅要增大介电常数,而且要减小介质层的厚度。从上图4(b)可知,对于介质厚度为1 nm,介电常数为80的晶体管,电报信号杂音的幅度在启动状态可以减小到2%,在工作状态接近0.1%,这样的杂音也可以视为低杂音。

3.2. 杂音与复合介质厚度的关系

我们知道,随着介质厚度的减小,电报信号杂音的强度也减小。但是,如果栅极介质层太薄,栅极

Figure 3. The top pannel shows the current with no trapped charge for different dielectric constants of 3.9 (black solid curve), 10 (red dashed curve), 20 (green dot-dashed curve), 30 (bluedouble dot-dashed curve), 40 (cyan double dashdotted curve), and 80 (orange dotted curve). The middle pannel shows the current with a trapped charge of Q = +1e in the different gate oxides defined for the top pannel and at 0.4 nm away from the nanotube wall. The bottom pannel shows the amplitude of the RTS noise due to the trapped charge defined for the middle panel

图3. (a) 表示无束缚电荷时的电流,介电常数分别对应为3.9(黑色实线),10(红色虚线),20(绿色点虚线),30(蓝色双点虚线),40(青色双虚点线),80(橘色点线);(b) 表示一个带正电的束缚电荷在距纳米管壁0.4 nm时的电流;(c) 表示由束缚电荷引起的杂音幅度变化

就会出现漏电流,因为在半导体纳米管的费米能级和栅极的费米能级之间会有隧穿效应。实验中使用二氧化铪(HfO2)作为电介质时发现碳纳米管场效应晶体管栅极与漏极之间存在漏电流。为了防止或减小栅极漏电流,晶体管绝缘层使用复合电介质已经有研究[11] 。这样的话,无规则电报信号杂音与复合介质层的厚度有怎样的关系就成为有意义的研究问题。为了解决这个问题,我们设计了这样一种模型,如图5所示。

如图5所示,在这种结构中,靠近纳米管即里面一层电介质厚度为t1,介电常数为 ,外面一层介质为SiO2,厚度相应为t2,介电常数为

,外面一层介质为SiO2,厚度相应为t2,介电常数为 。下面我们研究使用这种复合电介质情况下的无规则电报信号杂音强度。

。下面我们研究使用这种复合电介质情况下的无规则电报信号杂音强度。

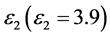

我们考虑内层绝缘层的介电常数为 ,厚度t1

= 1 nm,外层绝缘层选择厚度为2 nm,介电常数为3.9的SiO2(即

,厚度t1

= 1 nm,外层绝缘层选择厚度为2 nm,介电常数为3.9的SiO2(即 )。计算在复合介质中无缺陷电荷和存在缺陷电荷Q

= +1e时通过场效应管的电流I0和IQ。并计算由缺陷引起的电流相对变化值(IQ −

I0)/I0随栅极电压Vg的变化关系。为便于对比,我们也计算了在单一电介质SiO2和单一介电常数为40的介质中缺陷引起的无规则电报信号杂音。计算结果如图6所示。

)。计算在复合介质中无缺陷电荷和存在缺陷电荷Q

= +1e时通过场效应管的电流I0和IQ。并计算由缺陷引起的电流相对变化值(IQ −

I0)/I0随栅极电压Vg的变化关系。为便于对比,我们也计算了在单一电介质SiO2和单一介电常数为40的介质中缺陷引起的无规则电报信号杂音。计算结果如图6所示。

Figure 4. The amplitude of the RTS noise at the drain voltage of −50 mV due to a trapped charge of Q = +1e at the nanotube-oxide interface for different dielectric constants of 3.9 (black solid curve), 16 (red dashed curve), 30 (green dotdashed curve), 40 (blue double dot-dashed curve), and 80 (orange double dash-dotted curve), respectively. Panels (a) and (b) show the results for the 2 nm-thick gate dielectrics and those for the 1 nm-thick gate dielectrics, respectively

图4. 在Vd = −50 mV,一个带正电的缺陷电荷引起的杂音的幅度,对应于不同的介电常数分别为3.9(黑色实线),16(红色虚线),30(绿色点虚线),40(蓝色双点虚线),80(橘色双虚点线);(a) (b)分别表示介质厚度为2 nm和1 nm情况下的计算结果

Figure 5. Cross-sectional plots for a CNFET with composite gate dielectrics

图5. 复合介质层时的CNFET横截面图

Figure 6. (a) and (c) The current through CNFET without any impurity charge and the thickness of gate dielectric are 3 nm and 15 nm for different situation of composite constant (black solid curve), single dielectric constant SiO2 (green dotdashed curve) and 40 (red dashed curve); (b) and (d) The relative current reductions due to a trapped charge of Q = +1e at the nanotube-insulator interface for different gate dielectrics defined in panel (a) and (c)

图6. (a)和(c)表示绝缘层厚度分别为3 nm和15 nm,且在理想情况下(即在介质中无缺陷)通过CNFET的电流I0,实曲线为复合电介质的结果,点虚线为单一介质SiO2的结果,虚线为介电常数为40单一介质的结果;(b)和(d)表示由缺陷电荷引起的分别对应于(a)和(c)情形的电流相对变化量(IQ − I0)/I0

从图6(b)可以看出复合介质情况下,在内层介质厚度t1 = 1 nm时,电报信号杂音在启动阶段达到84%;从图6(d)可以看出在内层介质厚度增大到t1 = 13 nm时,杂音在启动阶段减小到49%,比3 nm厚情况下减小了35%。而绝缘层为15 nm厚的单层介电常数为40的电介质时,启动状态的电报信号杂音将近47%,比3 nm厚情况下增大了20%。对比图6(b)和图6(d)两种不同厚度的绝缘介质层,表明对于单层电介质,绝缘层越薄,杂音越小;而对于复合电介质时,在外层介质厚度不变,内层介质厚度变大(复合介质的总厚度变大)时,杂音减小。也就是说,使用复合介质层时介质厚度对杂音的影响与单层介质时完全不同。

那么,我们在制作碳纳米管场效应晶体管时可以选用复合电介质作为栅极氧化层,但是我们必须知道杂音对杂质离子位置的依赖关系。为此我们计算了内层介质介电常数 ,厚度t1

= 13 nm,外层介质介电常数

,厚度t1

= 13 nm,外层介质介电常数 ,厚度t2

= 2 nm这种情况下,一个带正电荷的杂质离子分别距离纳米管壁0.4 nm,3.4 nm,6.4 nm,10.4 nm以及14.4 nm时的无规则电报信号杂音。计算结果如图7所示

,厚度t2

= 2 nm这种情况下,一个带正电荷的杂质离子分别距离纳米管壁0.4 nm,3.4 nm,6.4 nm,10.4 nm以及14.4 nm时的无规则电报信号杂音。计算结果如图7所示

从图7很明显可以看出,不管是单层还是复合电介质情况,缺陷电荷离纳米管越远,电报信号杂音越小。比较图7(b)和图7(c),单层介质介电常数为40和复合电介质(其中内层介电常数为40,外层介电常数为3.9)这两种情况产生的电报信号杂音差别不大。

4. 结果与讨论

运用紧束缚非平衡格林函数方法计算通过碳纳米管场效应晶体管中的电流。计算结果表明,单层介质中,介质层越厚,产生的无规则电报信号杂音越大。但是,如果我们把栅极氧化层采用复合电介质,

Figure 7. The relative current reduction due to a charge of Q= +1e at a distance of 0.4 nm (black solid curve), 3.4 nm (red dashed curve), 6.4 nm (green dash-dotted curve), 10.4 nm (blue double dot-dashed curve), and 14.4 nm (orange double dash-dotted curve) from nanotube wall. In panels (a) and (b), the dielectric constants of the gate oxides are 3.9 and 40, respectively. Gate oxides in panels (a) and (b) are both 15 nm thick. Panel (c) shows results for a CNFET with composite insulators, where the inner insulator has a dielectric constant of 40 and the outer insulator is SiO2

图7. 一个缺陷电荷距纳米管壁的距离依次为0.4 nm(黑色实线),3.4 nm(红色虚线),6.4 nm(绿色虚点线),10.4 nm(蓝色双点虚线),14.4 nm(橘色双虚点线(时的电流相对变化值。(a)和(b) 栅极为单一电介质,介电常数分别为为3.9和40;(c) 栅极为复合电介质,内层介电常数为40,外层介电常数为3.9

其中内层介质使用介电常数大的绝缘材料,而外层用介电常数较小的二氧化硅。发现在外介质层厚度不变的情况下,内介质层越厚(相应总厚度也越大),产生的杂音反而越小,这与单层电介质情况完全不同。在此基础了,也发现单层和复合电介质的情况,缺陷电荷离纳米管越远,产生的电报信号杂音越小。计算结果能为设计最佳的碳纳米管场效应晶体管提供了一定的理论依据。

致 谢

感谢国家自然科学基金资助项目(项目编号:50902110)。

参考文献 (References)

- [1] Iijima, S. (1991) Helical microtubules of graphitic carbon. Nature, 354, 56-58.

- [2] Javey, A., Guo, J., Wang, Q., et al. (2003) Ballistic carbon nanotubes field-effect transistors. Nature, 424, 654-657.

- [3] Heinzeetal, S. (2002) Carbon nanotubes as schottky barrier transistors. Physical Review Letters, 89, Article ID: 106801.

- [4] Collins, P.G., Fuhrer, M.S. and Zettl, A. (2000) 1/f noise in carbon nanotubes. Applied Physics Letters, 76, 894-896.

- [5] Chan, J., Burke, B., Evans, K., et al. (2009) Reversal of current blockade through multiple trap correlations. Physical Review B, 80, Article ID: 033402.

- [6] Liu, F., Bao, M.Q., Kim, H.-J., Wang, K.L., et al. (2005) Giant random telegraph signals in the carbon nanotubes as a single defect probe. Applied Physics Letters, 86, Article ID: 163102.

- [7] Lee, J.-W., Lee, B.H., Shin, H., et al. (2010) Investigation of random telegraph noise in gate-induced drain leakage and gate edge direct tunneling currents of high-k MOSFETs. IEEE, 57, 913-918.

- [8] Neophytou, N., Kienle, D., et al. (2006) Influence of defects on nanotube transistor performance. Applied Physics Letters, 88, Article ID: 242106.

- [9] Chan, J., Burke, B., Evans, K., Williams, K.A., Vasudevan, S., Liu, M., Campbell, J. and Ghos, A.W. (2009) Reversal of current blockade in nanotube-based field effect transistors through multiple trap correlations. Physical Review B, 80, Article ID: 033402.

- [10] Liu, F., Wang, K.L., et al. (2006) Random telegraph signals and noise behaviors in carbon nanotube transistors. Applied Physics Letters, 89, Article ID: 243101.

- [11] Choi, C. and Choi, R. (2012) The electrical and structural properties of HfO2/SrTiO3 stacked gate dielectric with TiN metal gate electrode. Thin Solid Films, 521, 42-44.

- [12] Campbell, S.A., Kim, H.-S. et al. (1999) Titanium dioxide(TiO2)-based gate insulators. IEEE Electron Device Letters, 43, 383-392.

- [13] Lee, J.-W., Lee, B.H., Shin, H. and Lee, J.-H. (2010) Investigation of random telegraph noise in gate-induced drain leakage and gate edge direct tunneling currents of high-k MOSFETs. IEEE Transactions on Electron Devices, 57, 913- 918.

- [14] Wang, N.-P., Heinze, S., et al. (2007) Random-telegraph-signal noise and device variability in ballistic nanotube transistors. Nano Letters, 7, 910-913.

- [15] Datta, S. (1995) Electronic transport in mesoscopic systems. Cambridge University Press, Cambridge.

- [16] Brandbyge, M., Mozos, J.-L., et al. (2002) Density-functional method for nonequilibrium electron transport. Physical Review B, 65, Article ID: 165401.

- [17] Svizhenko, A., Anantram, M.P., et al. (2002) Two dimensional quantum mechanical modeling of nanotransistors. Journal of Applied Physics, 91, 2343-2354.

- [18] Heinze, S., Wang, N.-P. and Tersoff, J. (2005) Electromigration forces on ions in carbon nanotubes. Physical Review Letters, 95, Article ID: 186802.

- [19] Dutta, P. and Horn, P.M. (1981) Low-frequency fluctuations in solids: 1/f noise. Reviews of Modern Physics, 53, 497-499.

- [20] Weissman, M.B. (1988) 1/f noise and other slow nonexponential kinetics in condensed matter, Reviews of Modern Physics, 60, 537-539.