Hans Journal of Wireless Communications

Vol.

09

No.

01

(

2019

), Article ID:

28873

,

6

pages

10.12677/HJWC.2019.91003

Integrated All-Optical Programmable Logic Array Based on Cross Gain Modulation

Weiyue Zhang1, Wenchan Dong2

1No. 1 Middle School Affiliated to Central China Normal University, Wuhan Hubei

2School of Optics and Electronic Information, Huazhong University of Science and Technology, Wuhan Hubei

Received: Jan. 24th, 2019; accepted: Feb. 8th, 2019; published: Feb. 15th, 2019

ABSTRACT

We propose and experimentally demonstrate an integrated all-optical PLA at the operation speed of 40 Gb/s based on semiconductor optical amplifiers (SOAs). Different all-optical minterms are generated by using cross gain modulation of SOAs, then we use SOAs to select out the appropriate CLUs by changing the working states, and reconfigurable logic functions can be output directly.

Keywords:All-Optical Logic, Programmable Logic Array, Semiconductor Optical Amplifier

基于交叉增益调制的集成全光可编程逻辑阵列研究

张惟玥1,董文婵2

1华中师范大学附属第一中学,湖北 武汉

2华中科技大学光学与电子信息学院,湖北 武汉

收稿日期:2019年1月24日;录用日期:2019年2月8日;发布日期:2019年2月15日

摘 要

我们提出并实验验证了基于半导体光放大器实现调制速率为40 Gbit/s的集成全光可编程逻辑阵列。利用半导体光放大器中交叉增益调制效应实现不同全光最小项,再利用半导体光放大器的开关特性实现对最小项的选择,从而实现基于最小项的不同组合逻辑功能。

关键词 :全光逻辑,可编程逻辑阵列,半导体光放大器

Copyright © 2019 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

1. 引言

全光信号处理可以避免光电光转换过程从而降低功耗提高系统容量,而光计算又是全光信号处理中的难点技术之一 [1] 。在过去的几十年里,除了全光与门、全光或门、全光或非门等基础逻辑门被广泛研究 [2] [3] ,全光复杂逻辑器件,例如全加器、全减器、半加器、编码器、译码器、可编程逻辑阵列等也引起了研究者的关注 [4] [5] 。其中,全光可编程逻辑阵列是一种典型的可重构复杂逻辑器件 [6] 。全光可编程逻辑阵列不仅能够通过可编程选择满足用户自定义从而大大提高逻辑功能输出的灵活性,而且也能够通过多个可编程控制点的设置来使输出逻辑结果多样化,因此得到了广泛研究。

基础逻辑门以及包括全光可编程逻辑阵列在内的复杂逻辑器件主要是基于非线性器件以及相应的非线性效应来实现。非线性器件主要包括半导体光放大器、高非线性光纤、硅波导等,而非线性效应主要包括四波混频、交叉增益调制、交叉相位调制等。其中高非线性光纤作为一种无源材料 [7] ,具有非线性响应快(飞秒量级)、损耗小、无噪声、非线性累积效应大等显著优势,是一种具有竞争力的全光信号处理器件,但存在体积大难以集成的劣势。半导体光放大器是一种体积小、易于与其他器件集成的有源非线性器件,并且可以实现丰富的非线性效应,是未来集成时代作为非线性介质很有潜力的候选者之一。而硅波导是体积更小的集成器件,也是全光信号处理中的常用器件。由于半导体光放大器是有源器件,不仅可以作为非线性介质来实现全光最小项,还可以利用开关特性来实现相应最小项的选择,因此本文提出并实验验证了基于半导体光放大器实现全光可编程逻辑阵列的方案。通过利用半导体光放大器中交叉增益调制效应实现不同全光最小项,再利用半导体光放大器的开关特性实现对最小项的选择,从而实现基于最小项的不同组合逻辑功能,验证全光可编程逻辑阵列功能。本方案实现集成可编程逻辑阵列将为全光复杂逻辑器件从分立方案走向集成方案迈出重要的一步,进一步促进全光全加器、全减器、编码器等器件实现集成方案,推动利用全光方法来处理原本信息就加载在光上的应用场景,有潜力进一步结合新材料新结构来实现低功耗方案从而解决实际运算问题。

2. 实验方案

我们基于磷化铟平台开发了全光可编程逻辑阵列集成芯片,该芯片工作的结构图如图1所示,包括输入光路,标准逻辑单元(CLUs)阵列和开关阵列。输入光路由延时干涉仪(DI)构成,用于对差分相移键控(DPSK)信号进行预编码。通过将差分相移键控信号上的相位信息转换到幅度上,从而产生互补码流作为逻辑运算的输入信号 [8] 。腔长较长的半导体光放大器(SOA)是作为实现交叉增益调制(XGM)的非线性介质,用于产生不同的标准逻辑单元信号,也即最小项。腔长较短的半导体光放大器是用来选择标准逻辑单元信号的通断。

Figure 1. Schematic diagram of the integrated optical PLA in XGM mode, OC: optical coupler, DI: delayed interferometer, SOA: semiconductor optical amplifier, TBPF: tunable bandpass filter

图1. XGM工作模式下的结构图,OC:光耦合器,DI:延时干涉仪,SOA:半导体光放大器,TBPF:可调带通滤波器

该全光可编程逻辑阵列的工作原理如图2所示。输入光路中当两个DPSK信号的波长分别对准DI传输谱的波峰或者波谷时,两个DPSK可以被同时解调产生两组互补码流。当我们定义DPSK信号对准DI传输谱波峰时,DI产生输入信号原码,那么当对准DI波谷时,DI则产生输入信号反码。因此,当两个DPSK信号同时对准DI的两个不同波峰时,在DI一个输出端口产生输入信号原码A和B的功率之和,那么在另一个端口则产生输入信号反码 和 的功率之和。同理,当我们将B信号的波长移动半个DI的FSR,也即将B信号由对准波峰改为对准波谷,那么DI的一个端口将输出A和 的功率之和,而另一个端口将输出 和B的功率之和。泵浦光 和探测光 一起进入SOA1中,经过XGM作用,探测光幅度上会携带 的逻辑信息。 、 和 这三路信号从SOA1 输出后进入SOA3,当SOA3处于ON状态时,三路信号会一起输出到片外,并经过片外的可调带通滤波器经转换光滤出,也即产生 信号;而当SOA3处于OFF状态时,三路信号会被SOA3损耗,输出端的可调带通滤波器(TBPF)将不能滤出 信号。同理,两路泵浦光A和B一起进入SOA2中,经过XGM作用,探测光幅度上会携带 的逻辑信息。A、B和 这三路信号从SOA2 输出后进入SOA4,当SOA4处于ON状态时,三路信号会一起输出到片外,并经过片外的可调带通滤波器经转换光滤出,也即产生 信号;而当SOA4处于OFF状态时,三路信号会被SOA4损耗,输出端的TBPF将不能滤出 信号。因此,当两个开关SOA3 和SOA4中的一个为ON状态时, 或者 将会输出;而当两个开关同时为ON状态时,将会输出这两个CLUs的耦合结果,也即是XOR。如前所述,当我们改变B信号波长,使DI的一个端口输出A和 的功率之和,而另一个端口输出 和B的功率之和,那么此时改变两个开关SOA3和SOA4的工作状态,则可以分别输出AB、 和XNOR三种不同逻辑功能。

Figure 2. XGM Operational principle of (a) Input circuit, (b) CLUs array, (c) Switches array

图2. XGM工作模式下工作原理,(a) 输入光路,(b) CLUs阵列,(c) 开关阵列

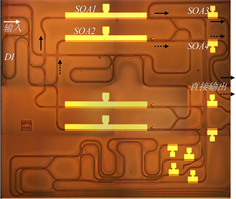

图3为我们开发的磷化铟单片集成可编程逻辑阵列芯片显微照片,两个不同波长的DPSK信号经过耦合器耦合之后输入到片上的DI,经过DI解调之后,DI一个端口输出A和B的功率之和,另一个端口输出 和 的功率之和。高功率的A和 作为泵浦光,而低功率的B和 则作为探测光。沿着图3所示的实线箭头顺序, 和 进入到SOA1中,经过XGM调制作用探测光产生了携带 逻辑信息的转换光。经过SOA3和一个2 ´ 2 MMI, 、 和 三路信号被输出到片外。同理,沿着图3所示的虚线箭头顺序,A和B进入到SOA2中,经过FWM过程产生了携带 逻辑信息的转换光。经过SOA4和一个2 ´ 2 MMI,A、B和 三路信号被输出到片外。通过控制SOA3和SOA4,我们可以根据需要输出不同的逻辑功能。

Figure 3. Micrograph of the integrated optical PLA based on SOA

图3. 全光可编程逻辑阵列显微照片

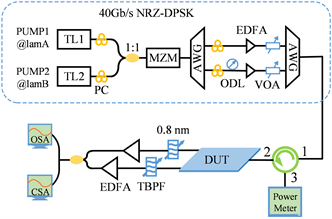

图4是实验装置图。将两个可调谐激光器输出的两路连续光分别经过偏振控制器(PC)和1:1耦合器之后进入马赫泽德调制器,调制成40 Gb/s的非归零DPSK信号。我们选择两路连续光波长对准DI的波峰或者波谷,DPSK信号( )波长为1555.66 nm,而DPSK信号( )波长为1549.36或者1549.20 nm。将调制后的两路DPSK信号输入到自由光谱范围为1.6 nm的阵列波导光栅进行解复用,这两路信号分别经过偏振控制器和掺铒光纤放大器之后功率被放大到19 dBm。光延时线是为了将这两路泵浦信号解相干,可调光衰减器是为了调整泵浦光的功率。光环行器是为了隔离片上的反射光,也用于监控耦合效率。输入到片上的DPSK( )功率为17.3 dBm,而DPSK( )功率为2.8 dBm。

Figure 4. Experimental setup for testing the performance of an optical PLA. TL: tunable laser; PC: polarization controller; MZM: Mach-Zehnder modulator; AWG: Arrayed waveguide gratings; ODL: optical delay line; EDFA: erbium-doped fiber amplifier; VOA: variable optical attenuator; TBPF: tunable bandpass filter; CSA: communication signal analyzer; OSA: optical spectrum analyzer; DUT: device under test

图4. 实验装置图,TL:可调谐激光器,PC:偏振控制器,MZM:马赫泽德调制器,EDFA:掺铒光纤放大器,AWG:阵列波导光栅,DI:延时干涉仪,ODL:光延时线,HNLF:高非线性光纤,VOA:可调光衰减器,DUT:待测器件,TBPF:可调带通滤波器,OSA:光谱分析仪,CSA:通信信号分析仪

3. 实验结果

表1是该全光可编程逻辑阵列不同参数下对应可以输出的可重构逻辑功能。当DPSK( )波长为1549.36 nm时,通过调节SOA3和SOA4的工作状态,可以切换输出这几个逻辑功能, 、 或XOR。而当DPSK( )波长为1549.20 nm时,通过调节SOA3和SOA4的工作状态,可以切换输出这几个逻辑功能,AB、 或XNOR。图5(a)和图5(b)是输出的全套CLUs、XOR和XNOR的时域波形。这些逻辑结果的码流都正确而且清晰,输出结果的逻辑电平也易于辨认。对于CLUs波形的逻辑“0”不平,主要是由于原始DPSK信号存在幅度抖动。

Table 1. Different outputs of optical PLA based on different parameters

表1. 不同参数下该全光可编程逻辑阵列的不同输出结果

Figure 5. Measured temporal waveforms of the output logic functions when DPSK ( ) is at, (a) 1549.36 nm; (b) 1549.2 nm

图5. 输出逻辑功能的时域波形,当DPSK( )波长为,(a) 1549.36 nm;(b) 1549.2 nm

4. 结论

本文实验研究了基于半导体光放大器实现调制速率为40 Gbit/s的全光可编程逻辑阵列。通过利用延时干涉仪对差分相移键控信号的解调作用实现输入光路,并同时利用半导体光放大器的交叉增益调制效应和开关特性分别实现标准逻辑单元阵列和开关阵列,从而实现基于最小项的不同组合逻辑功能,实现全光可编程逻辑阵列。

致谢

光逻辑阵列相关课题得到国家自然科学基金重点国际合作项目的资助。

文章引用

张惟玥,董文婵. 基于交叉增益调制的集成全光可编程逻辑阵列研究

Integrated All-Optical Programmable Logic Array Based on Cross Gain Modulation[J]. 无线通信, 2019, 09(01): 14-19. https://doi.org/10.12677/HJWC.2019.91003

参考文献

- 1. Willner, S.K.A.E., Chitgarha, M.R. and Yilmaz, O.F. (2014) All-Optical Signal Processing. Journal of Lightwave Technology, 32, 660-680.

https://doi.org/10.1109/JLT.2013.2287219 - 2. 王文睿, 于晋龙, 罗俊, 韩丙辰, 郭精忠, 王菊, 刘毅, 杨恩泽. 基于非线性光纤环镜的40Gb/s可重构光逻辑门[J]. 光学学报, 2012(32): 45-50.

- 3. 董建绩, 张新亮, 王阳, 黄德修. 基于单个半导体光放大器的高速多功能逻辑门[J]. 物理学报, 2008(4): 38.

- 4. Zhang, Y., Lei, L., Dong, J. and Zhang, X. (2011) 40 Gbit/s Four-Input Photonic Digital Priority Encoder Employing Three Parallel Semiconductor Optical Amplifiers. Electronics Letters, 47, 872-873.

https://doi.org/10.1049/el.2011.1234 - 5. Zhang, Y., Lei, L., Dong, J. and Zhang, X. (2011) 40 Gbit/s 2-to-1 Photonic Data Selector via XGM and FWM in Two SOAs. Electronics Letters, 47, 811-813.

https://doi.org/10.1049/el.2011.1235 - 6. Lei, L., Dong, J., Yu, Y., Tan, S. and Zhang, X. (2012) All-Optical Canonical Logic Units-Based Programmable Logic Array (CLUs-PLA) Using Semiconductor Optical Amplifiers. Journal of Lightwave Technology, 30, 3532-3539.

https://doi.org/10.1109/JLT.2012.2218575 - 7. 王文睿, 等. 基于高非线性光纤汇总非线性偏振旋转效应的全光逻辑门研究[J]. 物理学报, 2014(61): 084214.

- 8. Xu, J., Zhang, X., Zhang, Y., Dong, J., Liu, D. and Huang, D. (2009) Reconfigurable All-Optical Logic Gates for Multi-Input Differential Phase-Shift Keying Signals: Design and Experiments. Journal of Lightwave Technology, 27, 5268-5275.