Optoelectronics

Vol.4 No.03(2014), Article

ID:14016,9

pages

DOI:10.12677/OE.2014.43006

Fabrication Process of Silica Film for Optical Waveguides

1Shenzhen Optical Fiber Sensing Engineering Technology R&D Center, Shenzhen

2T&S Communications Co. Ltd., Shenzhen

Email: *petter.wu@china-tscom.com

Copyright © 2014 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received: Jul. 23rd, 2014; revised: Jul. 30th, 2014; accepted: Aug. 8th, 2014

ABSTRACT

SiO2 based planar waveguide circuit device has found increasing application in optical communication and optical sensing. The deposition of SiO2 thin film is the basis of fabricating PLC and integrated devices. PECVD (Plasma enhanced Chemical Vapor Deposition) and FHD (Flame Hydrolysis Deposition) are the typical techniques for depositing SiO2 thin film. In this paper, the influence of process parameters on thin film performance is discussed, showing that the hybrid process of PECVD and FHD is the most competitive way to fabricate PLC devices on SiO2 substrate.

Keywords:Planar Lightwave Circuits, Silica Film, PECVD, FHD

二氧化硅光波导膜材料的制备工艺

吴金东1,2*,黄 舒1,2,胡海鑫1,2,丁纲筋1,2,肖湘杰1,2

1深圳市光纤传感工程技术研究开发中心,深圳

2深圳太辰光通信股份有限公司,深圳

Email: *petter.wu@china-tscom.com

收稿日期:2014年7月23日;修回日期:2014年7月30日;录用日期:2014年8月8日

摘 要

二氧化硅(SiO2)平面光波导器件在光通信和光传感的应用日益广泛,制备SiO2膜材料是平面光波导及其集成器件制作的基础。等离子增强化学气相沉积(Plasma Enhanced Chemical Vapor Deposition, PECVD)和火焰水解沉积(Flame Hydrolysis Deposition, FHD)工艺是制备SiO2厚膜的典型方法, 本文分析总结了制备工艺参数对膜层性能的影响,说明PECVD + FHD混合工艺是SiO2型PLC器件最具竞争性的制作方法。

关键词

平面光波导,二氧化硅膜,等离子增强化学气相沉积,火焰水解沉积

1. 引言

平面光波导(Planar Lightwave Circuit, PLC)是采用半导体工艺将光学元件集成到一块芯片上,实现对光信号复杂控制处理功能的光器件技术[1] [2] ,已经大量应用的PLC器件有光分路器(Splitter)、阵列波导光栅(AWG)、光开关(Switch)、可调光衰减器(VOA)、光波导模式光谱(OWLS)传感器等。目前,无源器件与有源、MEMS融合是PLC技术的重要发展方向,可开发出新型的多功能集成器件[3] ,如VMUX (VOA + AWG)、WSS (Switch + AWG)、加速度计、压力传感器、微型麦克风(智能手机)等。PLC不但能实现光电器件集成化、规模化、小型化,而且具有性能稳定、适于规模化生产、成本低等优势。

通常,Si基PLC为四层结构(如图1所示):Si衬底、缓冲层(下包层)、芯层和覆盖层(上包层)。SiO2基PLC为三层结构,SiO2即是基底,也充当下包层,多用来制作PLC分路器。可制作PLC的材料有二氧化硅(SiO2)、铌酸锂(LiNbO3)、III-V族半导体化合物(如InP,GaAs)、绝缘体上硅(Silicon-on-Insulator, SOI)、氮氧化硅(SiON)、玻璃和聚合物(Polymer)等,其中SiO2、InP、GaAs、SOI、SiON和Polymer波导以半导体刻蚀工艺制作,LiNbO3和玻璃波导以离子扩散工艺制作。光波导芯层材料传输光信号,要求传输损耗低、厚度尺寸和折射率均匀一致、双折射小,且与包层的界面光滑平整。PLC还要求包层足够厚,如0.34%~0.75%Δ光波导需要上下包层厚度达到12~20 um,以保证传输的光波不会被泄漏;其次包层材料的温度特性与芯层差异要小,以减小波导中产生应力双折射而影响性能,如AWG偏振相关性和中心波长温度敏感性;此外包层材料应具有良好的流动性,因为光波导芯层已被刻蚀出台阶和沟槽状,这样才能完全填充芯层与包层的空隙达到紧密的包裹效果。通常在SiO2材料中需掺入一定的B2O3、P2O5和GeO2等,调节SiO2的折射率、热膨胀系数和软化温度。

Figure 1. Cross section of PLC

图1. PLC的层结构截面示意图

2. PECVD + FHD混合工艺

SiO2波导PLC器件,需要在Si/SiO2和SiO2基片上制备折射率和厚度不同的SiO2膜材料,以形成SiO2波导的芯层和上包层。SiO2膜材料的制作方法有多种,等离子增强化学气相沉积法(PECVD)[4] [5] 和火焰水解沉积法(FHD) [6] [7] 应用最为广泛,两种方法各有优劣。PECVD的膜层生长速率较慢,通常为100~300 nm/min,容易对膜层厚度、折射率和界面光滑度精确控制[8] 。PECVD每沉积几微米厚度膜层,即需要对沉积腔体进行清理[9] ,如制备厚度20微米以上膜层,需要多次沉积和腔体清洗过程,很费时间。通常PECVD设备昂贵,采用全PECVD工艺制作PLC器件[10] ,往往生产效率与制作成本处于劣势。FHD比PECVD更早用于PLC器件的制作[11] [12] ,该方法能较快地生长厚达几十甚至上百微米的SiO2膜层材料,对台阶的覆盖比PECVD更好[13] ,但对膜层厚度均匀性的控制相对更难。由于FHD设备投资相对小,在制作厚度较大的包层方面具有效率高成本低的优势。可见,采用PECVD制作芯层,FHD制作包层的混合工艺是PLC器件最具竞争性的制作方法,本文着重介绍两种技术的应用。

3. PECVD制备芯层

PECVD利用辉光放电,在高频电场下使稀薄气体电离产生等离子体,触发并维持淀积所需的化学反应,从而可以在较低温度下实现SiO2沉积。PECVD制备的SiO2膜层多孔疏松,含有大密度的O-H,N-O,Si-H键,影响膜层的稳定性和光学性能(折射率和红外吸收)[14] [15] ,如Si-H和O-H在630、1400 nm波长的吸收峰是膜层损耗增加[16] 。必须在N2或O2气氛中进行退火处理,使膜层致密化,消除H键和残余应力,才能满足光传输的需要。退火处理温度和时间对膜层性能有一定影响,800℃退火后通常O-H吸收消失,而N-H、Si-H的吸收需要在1100℃退火才能减弱,并伴随着损耗大幅度降低。

GeO2-SiO2具有优异的光学特性(其损耗可降至0.02 dB/cm),是PLC器件运用最为广泛的光波导芯层材料。PECVD制备GeO2-SiO2膜材料的工艺气体通常为SiH4、10%GeH4 (以Ar为稀释气体)和N2O[17] 。沉积腔的压强、温度、气体流速和流速比率、射频功率等是影响膜材料生长速率、膜层结构、折射率和粗糙度的主要变量[18] 。本文讨论生长温度为320℃,气体流量比10%GeH4:SiH4:N2O为20:17:2000 sccm,射频输入功率为700 W,沉积腔压强为300 mTorr的条件下,10%GeH4流量、沉积腔压强和射频输入功率对膜材料生长速率、膜层结构、折射率和粗糙度的影响。

如图2,GeO2-SiO2膜材料的折射率随10% GeH4流量的呈线性变化,GeO2-SiO2膜的折射率随GeH4流量线性增大,说明可以通过精确控制GeH4的流量来调节膜层的折射率。

Figure 2. Refractive index versus GeH4 flow rate (GeH4/Ar = 10/90)

图2. 折射率随GeH4流量的变化(GeH4/Ar = 10/90)

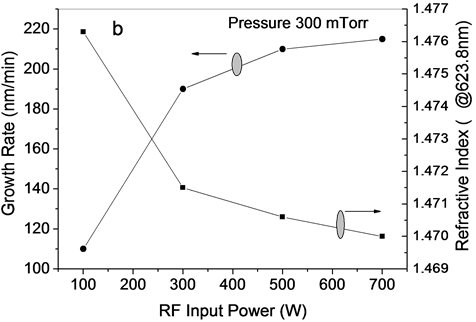

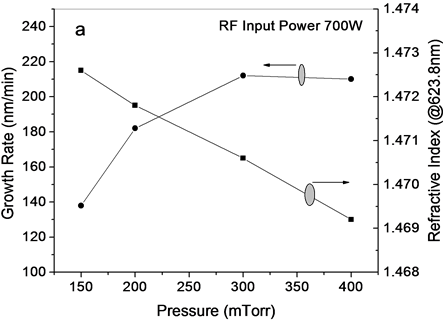

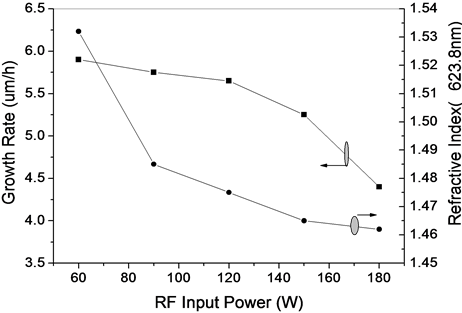

沉积腔压强对薄膜的生长速率,表面粗糙度,折射率的影响分别如图3(a)和图4所示。如图3(a)所示,随着压力的增加,膜生长速率快速增加,在300 mTorr时达到220 um/min,然后增幅变缓趋于饱和。因为随着压强增大,更多反应的生成物到达基底表面,膜的生长速度增加。由于速度增加,表面沉积SiO2的颗粒增大,表面粗糙度也变大(如图4),膜层的致密性和均匀性变差,针孔缺陷和残余应力也增加,达到某种程度时这些问题在退火中不容易消除。因此,采用较小生长速度是降低损耗获得高质量芯层材料的关键。从图3(a)可知,随压强增大膜层折射率逐渐减小。

射频输入功率对薄膜的生长速率,表面粗糙度,折射率的影响分别如图3(b)和图4所示。图3(b)表明随功率的增加,薄膜的生长速率先迅速增加,然后增加逐渐变缓,趋于稳定。其变化的原因是:功率越大,提供反应活性粒子的能量越高,增大了相互反应的几率,从而增加了淀积速率;而随着功率增加到一定值,淀积速率增幅明显变缓,这是由于参与反应的活性粒子的数目随功率增加逐渐趋于饱和,使得淀积速率也逐渐趋于饱和最后稳定。同理,表面粗糙度(图4)随着射频输入功率增加而变大。而折射率(图3(b))则相反,随着射频输入功率增加而减小。

PLC集成度增高要求光波导的尺寸更小,其弯曲半径更小。表1是光波导设计Δ%、厚度、宽度与

Figure 3. Influence of (a) chamber pressure (b) RF power on thin film growth rate and refractive index

图3. (a)沉积腔压力(b)射频输入功率对薄膜生长速率和折射率影响

Figure 4. Influence of chamber pressure and RF power on surface roughness

图4. 沉积腔压力和射频输入功率对表面粗糙度的影响

性能的对照表,芯层Δ增加对于大通道AWG,VMUX和环形振荡滤波器等,具有十分关键的意义。

Ge:SiO2折射率随GeH4流量呈线性变化,制备Δ% = 1.5,2,3,3.5,4%芯层膜所采用典型沉积条件如下:5%SiH4 = 400,356,180,140,110 sccm,2%GeH4 = 198,250,250,250,250 sccm,N2O:N2 = 2000:500 sccm,射频输入功率462 W,压力503 mtorr,温度的300℃,膜层的退火温度为1100℃(O2气氛)。

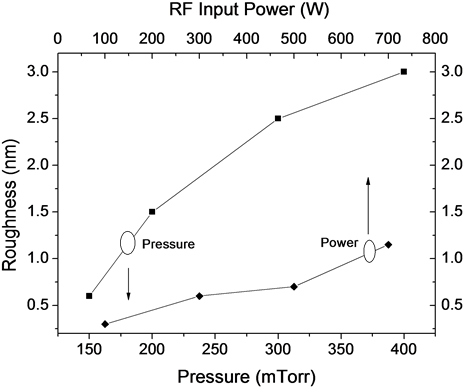

除Ge:SiO2外,SiON折射率达1.46~1.53,也可制作高折射率芯层材料[19] 。在生长温度320℃,气体流量比10% SiH4/(N2O + N2)为0.17,沉积腔压强900 mTorr的沉积条件下,射频输入功率对PECVD薄膜的生长速率,折射率的影响如图5所示,膜层的退火温度为1100℃(N2气氛)。由于N-H键在1510 nm附近有强吸收[20] ,图6是3.5%Δ的Ge:SiO2和SiON直波导损耗谱,SiON芯层的损耗大于1 dB/cm,影响1550通信窗口应用性能。而Ge:SiO2中没有N-H且O-H含量较低,在1480~1620 nm波长范围损耗约为0.1 dB/cm,较SiON芯层低得多。另外SiON比Si的热膨胀小,易导致热应力双折射。近来,文献[21] [22] 报道低损耗Si3N4膜材料的制作工艺,这些成果为PLC增加新的制作材料。

4. FHD制备包层

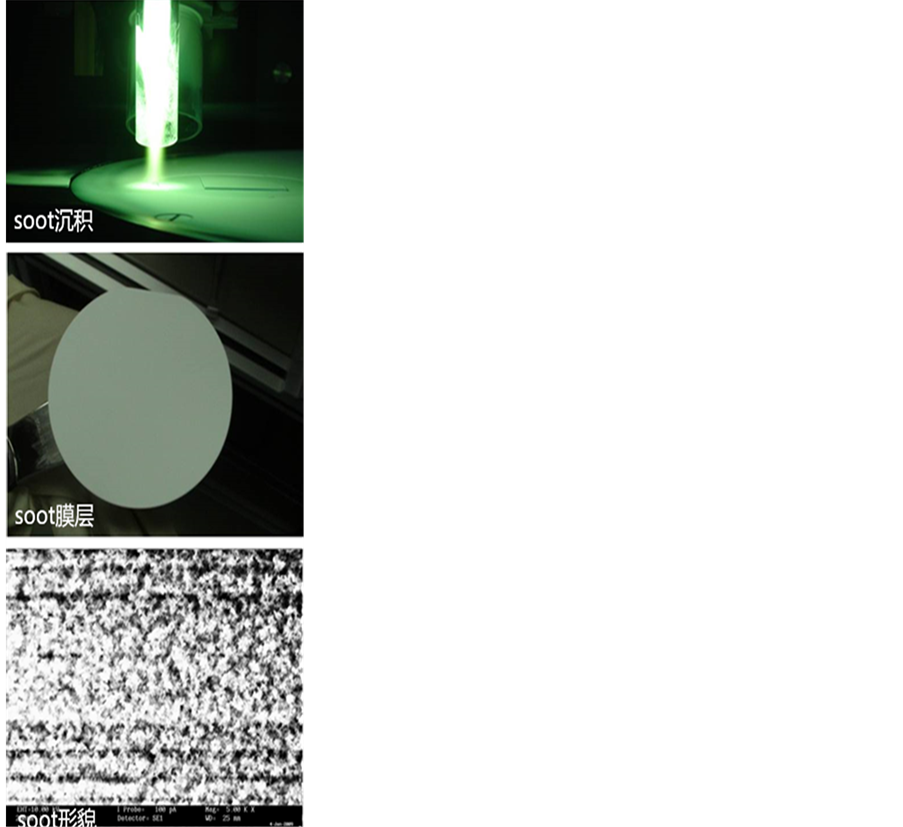

火焰水解沉积工艺如图7所示。SiCl4、GeCl4、BCl3和POCl3等工艺气体经充分混合后送入氢氧焰喷枪中。将已制作光波导图案的PLC晶圆片放在匀速旋转的转台上,氢氧焰喷枪沿转台轴向来回移动,喷

表1. 光波导设计参数:Δ%、厚度、宽度与性能

Figure 5. Influence of RF power on SiON growth rate and refractive index

图5. 射频输入功率对SiON生长速率和折射率的影响

Figure 6. Loss spectrum of SiON and Ge doped SiO2 straight waveguide (3.5%Δ)

图6. SiON与Ge:SiO2直波导(3.5%Δ)的损耗谱

Figure 7. FHD process

图7. 火焰水解沉积工艺

枪移动速度随喷枪位置变化。SiCl4、GeCl4、BCl3和POCl3气体在氢氧焰中水解产生的微细粉末沉积到基片表面,形成一层疏松的粉末层(图7)。将淀积了多孔粉末层的晶圆片送入高温炉中,经过1200℃以上高温烧结,多孔粉末致密化转变成透明的SiO2玻璃[23] 。

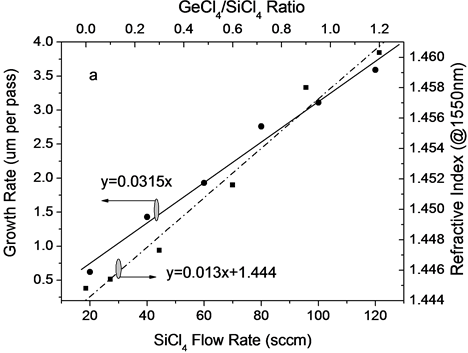

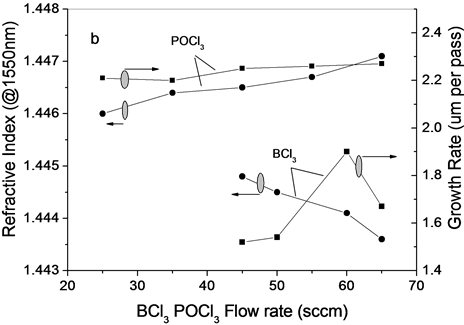

FHD沉积工艺参数见表2。火焰沉积温度由H2:O2比例和流量,以及稀释气体Ar决定,沉积温度约为550℃。SiO2膜层厚度主要由SiCl4流量大小决定,并喷灯移动、排气管距离等因素影响[24] 。每步沉

积厚度随SiCl4流量的变化,膜层折射率与GeCl4/SiCl4比如图8(a)所示。

GeCl4和POCl3、BCl3流量对SiO2膜层折射率影响如图8,可以看出,在一定气体流量范围内,膜层折射率随掺杂气体流量变化基本呈线性关系,对于Ge和P掺杂折射率单调增加,对于B掺杂折射率单调降低,在Ge、P、B掺杂同时存在时,膜层折射率可以认为是几种掺杂效应叠加的结果,通过改变沉积时B、P和Ge的流量可以实现上包层折射率的匹配。

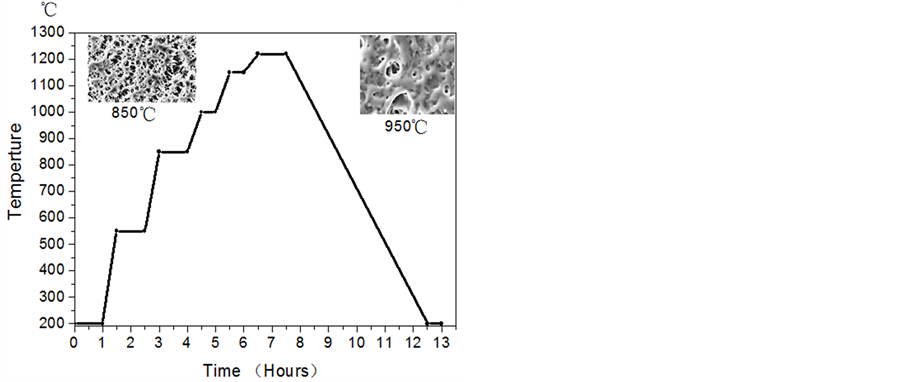

多孔SiO2粉末层的烧结致密机理是粘性烧结(viscous sintering),即SiO2微小颗粒在表面张力作用下引起粘性流动或塑性流动的结果。在SiCl4源气体中掺入GeCl4、BCl3和POCl3,可以大幅度降膜层玻璃的软化点,增加膜层流动性消除光波导旁边的空洞。由于烧结升温曲线对于透明膜层的质量有较大影响,通常烧结过程按照图9的温度曲线逐步升温至1200℃以上,保温2 h后自然降至室温。直接将SiO2粉末层升温到1200℃以上,烧结致密反应进行过快,容易致使封闭气孔来不及排除,产生气泡、裂纹等缺陷,图9显示烧结前不同温度下SiO2粉末层形貌,说明烧结升温过程对于消除空洞缺陷得到透明包层至关重要。SiO2粉末层的烧结致密需配以气体流量为He:O2 = 2:1的混合气体为烧结气氛,因为He的扩撒系数大,容易排除封闭气孔,O2可以消除SiO2玻璃结构中的氧空位,SiO2−x + xO → SiO2。此外,提高B、P 流量降低Tp,有利于膜层回流填充,消除光波导边缘的空洞,上包层台阶覆盖的界面图形如图10所示,表面光滑平整,台阶的覆盖性和覆盖平坦度都较好。采用PECVD + FHD制备1 × 16 PLC分路器芯片(如图10(c)),在波长范围1260~1650 nm,测试其插入损耗≤13 dB,偏振相关损耗≤0.2 dB,均匀性≤0.8 dB,均符合PLC分路器芯片的产品标准,达到实用化水平。如进一步优化工艺与提高良品率,可以满足大批量生产的需要。

表2. FHD法制备SiO2膜层的工艺参数与结果

Figure 8. Influence of SiCl4, GeCl4, POCl3, BCl3 on SiO2 refractive index and growth rate

图8. SiCl4、GeCl4、POCl3、BCl3流量对SiO2膜层折射率,生长速率的影响

Figure 9. Typical SiO2 soot sintering curve and appearance (850˚C, 950˚C)

图9. SiO2粉末层烧结典型温度曲线与形貌(850℃, 950℃)

5. 总结

制备SiO2膜材料是制作PLC器件的基础,应用最为普遍的方法是PECVD和FHD工艺,两种方法

Figure 10. FHD cladding layer appearance: (a) hollow on side of waveguide (b) cladding properly covered (c) 1 × 16 PLC splitter waveguide pattern

图10. FHD上包层形貌(a)波导测空洞,(b)上包层覆盖完全,(c) 1 × 16 PLC分路器波导图案

在制作不种特性的SiO2膜上各有优势。PECVD是一种低温沉积工艺,成膜速率相对慢,具有可精确控制膜层折射率和厚度,生成的膜层均匀且结构致密等优点,但设备昂贵,适合制备厚度较小的波导芯层。FHD具有沉积速率快,成膜效率高,设备简单和易于操作等优点,但是它需要在1200℃以上高温烧结玻璃化,容易造成基底变形,适合制作膜层较厚的包层。PECVD + FHD的混合工艺是SiO2型PLC器件的最具竞争性的制作方法。

参考文献 (References)

- [1] Doerr, C.R. and Okamoto, K. (2006) Advances in silica planar lightwave circuits. Journal of Lightwave Technology, 24, 4763-4789.

- [2] Okamoto, K. (1999) Recent progress of integrated optics planar lightwave circuits. Optical and Quantum Electronics, 31, 107-129.

- [3] Feng, D.Z., Feng, N.N., Kung, C.C. and Liang, H. (2011) Compact single-chip VMUX/DEMUX on the siliconon-insulator platform. Optics Express, 19, 6125.

- [4] Cho, S.M., Kim, Y.T. and Yoon, D.H. (2003) Optical characterization of silica based waveguide prepared by plasma enhanced chemical vapor deposition. Journal of the Korean Physical Society, 42, S947-S951.

- [5] 亢喆, 黎威志, 袁凯, 蒋亚东 (2010) PECVD淀积SiO2薄膜工艺研究. 微处理机, 1, 23-26.

- [6] Tandon, P. and Boek, H. (2003) Experimental and theoretical studies of flame hydrolysis deposition process for making glasses for optical planar devices. Journal of Non-Crystalline Solids, 317, 275-289.

- [7] Ruano, J.M., Benoit, V., Aitchison, J.S. and Cooper, J.M. (2000) Flame hydrolysis deposition of glass on silicon for the integration of optical and microfluidic devices. Analytical Chemistry, 72, 1093-1097.

- [8] Kim, Y.T., Cho, S.M. and Seo, Y.G. (2003) Refractive index control of core layer using PECVD and FHD for silica optical waveguide. Surface and Coatings Technology, 171, 34-38.

- [9] Hess, R.R. (2011) Optimized PECVD chamber clean for improved film deposition capability. CS MANTECH Conference, Palm Springs, 16th-19th May 2011, 4p.

- [10] Lai, Q., Gu, J.S., Smit, M.K., Schmid, J. and Melchior, H. (1992) Simple technologies for fabrication of low-loss silica waveguide. Electronics Letters, 28, 1000-1001.

- [11] 郑伟, 吴远大, 邢华, 张乐天, 李爱武, 刘国范, 张玉书 (2002) 火焰水解法制备SiO2-GeO2平面波导材料. 光子学报, 22, 45-48.

- [12] Cho, J., Han, D., Song, J.H. and Jung, S. (2005) Crosstalk enhancement of awg fabricated by flame hydrolysis deposition method. IEEE Photonics Technology Letters, 17, 2328-2330.

- [13] Kominato, T., Ohmori, Y., Okazaki, H. and Yasu, M. (1990) Very low-loss GeO2-doped silica waveguides fabricated by flame hydrolysis deposition method. Electronics Letters, 26, 327-329.

- [14] Cho, S.M., Kim, Y.T. and Yoon, D.H. (2003) Optical characterization of silica based waveguide prepared by plasma enhanced chemical vapor deposition. Journal of the Korean Physical Society, 42, S947-S951.

- [15] Ay, F. and Aydinli, A. (2004) Comparative investigation of hydrogen bonding in silicon based PECVD grown dielectrics for optical waveguides. Optical Materials, 26, 33-46.

- [16] Iacona, F., Ceriola, G. and La Via, F. (2001) Structural properties of SiO2 films prepared by plasma enhanced chemical vapor deposition. Materials Science in Semiconductor Processing, 4, 43-46.

- [17] Lee, J.W., Kim, S.S., Lee, B.T. and Moon, J.H. (2004) Ge-doped SiO2 glass films prepared by plasma enhanced chemicalvapor deposition for planar waveguides. Applied Surface Science, 228, 271-276.

- [18] 杭凌侠, 张霄, 周顺 (2010) PECVD 工艺参数对SiO2薄膜光学性能的影响. 西安工业大学学报, 2, 117-120.

- [19] Hussein, M.G., Wörhoff, K., Roeloffzen, C.G.H., Hilderink, L.T.H., de Ridder, R.M. and Driessen, A. (2001) Characterization of thermally treated PECVD SiON layers. IEEE/LEOS Benelux Chapter 2001 Annual Symposium, Brussel, 3 December 2001, 1-4.

- [20] Kim, Y.T., Cho, S.M., Seo, Y.G., Yoon, H.D., Im, Y.M. and Yoon, D.H. (2003) Influence of hydrogen on SiON thick film for silica waveguide depositedby PECVD and annealing effect. Surface and Coatings Technology, 173-174, 204- 207.

- [21] Bauters, J.F., Heck, M.J.R., John, D., Dai, D., Tien, M.C., Barton, J.S., et al. (2011) Ultra-low-loss high-aspect-ratio Si3N4 waveguides. Optics Express, 19, 3163-3274.

- [22] Bauters, J.F., Heck, M.J.R., John, D.D., Tien, M.C., Li, W., Barton, J.S., Leinse, A., Heideman, R.G., Blumenthal, D.J. and Bowers, J.E. (2011) Ultra-low-loss single-mode Si3N4 waveguides with 0.7 dB/m propagation loss. 37th European Conference and Exhibition on Optical Communication, Geneva, 18-22 September 2011, 18-22.

- [23] Zhang, L., Xie, W., Wu, Y., Xing, H., Li, A., Zheng, W. and Zhang, Y. (2003) Thermal annealing of SiO2 fabricated by flame hydrolysis deposition. Chinese Physics Letters, 20, 1366-1368.

NOTES

*通讯作者。