Open Journal of Circuits and Systems

Vol.3 No.01(2014), Article ID:13282,6 pages

DOI:10.12677/OJCS.2014.31003

Research on Channel Estimation Algorithm for LTE Uplink Based on FPGA

School of Electronics and Information Engineering, Beijing Jiaotong University, Beijing

Email: xbzhou@bjtu.edu.cn

Copyright © 2014 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received: Feb. 10th, 2014; revised: Mar. 12th, 2014; accepted: Mar. 20th, 2014

ABSTRACT

From the point of view of implementation, channel estimation of LTE uplink is studied in the paper. Firstly, LS, MMSE and other commonly used channel estimation algorithm are analyzed and simulated by MATLAB. Secondly, channel estimator circuit structure adopting digital MMSE algorithm is described in detail. Then, in accordance with the 3GPP physical layer standards, based on FPGA, digital channel estimation algorithm of TD-LTE uplink system is implemented. The simulation results illustrate that the digital MMSE algorithm model system is optimal in both the complexity of the system and channel estimation effect.

Keywords:LTE; MMSE; Channel Estimation; FPGA

基于FPGA的LTE系统信道估计算法

研究与设计

周晓波,王建忠,邵际南

北京交通大学电子信息工程学院,北京

Email: xbzhou@bjtu.edu.cn

收稿日期:2014年2月10日;修回日期:2014年3月12日;录用日期:2014年3月20日

摘 要

本论文从实现的角度对LTE系统信道估计算法进行了研究,对LS、MMSE等常用的信道估计算法进行了分析和MATLAB仿真;详细介绍了采用数字化后的MMSE算法实现的信道估计器电路结构,依照3GPP物理层标准,实现了基于FPGA的TD-LTE系统上行的信道估计算法电路。仿真结果表明,所提出的数字化MMSE算法模型系统在系统复杂度和信道估计效果上都较为优化。

关键词

LTE;MMSE;信道估计;FPGA

1. 引言

LTE是3GPP组织为WCDMA、TD-SCDMA等各种3G移动通信标准制定的长期演进,旨在增加系统的频谱利用率、提高数据的传输率和降低系统的传输延时[1] 。

LTE标准物理层采用了OFDM和MIMO等关键技术来提高系统的频谱利用率,而这些关键技术的性能很大程度依赖于信道估计的精确度。目前大多数的硬件实现方案采用DSP[2] ,本论文主要从电路实现的角度,对信道估计算法进行研究,并设计出基于FPGA的符合3GPP标准的数字化信道估计算法,这些工作都有很重要的实际意义。

本文首先分析研究OFDM系统中最常用的最小平方估计算法(LS)和最小均方误差估计算法(MMSE) [3] [4] ,给出算法仿真结果,再针对MMSE算法进行数字化设计与仿真验证工作。

2. 最小平方误差估计(LS)算法

最小平方误差估计算法是一种不考虑信道噪声影响的简单算法,其算法推导过程如下。由于系统是在频域进行估计的,推导过程中的各个矩阵都是频域信号。

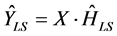

(1)

(1)

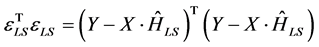

LS算法忽略噪声的影响,得到下式:

(2)

(2)

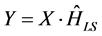

其中 是估计结果即信道冲激响应的估计值,

是估计结果即信道冲激响应的估计值, 是根据此估计值获得的接收到的信号。估计值和实际值之间的误差为:

是根据此估计值获得的接收到的信号。估计值和实际值之间的误差为:

(3)

(3)

LS算法希望误差的平方 最小,因此:

最小,因此:

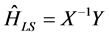

(4)

(4)

令:

(5)

(5)

则:

(6)

(6)

(7)

(7)

可见,LS估计方法的计算就是将在各个子载波上接收到的信号与发出的信号进行相除,得到的估计结果。这种方法计算过程少,简单,电路易于实现,但由于其在估计过程中忽略了噪声的影响,因此当实际信道信噪比低的情况下,这种估计方法的准确度就非常低了。

3. 最小均方误差估计(MMSE)

由于LS算法受噪声影响比较大,因此在LS算法的基础上,产生基于最小均方误差(MMSE)的估计算法。

(8)

(8)

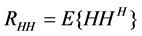

其中 为信道冲激响应的自相关矩阵,

为信道冲激响应的自相关矩阵, 。MMSE算法的要比LS算法运算量上大很多,因为每当发送信号发生变化时

。MMSE算法的要比LS算法运算量上大很多,因为每当发送信号发生变化时 都会要重新计算。为了简化计算,式中

都会要重新计算。为了简化计算,式中 可以用它的期望代替,可得

可以用它的期望代替,可得

(9)

(9)

(10)

(10)

其中 ,且其在星座调制中为常数,对于QPSK,

,且其在星座调制中为常数,对于QPSK, ,对于16QAM,

,对于16QAM, 。

。

为MMSE算法的信道估计结果。

为MMSE算法的信道估计结果。

3.1. 数字化最小均方误差估计(Digital-MMSE)算法

为了在FPGA中实现MMSE算法,本文对该算法进行了数字化设计。该模块主要是利用导频符号来估计信道的特性,并计算噪声功率和信噪比。导频信号是基站连续发射未经调制的直接序列扩频信号,它使得接收端能够获得前向码分多址信道时限,提供相关解调相位参考。由于导频是在通信协议中规定的,因此可以利用导频作为训练序列进行信道估计[5] 。

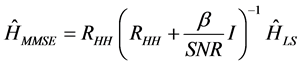

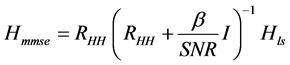

由式(10)可知,MMSE算法信道估计的表达式为:

(11)

(11)

其中 为一个随SNR变化的矩阵,

为一个随SNR变化的矩阵, 为LS算法的信道估计结果。由上式可以看出,MMSE算法实际上是对LS算法的估计结果进行了一次滤波处理,消除了部分噪声的影响,因此估计效果要比LS算法好。

为LS算法的信道估计结果。由上式可以看出,MMSE算法实际上是对LS算法的估计结果进行了一次滤波处理,消除了部分噪声的影响,因此估计效果要比LS算法好。

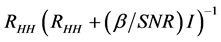

在基于FPGA的电路设计上,用MMSE算法进行信道估计第一步是进行LS估计,其方法就是将接收到的导频信号与本地生成的导频信号的共轭相乘,结果就是 [6] 。第二步是

[6] 。第二步是 与

与 相乘,也就是通过一个系数为

相乘,也就是通过一个系数为 的可变系数FIR滤波器。由于滤波器系数是SNR的函数,因此需要计算SNR,计算方法如下:

的可变系数FIR滤波器。由于滤波器系数是SNR的函数,因此需要计算SNR,计算方法如下:

1) 将LS算法估计结果 进行FIR滤波,滤波的结果与

进行FIR滤波,滤波的结果与 相减,计算出信道噪声频谱。

相减,计算出信道噪声频谱。

2) 对 所有频点的值进行取模的平方,再将这些值求和,从而计算出信号功率。

所有频点的值进行取模的平方,再将这些值求和,从而计算出信号功率。

3) 对第1)步计算所得的噪声频谱所有频点的值进行取模的平方,再将这些值求和,计算出信道噪声的功率σ2。

4) 再将第2)步和第3)步的结果相除,得到SNR。

为了简化算法,降低系统的复杂度,将可变系数FIR滤波器的系数分为四组,分别对应SNR大于15 db,15 db~10 db,10 db~5 db,5 db~0

db四种情况,再计算出SNR后选择相应的滤波器系数对 进行滤波。

进行滤波。

滤波的结果即所需要的 及噪声功率σ2,将二者送至均衡模块,SNR由于后级模块需要也送至均衡模块再传输至外部。图1为信道估计的流程图,其中的数据均为复数,涉及的全部运算都是复数运算:

及噪声功率σ2,将二者送至均衡模块,SNR由于后级模块需要也送至均衡模块再传输至外部。图1为信道估计的流程图,其中的数据均为复数,涉及的全部运算都是复数运算:

3.2. FPGA实现

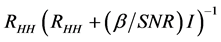

3.2.1. 电路整体结构

如图2所示,信道估计和均衡部分只是整个设计的一块,在FPGA中,除了这部分,还包括数字前端和数字后续处理中的很大一部分,因此FPGA资源量上要求比较大。由于系统整体延时的要求,核心的信道估计和均衡部分工作速度要达到150 MHz,同时由于整个电路规模庞大,整个芯片上资源占用率会较高,因此对FPGA的工作度要求比较快。本设计中FPGA选择的是ALTERA公司Statix III系列的EP3SE80F780C4,这款FPGA包含64,000个查找表资源(ALUT)、6 Mbits片上存储容量、672个DSP单元、4个PLL、4个DLL以及488个可编程IO。

本系统整体结构模块图如图2所示。

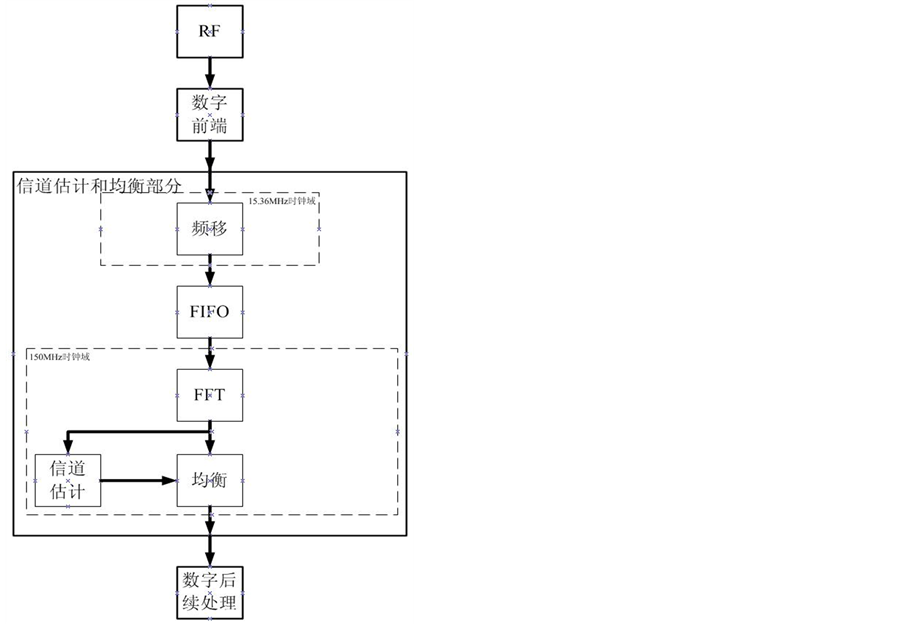

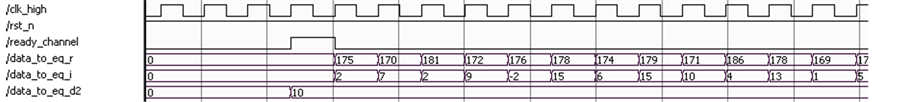

3.2.2. 信道估计算法仿真时序

图3~图5为Digital-MMSE算法的时序仿真波形,数据实部输入和虚部输入通过该算法模块,得到

Figure 1. Structure of channel estimation

图1. 信道估计部分结构图

Figure 2. The circuit structure

图2. 电路整体结构图

Figure 3. Timing of the channel estimation configuration

图3. 信道估计部分配置时序图

Figure 4. Timing of the channel estimation input

图4. 信道估计部分输入时序图

Figure 5. Timing of the channel estimation output

图5. 信道估计部分输出时序图

估计后的实部输出和虚部输出;该输出数据和算法理论结果相同,验证了该MMSE算法的硬件实现正确性。

3.2.3. 资源使用情况

Digital-MMSE算法部分包含的主要器件有:13阶FIR滤波器 × 2,累加器 × 2,复数乘法器,除法器 × 2,1024 × 20 bits FIFO。

导频生成主要器件有:除法器 × 4,1024 × 9 bits ROM × 2,32 × 10 bits ROM,32 × 29 bits ROM FPGA资源使用情况:

4391 combinational ALUTs 4724 dedicated logic registers 42,360 block memory bits 76 DSP block 18-bit elements

4. 算法仿真

算法仿真是在理论的基础上,通过MATLAB等软件进行算法性能的评价。具体的方法是首先建立一个信道模型,用于模拟真实信道的状况。然后将数据通过这个信道模型,模拟数据的发送、传输、接收过程。之后再将通过信道后的数据(即模拟的收到的数据)按照所要评价的算法进行估计计算,同时将收到的数据按照均衡算法进行均衡得到最终均衡后的输出数据。最后将得到的信道估计结果所得的信道冲激响应与信道模型的信道冲激响应进行比较,并取均方误差,同时将均衡后的数据与初始发送的数据进行比较,得到传输过程的误码率,进而评价信道估计算法的优劣。

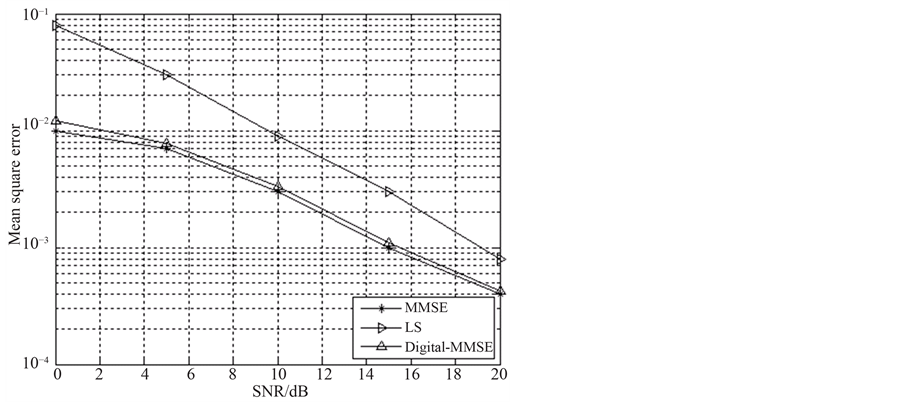

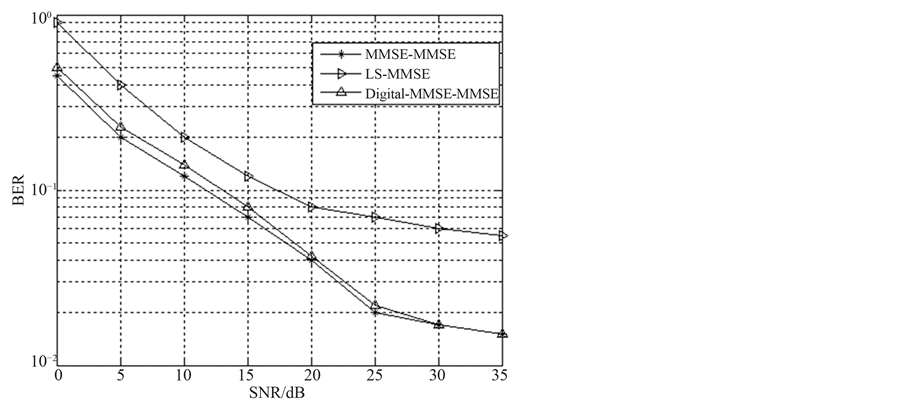

图6和图7分别为LS算法(图例中标LS的曲线)、MMSE算法(图例中标MMSE的曲线)、以及将MMSE算法数字化后的算法(图例中标Digital-MMSE的曲线)三者之间的信道冲激响应均方误差比较,以及接收到的信号的误码率比较,用于仿真的信道是最为常用的高斯信道。从图中比较可见,在均方误差和误码率方面,MMSE算法明显优于LS算法,本论文中采用的数字化后的MMSE算法在性能上比标准MMSE算法略差,这是因为在数字化MMSE算法中,将可变系数FIR滤波器的系数分为四组,再根据SNR进行滤波器组的选择,降低了精确度,但从实现的复杂度上要比标准MMSE算法容易的多。

Figure 6. Simulation results of mean square error

图6. 三种算法的均方误差仿真结果

Figure 7. Simulation results of error rate

图7. 三种算法的误码率仿真结果

5. 结论

本文对LS算法和MMSE算法的信道估计原理进行了介绍,并基于FPGA对数字化后的MMSE算法的信道估计模块进行了设计,提出了一种适合FPGA电路实现的数字化MMSE算法模型。同时利用MATLAB软件对所实现的模块的信道估计特性进行了仿真和比较;仿真结果表明,所提出的数字化MMSE算法模型系统在系统复杂度和信道估计效果上都较为优化,对实际应用具有一定的参考意义。

基金项目

中央高校基本科研业务费专项资金资助(No. 2013JBM010)。

参考文献 (References)

- [1] 3GPP. TS 36.201. V9.0.0. (2009) LTE physical layer—General description. 12.

- [2] 罗润树 (2010) LTE下行系统中信道估计的研究及DSP实现. 电子科技大学, 成都.

- [3] 郑侃 (2003) 宽带无线通信OFDM技术. 人民邮电出版社, 北京.

- [4] 张继东, 等 (2003) 基于导频的OFDM信道估计及其研究进展. 通信学报, 11, 116-124.

- [5] 王勇, 葛建华, 陆震, 等 (2004) OFDM系统信道估计算法及其FPGA实现. 电路与系统学报, 9, 139-142.

- [6] 卞荔, 朱琦 (2008) 基于IEEE802.16d OFDM系统的FPGA设计. 南京邮电大学学报, 4, 75-81.