Nuclear Science and Technology

Vol.

07

No.

01

(

2019

), Article ID:

28288

,

12

pages

10.12677/NST.2019.71003

Design and Test Research on Short-Circuit Impedance for High Power Pulse Transformer

Zhigang Yang1, Yiyun Huang2

1No. 38 Research Institute of CETC, Hefei Anhui

2University of Science and Technology of China, Hefei Anhui

Received: Dec. 6th, 2018; accepted: Dec. 21st, 2018; published: Dec. 28th, 2018

ABSTRACT

In this paper, the short-circuit impedance of HV-MV, HV-LV and MV-LV is analyzed and designed in detail for ITER-PPEN Transformer. The correctness of the design is verified by measuring test on the short-circuit impedance.

Keywords:ITER, PPEN, Transformer, Short-Circuit Impedance

大功率脉冲变压器短路阻抗设计及试验研究

杨志刚1,黄懿赟2

1中国电子科技集团公司第三十八研究所,安徽 合肥

2中国科学技术大学,安徽 合肥

收稿日期:2018年12月6日;录用日期:2018年12月21日;发布日期:2018年12月28日

摘 要

本文对ITER-PPEN三相三绕组变压器的高压–中压短路阻抗、高压–低压短路阻抗和中压–低压短路阻抗进行了详细的设计分析,并通过对变压器的短路阻抗试验测量,验证了设计分析的正确性。

关键词 :ITER,PPEN,变压器,短路阻抗

Copyright © 2019 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

1. 引言

ITER (thermo-nuclear experimental reactor)是为解决人类面临的能源短缺、环境污染等问题,由欧、美、日、俄、中、韩、印七方共同启动和参与的一个超大型国际科技合作项目,旨在验证磁约束聚变能科学与工程技术的可行性,是迄今为止我国参加的最大国际合作项目 [1] [2] [3] 。ITER所有的部件将由7个参与方分别研制和提供,并按规定时间节点提交安装。经过分解,ITER装置的部件被拆分成22个采购包,共97个子包。我国承担了12个子包(分属6个采购包)的制造任务,预计研制费和加工费达40亿元人民币。PPEN (pulsed power electrical network)采购包是我国承担的任务之一。PPEN主要为ITER装置的磁体电源、微波电源和中性束电源等各类脉冲运行子系统提供脉冲功率,其电能采用法国电网400 kV双进线经3台相同的三相三绕组变压器变电66 kV和22 kV的方式配送,负载分布在66 kV母线和22 kV母线侧,ITER PPEN技术协议书中的主变压器的主要参数如表1所示。

Table 1. Main technical parameters of PPEN transformer

表1. PPEN主变压器的主要技术参数

短路阻抗是变压器的一个非常重要的性能参数,它对变压器运行时输出电压的高低、承受短路电动能力有直接的影响,是判断变压器能否投入运行的重要参数之一。为了保证变压器高效可靠运行,本文对变压器的高压–中压短路阻抗(Z12)、高压–低压短路阻抗(Z13)和中压–低压短路阻抗(Z23)进行了详细的设计分析,并通过试验测量得到了短路阻抗值,验证了变压器工程设计及计算分析的正确性。

2. 短路阻抗的原理

短路阻抗有多种定义,按照IEC 60076标准定义,短路阻抗是指在参考温度和额定频率下,变压器某一绕组两端子之间的等效串联阻抗 ,其通常以阻抗电压 ,即短路阻抗的标幺值或百分数的形式表示,它包括两个分量:电阻分量 和电抗分量 。根据经验,对于大容量的变压器, 远大于 ,因此,可以近似认为 ,从而把短路阻抗的计算转化为漏电抗的计算 [4] [5] 。

漏电感与漏磁通的数学关系式如下:

(1)

式中, 为漏电感; 为漏磁链; 为漏磁通;W为匝数;I为流过绕组的电流。

漏电抗等于漏电感乘以角频率,公式如下:

(2)

式中, 为漏电抗; 为角频率。

3. 短路阻抗的计算方法

下面以三绕组变压器高压–低压运行为例来推导短路阻抗的工程计算方法 [6] [7] [8] ,假定绕组内部沿轴向方向安匝均匀分布,漏磁势在绕组辐向方向成线性变化关系,漏磁分布如下图1所示。

(

为低压绕组内半径;

为高压绕组外半径;

为低压、高压绕组的平均半径;

为高低压绕组漏磁空道的平均半径;

为低压、高压绕组的辐向厚度;

为高低压绕组漏磁空道的厚度;H为绕组的轴向平均高度)

(

为低压绕组内半径;

为高压绕组外半径;

为低压、高压绕组的平均半径;

为高低压绕组漏磁空道的平均半径;

为低压、高压绕组的辐向厚度;

为高低压绕组漏磁空道的厚度;H为绕组的轴向平均高度)

Figure 1. Magnetic flux distribution schematic diagram for transformer H-L running

图1. 变压器高–低运行时的漏磁分布示意图

图1中,低压绕组内一微小区域dx范围内,包括的匝数是 ,则dx范围内的漏磁链为:

(3)

式中, 为dx范围内的漏磁通; 为漏磁密。

对低压绕组范围内 进行积分,可得到低压绕组的漏磁链为:

(4)

同理,可推导得到高压绕组的漏磁链为:

(5)

对于高压–低压绕组间的主空道位置,磁势保持平衡 ,可推导得到主空道区域的漏磁链为:

(6)

高压–低压运行时,三个区域的总漏磁链为:

(7)

式中,令 ,称为等效漏磁面积。

将计算结果代入公式(2)中,计算得到:

(8)

则短路阻抗计算为:

(9)

式中, 为漏磁场洛氏系数, ; 为匝电动势,单位V。

在实际计算中,考虑到辐向漏磁通的存在及制造工艺造成的误差,一般乘以一个工艺修正系数K来进行校正,并将 , 代入公式(9)中,可得短路阻抗的工程计算公式如下:

(10)

4. PPEN主变压器短路阻抗计算分析

PPEN主变压器的结构由内到外依次是铁芯、低压绕组、中压绕组、高压绕组、分接绕组、油箱。下面按照3节中推导的短路阻抗的工程计算方法,依次求取额定分接高–中、最小分接高–中、最大分接高–中、额定分接高–低、最小分接高–低、最大分接高–低、中–低的短路阻抗。

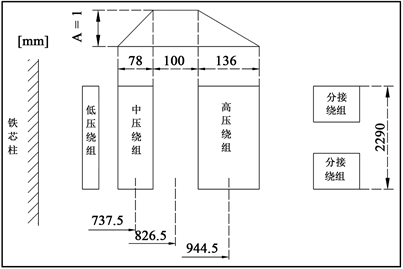

4.1. 额定分接高–中短路阻抗计算

额定分接下,高–中压绕组安匝平衡,假设相对漏磁势取为1,额定分接高–中运行时相对漏磁势如图2所示。

Figure 2. Magnetic flux distribution schematic diagram for transformer H-M running in rated tap

图2. 额定分接变压器高–中运行时的漏磁分布示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表2。

Table 2. Calculation of the area of magnetic flux leakage for transformer H-M running in rated tap

表2. 额定分接高–中运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.956,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到额定分接高–中短路阻抗为:

(11)

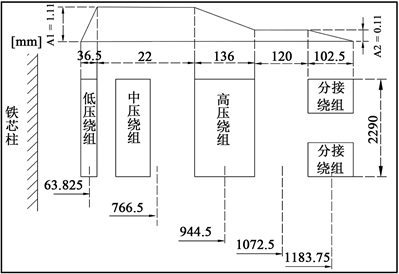

4.2. 最小分接高–中短路阻抗计算

假设以中压绕组为基准,折算到额定容量下的安匝数计算为:

(12)

最小分接绕组的相对漏磁势计算为:

(13)

高压绕组相对漏磁势计算为:

(14)

因此,最小分接下高–中运行时相对漏磁势如图3所示。

Figure 3. Magnetic flux distribution schematic diagram for transformer H-M running in min. tap

图3. 最小分接高–中运行时相对漏磁势示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表3。

Table 3. Calculation of the area of magnetic flux leakage for transformer H-M running in min. tap

表3. 最小分接高–中运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.925,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到最小分接高–中短路阻抗为:

(15)

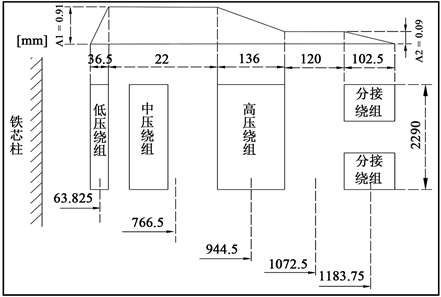

4.3. 最大分接高–中短路阻抗计算

最大分接绕组的相对漏磁势计算为:

(16)

高压绕组相对漏磁势计算为:

(17)

因此,最大分接下高–中运行时相对漏磁势如图4所示。

Figure 4. Magnetic flux distribution schematic diagram for transformer H-M running in max. tap

图4. 最大分接高–中运行时相对漏磁势示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表4。

Table 4. Calculation of the area of magnetic flux leakage for transformer H-M running in max. tap

表4. 最大分接高–中运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.925,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到最大分接高–中短路阻抗为:

(18)

4.4. 额定分接高–低短路阻抗计算

额定分接下,高–低压绕组安匝平衡,假设相对漏磁势取为1,其相对漏磁势如图5所示。

Figure 5. Magnetic flux distribution schematic diagram for transformer H-L running in rated tap

图5. 额定分接高–低运行时相对漏磁势示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表5。

Table 5. Calculation of the area of magnetic flux leakage for transformer H-L running in rated tap

表5. 额定分接高–低运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.945,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到额定分接高–低短路阻抗为:

(19)

4.5. 最小分接高–低短路阻抗计算

假设以低压绕组为基准,折算到额定容量下的安匝数计算为:

(20)

最小分接绕组的相对漏磁势计算为:

(21)

高压绕组相对漏磁势计算为:

(22)

因此,最小分接下高–低运行时相对漏磁势如图6所示。

Figure 6. Magnetic flux distribution schematic diagram for transformer H-L running in min. tap

图6. 最小分接高–低运行时相对漏磁势示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表6。

Table 6. Calculation of the area of magnetic flux leakage for transformer H-L running in min. tap

表6. 最小分接高–低运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.915,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到额定分接高–低短路阻抗为:

(23)

4.6. 最大分接高–低短路阻抗计算

最大分接绕组的相对漏磁势计算为:

(24)

高压绕组相对漏磁势计算为:

(25)

因此,最大分接下高–低运行时相对漏磁势如图7所示。

Figure 7. Magnetic flux distribution schematic diagram for transformer H-L running in max. tap

图7. 最大分接高–低运行时相对漏磁势示意图

各漏磁区域计算参数、漏磁区域面积的计算结果见表7。

Table 7. Calculation of the area of magnetic flux leakage for transformer H-L running in max. tap

表7. 最大分接高–低运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.915,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到额定分接高–低短路阻抗为:

(26)

4.7. 中–低短路阻抗计算

中–低压绕组安匝平衡,假设相对漏磁势取为1,其相对漏磁势如图8所示。

Figure 8. Calculation of the area of magnetic flux leakage for transformer M-L running

图8. 中–低运行时漏磁区域面积的计算结果

各漏磁区域计算参数、漏磁区域面积的计算结果见表8。

Table 8. Calculation of the area of magnetic flux leakage for transformer M-L running

表8. 中–低运行时漏磁区域面积的计算结果

可以计算得到ρ = 0.978,取K = 0.98,再将I1 = 433.03 A;W1 = 636;et = 362.9 V;H = 229 cm代入式(10),计算得到额定分接高–低短路阻抗为:

(27)

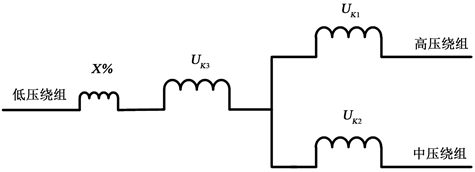

5. PPEN主变压器短路阻抗的匹配设计

通过第3节对短路阻抗的分析计算,发现为PPEN设计的主变压器自身结构的高–低短路阻抗值和中–低短路阻抗达不到设计任务书(技术规范书)的要求,需要进一步进行短路阻抗的匹配设计,以提高高–低短路阻抗值和中–低短路阻抗值,同时高–中短路阻抗值保持不变,从而满足设计要求。

提高短路阻抗最直接、最有效的方法是增大等效漏磁面积。目前主要有以下四种结构形式设计:1) 拆分高压、中压绕组;2) 增大中压绕组和低压绕组之间的主空道;3) 高压绕组内置排列;4) 在低压绕组侧串联电抗器 [9] 。前三种结构形式需要改变变压器本身的结构,而且绝缘处理非常复杂,第四种结构形式不需要改变变压器本身的结构,实现容易,工程上已广泛成熟使用。综合以上考虑,课题组决定采用在低压绕组侧内置串联电抗器来实现对PPEN主变压器短路阻抗匹配的设计。

在低压绕组侧内置串联电抗器的结构特点在变压器的低压侧串联一个空心电抗器,通过空心电抗器的电抗来增大高–低和中–低短路阻抗。因此,短路阻抗匹配设计的关键在于电抗器参数的确定与设计。变压器低压侧串联电抗器示意图如图9所示。

Figure 9. Schematic diagram of series reactor in transformer low-voltage side

图9. 变压器低压侧串联电抗器示意图

在额定分接下,PPEN主变压器要求基于300 MVA的短路阻抗:高–中为 ,高–低为 ,中–低为 。在第4节中已求出PPEN主变压器本身结构基于300 MVA的短路阻抗:高–中为 ,高–低为 ,中–低为 。

低压绕组需要增加的短路阻抗值计算为:

(28)

从而可以求出串联电抗器的电抗值为:

(29)

式(29)中IN3是低压绕组的额定电流值。

再可以求出串联电抗器的电感值为:

(30)

由于电抗器与低压绕组串联,因此,其额定电压等级与低压侧额定电压相同,额定电流与通过低压绕组的额定电流相同,额定容量为:

(31)

将匹配设计的电抗器值带入短路阻抗公式,反算得到PPEN主变压器最终的短路阻抗值,并通过试验对变压器的短路阻抗进行测量,将计算值与试验值进行比较,结果见于表9。

IEC 60076-1:2011表1中规定的短路阻抗的偏差:额定分接高–中为±10%,其他分接高–中为±15%,额定分接高–低为±7.5%,其他分接高–低为±10%,中–低为±10% [10] 。所以,由表9数据可知,PPEN主变压器的短路阻抗分析计算结果、试验测量值以及它们的偏差均在IEC标准的偏差范围内,证明在低压绕组侧内置串联电抗器的短路阻抗匹配设计方法合理。

Table 9. Calculation and test results for PPEN transformer short-circuit impedance

表9. PPEN主变压器短路阻抗的计算及试验结果

6. 结论

本文针对PPEN主变压器的短路阻抗进行了设计和详细分析计算,并进行了试验验证,计算和试验结果表明:1) 该变压器本身结构的短路阻抗达不到客户的设计要求,通过在低压绕组侧内置串联电抗器的方法达到了短路阻抗匹配设计的效果;2) 该变压器的短路阻抗满足IEC标准规定的要求,工程设计和理论计算分析是正确的。目前,该变压器已成功装配应用在ITER实验场地中。

致 谢

本文中实验方案的制定和实验数据的测量记录工作是在保定天威集团变压器有限公司左红艳、谢辉、刘学民等工作人员的大力支持下完成的,在此向他(她)们表示衷心的感谢。

文章引用

杨志刚,黄懿赟. 大功率脉冲变压器短路阻抗设计及试验研究

Design and Test Research on Short-Circuit Impedance for High Power Pulse Transformer[J]. 核科学与技术, 2019, 07(01): 16-27. https://doi.org/10.12677/NST.2019.71003

参考文献

- 1. 傅鹏. 国际聚变堆ITER装置电源系统综述[J]. 电力电子技术, 2014, 48(12): 1-7.

- 2. 杨志刚, 傅鹏, 等. ITER脉冲功率变电站一次系统研究与实现[J]. 强激光与粒子束, 2017, 29(6): 1-6.

- 3. 潘传红. 国际热核实验反应堆(ITER)计划与未来核聚变能源[J]. 物理, 2010, 39(6): 375-378.

- 4. 尹克宁. 变压器设计原理[M]. 北京: 中国电力出版社, 2003.

- 5. 路长柏. 电力变压器理论与计算[M]. 沈阳: 辽宁科学技术出版社, 2007.

- 6. EI Hayek, J. (2001) Short-Circuit Reactances of Multi-Secondaries Concentric Windings Transformers. Electric Machines and Drives Conference, 462-465.

- 7. 周雨. 一种220 kV高阻抗变压器工程设计新方法[D]: [硕士学位论文]. 保定: 华北电力大学, 2013.

- 8. 杨志刚. ITER PPEN主变压器电磁设计及其特性分析[D]: [博士学位论文]. 合肥: 中国科学技术大学, 2017.

- 9. 李洪春. 22 kV三绕组有载调压高阻抗变压器设计[J]. 变压器, 2009, 46(5): 1-11.

- 10. IEC 60076-1: 2011, Power transformers—Part 1: General.