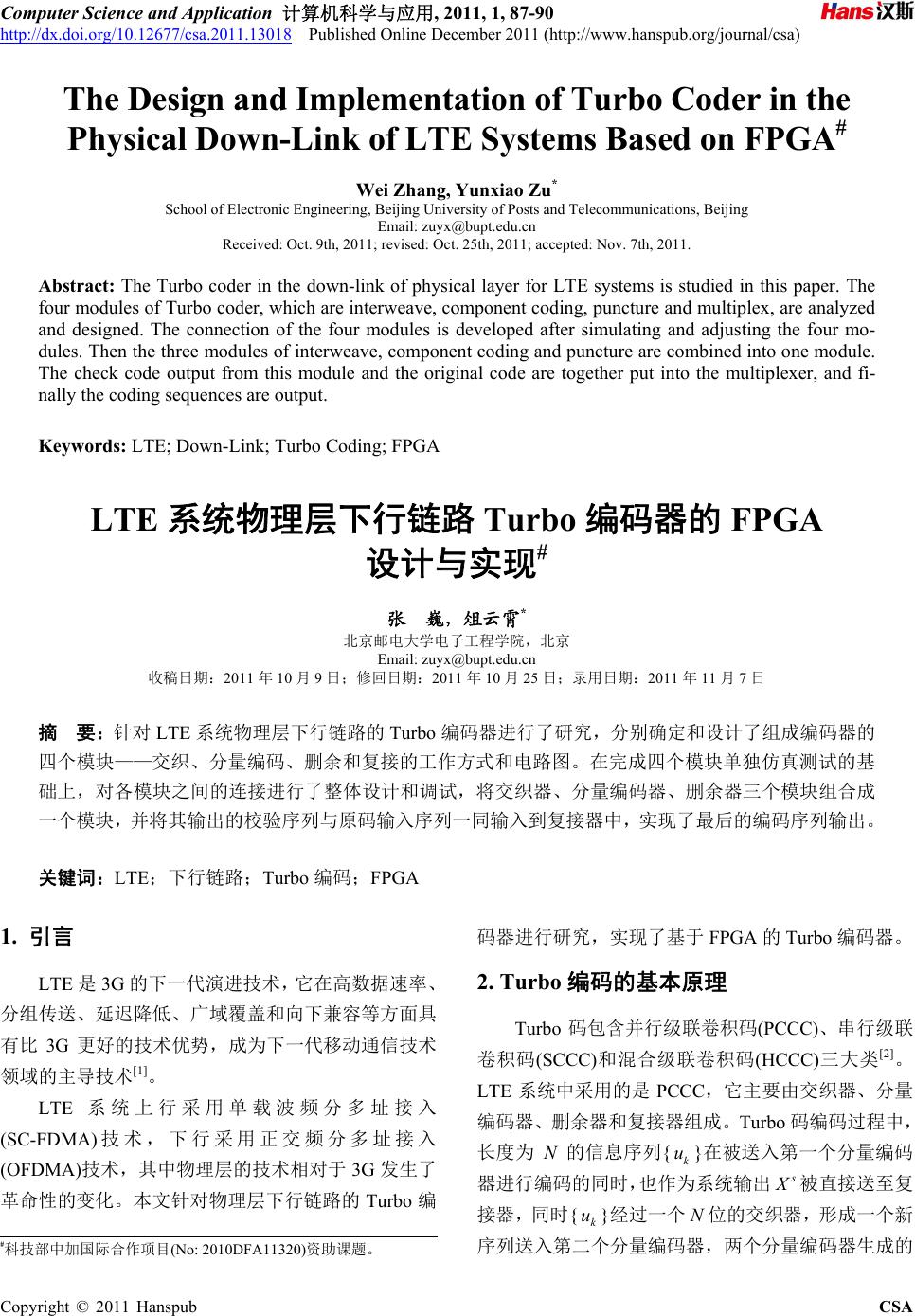

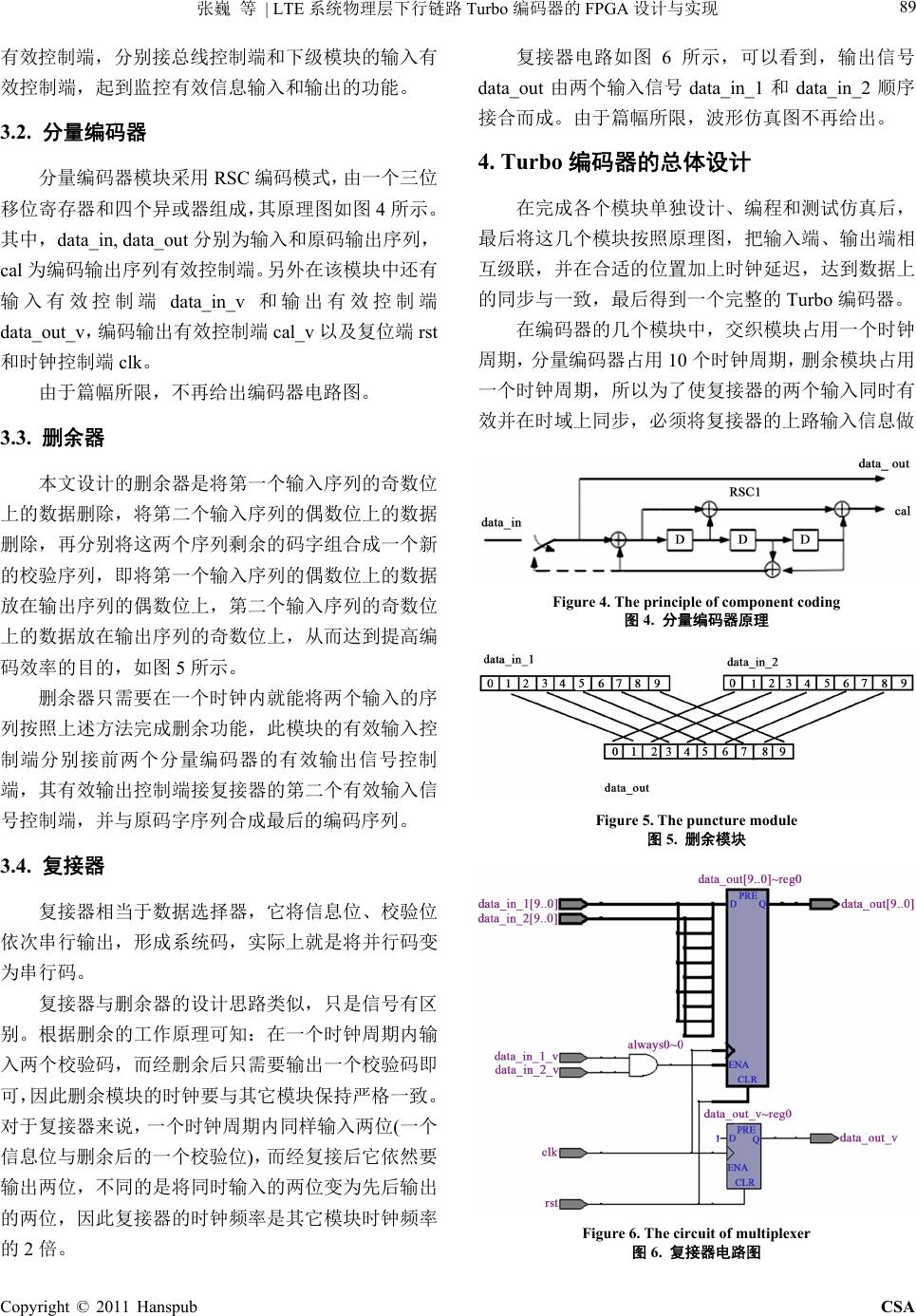

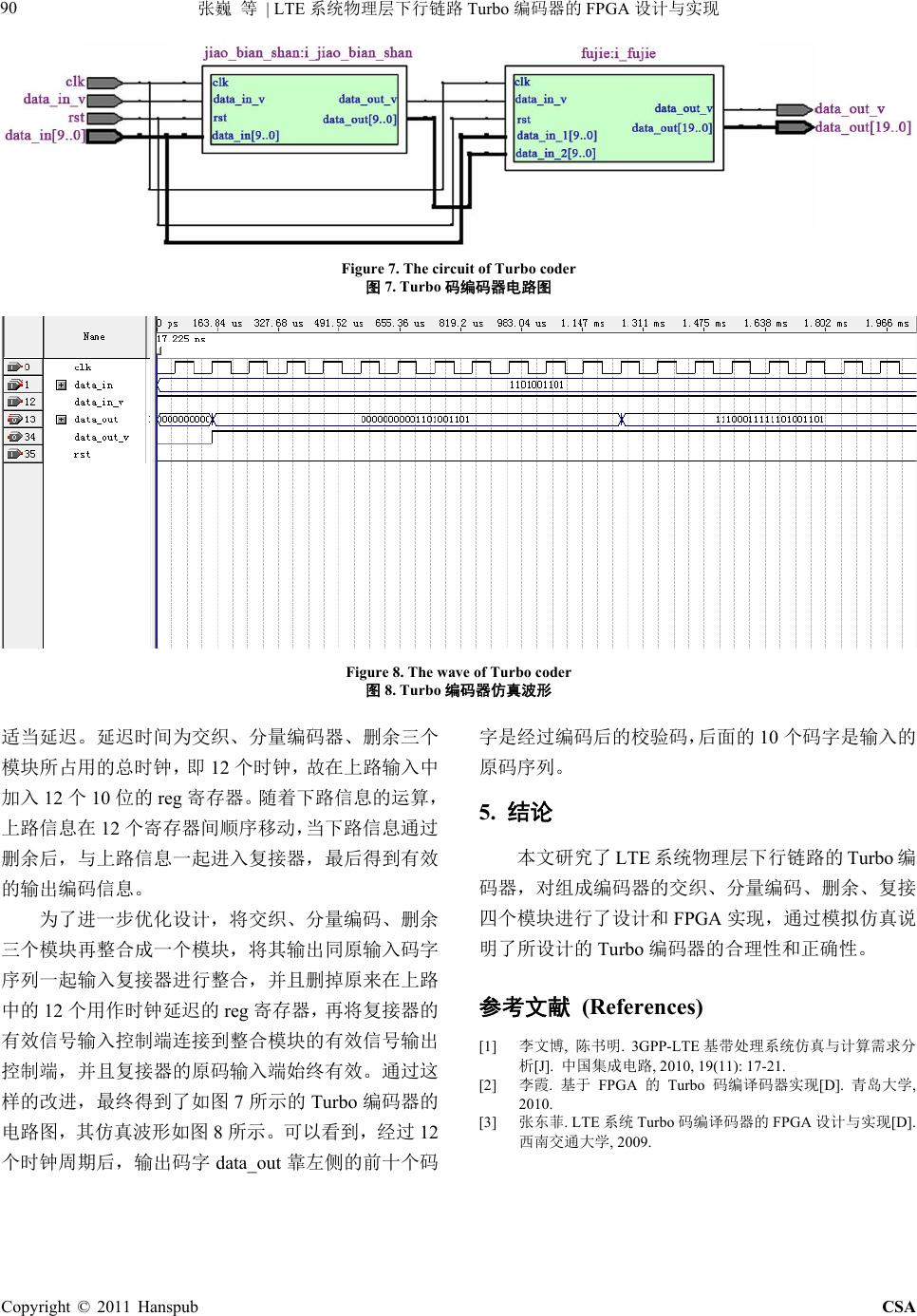

Computer Science and Applicatio n 计算机科学与应用, 2011, 1, 87-90 http://dx.doi.org/10.12677/csa.2011.13018 Published Online December 2011 (http://www.hanspub.org/journal/csa) Copyright © 2011 Hanspub CSA The Design and Implementation of Turbo Coder in the Physical Down-Link of LTE Systems Based on FPGA# Wei Zhang, Yunxiao Zu* School of Electronic Engineering, Beijing University of Posts and Telecommunications, Beijing Email: zuyx@bupt.edu. cn Received: Oct. 9th, 2011; revised: Oct. 25th, 2011; accepted: Nov. 7th, 2011. Abstract: The Turbo coder in the down-link of physical layer for LTE systems is studied in this paper. The four modules of Turbo coder, which are interweave, componen t coding, puncture and multiplex , are analyzed and designed. The connection of the four modules is developed after simulating and adjusting the four mo- dules. Then the three modules of interweave, component coding and puncture are combined into one module. The check code output from this module and the original code are together put into the multiplexer, and fi- nally the coding sequences are output. Keywords: LTE; Down-Link; Turbo Coding; FPGA LTE 系统物理层下行链路 Turbo 编码器的 FPGA 设计与实现# 张 巍,俎云霄* 北京邮电大学电子工程学院,北京 Email: zuyx@bupt.edu. cn 收稿日期:2011 年10 月9日;修回日期:2011 年10 月25 日;录用日期:2011 年11 月7日 摘 要:针对 LTE 系统物理层下行链路的Turbo 编码器进行了研究,分别确定和设计了组成编码器的 四个模块——交织、分量编码、删余和复接的工作方式和电路图。在完成四个模块单独仿真测试的基 础上,对各模块之间的连接进行了整体设计和调试,将交织器、分量编码器、删余器三个模块组合成 一个模块,并将其输出的校验序列与原码输入序列一同输入到复接器中,实现了最后的编码序列输出。 关键词:LTE;下行链路;Turbo 编码;FPGA 1. 引言 LTE 是3G 的下一代演进技术,它在高数据速率、 分组传送、延迟降低、广域覆盖和向下兼容等方面具 有比 3G 更好的技术优势,成为下一代移动通信技术 领域的主导技术[1]。 LTE 系统上行采用单载波频分多址接入 (SC-FDMA) 技术,下行采用正交频分多址接入 (OFDMA)技术,其中物理层的技术相对于 3G 发生了 革命性的变化。本文针对物理层下行链路的 Turbo 编 码器进行研究,实现了基于FPGA 的Turbo 编码器。 2. Turbo编码的基本原理 Turbo 码包含并行级联卷积码(PCCC)、串行级联 卷积码(SCCC)和混合级联卷积码(HCCC)三大类[2]。 LTE 系统中采用的是 PCCC,它主要由交织器、分量 编码器、删余器和复接器组成。Turbo 码编码过程中, 长度为 N的信息序列 k u}在被送入第一个分量编码 器进行编码的同时,也作为系统输出 { s X 被直接送至复 接器,同时 k u}经过一个N位的交织器,形成一个新 序列送入第二个分量编码器,两个分量编码器生成的 { #科技部中加国际合作项目(No: 2010DFA11320)资助课题。  张巍等系统物理层下行链路 编码器的设计与实现 LTETurbo FPGA 88 列效验序 1 p X 和2 p X 经过删余器后生成校验 列 p 序 X ,并与 s X 一起经过复接器构成码字序列 Code 输 出,如图 1所示[3]。 2.1. 交织 交织是将 Turbo 码实现为近似随机码的关键,它 实际上是输入码字序列和输出码字序列之间的一种映 射关系。交织器在分量编码器2之前将信息序列中的 N个比特的位置进行置换,从而减小分量编码器输出 的校验序列的相关性。 根据不同的设计思路,交织器可以分为规则交织 器和伪随机交织器两大类。规则交织器通常按照一定 的规则映射,实现交织,比较容易实现。伪随机交织 器是随机生成交织映射的交织器。规则交织器又分为 分组交织器、对称交织器、循环移位交织器和二次算 术交织器。本文采用分组交织器进行实现。 分组交织器的基本原理是:将信息序列看作一个 矩阵,信息按行写入,按列读出,从而实现交织的功 能。经过这样的置换,信息序列的首尾比特位置在交 织前后保持不变,交织后的距离特性呈均匀分布。 2.2. 分量编码 在Turbo 码中,分量码可以是递归系统卷积码 (RSC)、非递归卷积(NRC)码和非系统卷积(NSC)码。 其中递归系统卷积码是最佳选择,本文采用了这种编 码器。 2.3. 删余 Turbo 码若不进行删余,则码率为 1/3,这样的低 码率对于对带宽利用率要求较高的 LTE 系统是不 能 满足要求的,所以必须引入删余机制,周期性地删除 选定的比特,减少码信息的冗余度,提高码率。 ˆ k u k u 1p X 2p X s X p X Figure 1. The principle of Turbo coder 图1. Turbo编码器原理 2.4. 复接 复接器就是将两个输入的码字按照先后顺序合并 成一个码字进行输出。 3. Turbo编码器的设计实现 3.1. 交织器 本文设计的交织器是分组交织器。整个Turbo 编 码模块的编码长度暂定为10 个比特,交织矩阵设定为 2 × 5阶的矩阵,此矩阵的行、列长度可以根据编码长 度而变。输入序列和输出序列间的映射关系如图 2所 示。 交织器模块的电路图如图3所示。其中,data_in, data_out 分别为输入数据和输出数据,rst为复位, data_in_v,data_out_v分别为输入有效控制端和输出 Figure 2. The principle of interweave 图2. 交织原理 Figure 3. The circuit of interweaver 图3. 交织器电路图 Copyright © 2011 Hanspub CSA  张巍等系统物理层下行链路 编码器的设计与实现89 LTETurbo FPGA 有效控制端,分别接总线控制端和下级模块的输入有 效控制端,起到监控有效信息输入和输出的功能。 3.2. 分量编码器 分量编码器模块采用 RSC 编码模式,由一个三位 移位寄存器和四个异或器组成,其原理图如图 4所示。 其中,data_in, data_out分别为输入和原码输出序列, cal 为编码输出序列有效控制端。另外在该模块中还有 输入有效控制端data_in_v 和输出有效控制端 data_out_v,编码输出有效控制端 cal_v 以及复位端 rst 和时钟控制端 clk。 由于篇幅所限,不再给出编码器电路图。 3.3. 删余器 本文设计的删余器是将第一个输入序列的奇数位 上的数据删除,将第二个输入序列的偶数位上的数据 删除,再分别将这两个序列剩余的码字组合成一个新 的校验序列,即将第一个输入序列的偶数位上的数据 放在输出序列的偶数位上,第二个输入序列的奇数位 上的数据放在输出序列的奇数位上,从而达到提高编 码效率的目的,如图5所示。 删余器只需要在一个时钟内就能将两个输入的序 列按照上述方法完成删余功能,此模块的有效输入控 制端分别接前两个分量编码器的有效输出信号控制 端,其有效输出控制端接复接器的第二个有效输入信 号控制端,并与原码字序列合成最后的编码序列。 3.4. 复接器 复接器相当于数据选择器,它将信息位、校验位 依次串行输出,形成系统码,实际上就是将并行码变 为串行码。 复接器与删余器的设计思路类似,只是信号有区 别。根据删余的工作原理可知:在一个时钟周期内输 入两个校验码,而经删余后只需要输出一个校验码即 可,因此删余模块的时钟要与其它模块保持严格一致。 对于复接器来说,一个时钟周期内同样输入两位(一个 信息位与删余后的一个校验位),而经复接后它依然要 输出两位,不同的是将同时输入的两位变为先后输出 的两位,因此复接器的时钟频率是其它模块时钟频率 的2倍。 复接器电路如图 6所示,可以看到,输出信号 data_out 由两个输入信号 data_in_1 和data_in_2 顺序 接合而成。由于篇幅所限,波形仿真图不再给出。 4. Turbo编码器的总体设计 在完成各个模块单独设计、编程和测试仿真后, 最后将这几个模块按照原理图,把输入端、输出端相 互级联,并在合适的位置加上时钟延迟,达到数据上 的同步与一致,最后得到一个完整的 Turbo 编码器。 在编码器的几个模块中,交织模块占用一个时钟 周期,分量编码器占用10 个时钟周期,删余模块占用 一个时钟周期,所以为了使复接器的两个输入同时有 效并在时域上同步,必须将复接器的上路输入信息做 Figure 4. The principle of component coding 图4. 分量编码器原理 Figure 5. The puncture module 图5. 删余模块 Figure 6. The circuit of multiplexer 图6. 复接器电路图 Copyright © 2011 Hanspub CSA  张巍 等 LTE系统物理层下行链路 Turbo 编码器的 FPGA 设计与实现 Copyright © 2011 Hanspub CSA 90 Figure 7. The circuit of Turbo coder 图7. Turbo码编码器电路图 Figure 8. The wave of Turbo co d e r 图8. Turbo编码器仿真波形 适当延迟。延迟时间为交织、分量编码器、删余三个 模块所占用的总时钟,即12 个时钟,故在上路输入中 加入 12 个10 位的reg 寄存器。随着下路信息的运算, 上路信息在 12个寄存器间顺序移动,当下路信息通过 删余后,与上路信息一起进入复接器,最后得到有效 的输出编码信息。 为了进一步优化设计,将交织、分量编码、删余 三个模块再整合成一个模块,将其输出同原输入码字 序列一起输入复接器进行整合,并且删掉原来在上路 中的 12 个用作时钟延迟的reg 寄存器,再将复接器的 有效信号输入控制端连接到整合模块的有效信号输出 控制端,并且复接器的原码输入端始终有效。通过这 样的改进,最终得到了如图 7所示的 Turbo 编码器的 电路图,其仿真波形如图 8所示。可以看到,经过12 个时钟周期后,输出码字 data_out靠左侧的前十个码 字是经过编码后的校验码,后面的 10 个码字是输入的 原码序列。 5. 结论 本文研究了 LTE系统物理层下行链路的 Turbo 编 码器,对组成编码器的交织、分量编码、删余、复接 四个模块进行了设计和FPGA 实现,通过模拟仿真说 明了所设计的 Turbo 编码器的合理性和正确性。 参考文献 (References) [1] 李文博, 陈书明. 3GPP-LTE基带处理系统仿真与计算需求分 析[J]. 中国集成电路, 2010, 19(11): 17-21. [2] 李霞. 基于 FPGA的Turbo 码编译码器实现[D]. 青岛大学, 2010. [3] 张东菲. LTE系统Turbo 码编译码器的 FPGA 设计与实现[D]. 西南交通大学, 2009. |