Open Journal of Circuits and Systems

Vol.3 No.01(2014), Article ID:13283,5 pages

DOI:10.12677/OJCS.2014.31004

Design of SDRAM Controller Based on FPGA

Lingli Zhong, Xiaobo Zhou

School of Electronic Science and Technology, Beijing Jiaotong University, Beijing

Email: 09214027@bjtu.edu.cn, xbzhou@bjtu.edu.cn

Copyright © 2014 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received: Feb. 26th, 2014; revised: Mar. 19th, 2014; accepted: Mar. 25th, 2014

The paper briefly introduces the characteristics of SDRAM and the basic operation principle, then puts forward a design method of SDRAM controller based on FPGA. The controller was achieved by the language of Verilog. The paper analyses the overall design and the specific realization of the design scheme of each module. Finally, the image data should be stored in SDRAM, and then the reading control through SDRAM should be achieved, which sent the data to display on the VGA screen. When the colorful picture was displayed on the screen, it means the function of the SDRAM controller was achieved.

Keywords:SDRAM Controller; FPGA; Verilog

基于FPGA的SDRAM控制器设计开发

仲玲利,周晓波

北京交通大学电子信息学院,北京

Email: 09214027@bjtu.edu.cn, xbzhou@bjtu.edu.cn

收稿日期:2014年2月26日;修回日期:2014年3月19日;录用日期:2014年3月25日

在简要介绍SDRAM特点和基本操作原理的基础上,提出了一种基于FPGA的SDRAM控制器的设计方法,用Verilog硬件语言加以实现。分析了各模块的具体设计方案及整体设计的实现过程,最终实现将图像数据存入SDRAM,再通过SDRAM完成数据的读取,送入VGA进行显示,在输出显示屏上看到彩色图像则表明控制器的功能得以实现。

SDRAM控制器;FPGA;Verilog

SDRAM同步动态随机存储器容量可达256 Mb以上,工作频率可达100~200 MHz,是较为普遍使用的内存芯片。SDRAM发展至今已经历经四代,由于其具有价格低廉、密度高、数据读写速度快等优点,在数据采集系统和图像处理系统等方面得到了广泛的应用[1] 。然而,SDRAM定时刷新、预充电以及行列寻址等一系列操作,使得SDRAM时序控制较为复杂,在使用SDRAM实现特定功能时,经常需要自己设计一个合适的控制器,使系统用户很方便地操作SDRAM。

SDRAM作为一种数据缓存器常被应用于各种高速数据传输系统中。目前,许多嵌入式设备或是高速实时信号处理系统的大容量、高速度存储器都是采用SDRAM来实现,而且大多都是用专用芯片完成其控制电路,这使得硬件电路变得复杂,而且增加了设计成本。当前市场上虽然有一些SDRAM控制器,但大多无法针对特定系统,灵活性较差,不利于SDRAM的特殊应用[2] 。

随着FPGA开发技术逐渐走向成熟,使用FPGA进行开发可以降低系统成本,且可以重复编程。利用FPGA实现SDRAM控制器能够最大程度地保证其应用的灵活性以及可移植性,相比采用专用控制芯片来说优势明显。本文就是介绍如何利用Verilog硬件语言来实现基于FPGA控制的SDRAM多端口控制器,并简单介绍其实现原理。

SDRAM的地址分为页(bank)地址、行(row)地址和列(column)地址。SDRAM被分割为多个bank,而每个bank中行与列共同寻址,减少了地址位占用空间,但却使SDRAM的接口设计更为复杂。

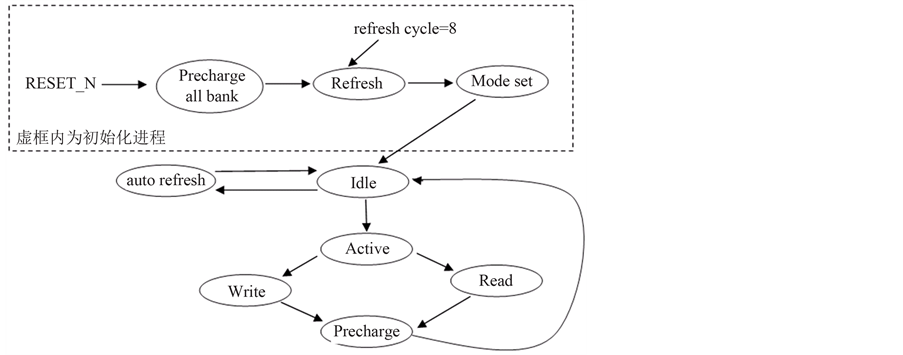

Figure 1. State transition diagram of SDRAM operations

图1. SDRAM操作状态转换图

转换图中SDRAM的一系列指令,都是通过片选信号CS(Chip Select)、行地址选通脉冲RAS(Row Address Strobe Command)、列地址选通脉冲CAS(Column Address Strobe Command)以及写使能信号WE(Write Enable),在时钟上升沿的状态共同决定的。SDRAM控制器必须为SDRAM提供满足时序要求的这些控制信号,以准确地控制SDRAM的各种不同操作[4] 。SDRAM相对SRAM来说,并不只是简单的读写操作,它的操作指令更为复杂多样。

SDRAM的主要操作

图1中虚线框表示SDRAM的初始化进程。SDRAM上电复位经历200 us的输入稳定期后,还需要进行所有bank的预充电、8个刷新周期和模式寄存器设置(Mode Register Set),然后才能进入正常的工作状态。

正常工作状态下,对SDRAM进行访问的最主要操作就是读RD(READ)和写WR(WRITE)操作。SDRAM可实现突发式读写,本文中SDRAM控制器就是基于全页突发读写模式。SDRAM寻址时先通过ACT命令激活特定的bank,并锁存行地址,在读写命令有效时再锁存列地址。需要注意的是,读操作时会有一个CAS延迟时间,又叫做读取潜伏期,通常为1~3个时钟周期。

为避免SDRAM中数据的丢失,需要进行定时的刷新操作。目前公认的标准时,存储体中电容的数据有效保存期上限是64 ms,也就是说每一行刷新的循环周期是64 ms。刷新操作分为两种,Auto Refresh与Self Refresh。

本项目中选用的FPGA是Altera公司生产的Cyclone IV E系列中的EP4CE115,所用到的SDRAM是ISSI系列512 Mb的IS45S16320B,此款同步动态随机存储器的组织结构是8M × 16 × 4 Banks,时钟频率可支持166,143,133 MHz。

在本次运用的控制器中,时钟设定为99 MHz。供电电压为3.3 V,容量大小536,870,912 bits。其内部有四个bank,通过BA0,BA1操作位控制选择。每一个bank包括两种模式,即×8,×16bits模式。×16模式下,一个bank包括8192行 × 1024列个存储单元,每个单元16 bits;×8模式下,一个bank包括8192行 × 2048列个存储单元,每个单元8 bits。

3.1. 总体设计框图

在高速图像处理系统中,数据输入模块与输出模块之间主要由数据缓存模块和SDRAM控制器组成,其中,读写FIFO可以通过Quartus II中IP核例化来得到。

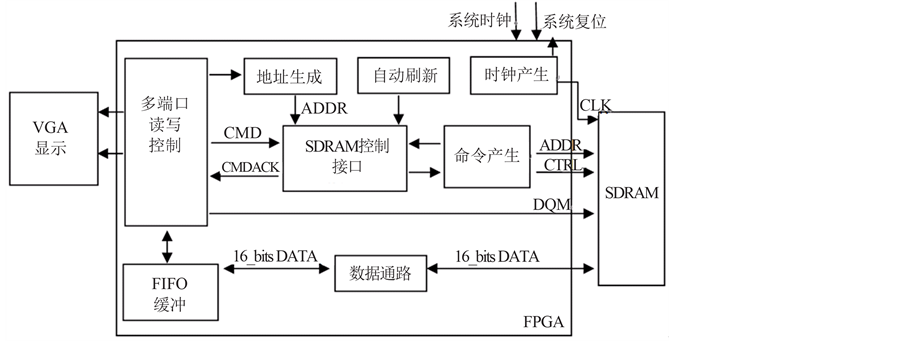

SDRAM控制器的内部结构图如图2所示。控制器中主要包括多端口读写控制模块、SDRAM控制接口模块、命令产生模块、时钟产生模块共四个模块。

3.2. 多端口读写控制模块

多端口读写控制模块是本设计的核心。

系统中SDRAM芯片的工作频率为100 MHz,但与外设的传输频率只有25 MHz,如果在两者间不加缓存,是无法实现页突发模式读写操作的。因而需要利用FPGA片上资源开辟多个FIFO缓存,分别作为读端口与写端口。为保证突发数据的准确性,我们必须在突发读写之前把数据准备好,而准备好的标准就是判断wrusedw和rdusedw。FIFO向SDRAM写入数据和SDRAM向FIFO读出数据的时钟都是外部时钟的几倍,要快很多,所以更强调了SDRAM数据准备的重要性。

多端口读写控制模块是与外部设备进行数据交换的媒介。它会根据对FIFO状态的判断,自动生成相

Figure 2. Internal structure of SDRAM controller

图2. SDRAM控制器的内部结构图

应的读写指令,并实现必要的数据缓冲。

该模块会对系统进行初始化,初始化完成后,它会根据不同的读写指令与地址信息进行分析后,生成对应的CMD命令和SADDR地址信号传给SDRAM控制接口模块。其中,CMD为01时表示读指令,CMD为10时表示写指令,CMD为00时表示空指令。此外,SDRAM控制接口模块也会反馈回CMD_ACK信号。

该模块生成的SADDR地址信号是分时复用的。初始化时,SADDR用于传输初始化定义的模式字内容,正常读写操作中,SADDR就是传递行、列、块信息的地址线。当从下一模块传回的CMD_ACK信号为高时,则表示CMD命令已成功发送并有效执行,此时系统反馈NOP命令。

3.3. SDRAM控制接口模块

当接收到各类CMD指令时,该模块会对这些指令进行分析并生成对应的操作指令给命令产生模块。

控制接口模块内部包含刷新计数器和初始化计数器。当刷新计数器达到规定的计数周期时,会向SDRAM发出REF_REQ请求,当刷新操作完成时,还会发出REF_ACK应答信号,表示一次刷新操作的完成,此时计数器才会重新开始计数,等待下一次刷新操作。通过这两个计数器可以传递对应的刷新请求和初始化请求到命令产生模块。当CMD指令有效执行时会向多端口读写控制模块反送高电平的CMD_ACK信号。

3.4. 命令响应模块

命令产生模块会根据接收到的操作指令做出相应规范动作。该模块在对输入指令进行判断后,会产生相应的CS、RAS、CAS、WE等信号,从而实现对SDRAM的控制操作。此外,系统还会重新把地址信息SADDR分配给SA、BA信号。

SDRAM主要操作指令详见表1。

SDRAM指令主要分初始化指令、刷新指令和读写指令3类。初始化操作是SDRAM正常工作的基础,所以它的优先级最高,刷新请求的优先级次高,读写请求的优先级最低。在同一时刻SDRAM不会同时执行多个指令,各类指令都有对应的优先级别,当某一种指令正在执行时系统不会响应其他的请求。

命令产生模块会在接收到操作指令后,向SDRAM控制接口模块传送高电平的CM_ACK应答信号。如果没有收到任何操作指令,则CM_ACK信号为0,相应的,CMD_ACK信号也为0。

3.5. 时钟产生模块

通过使用PLL(锁相环)资源为系统提供可靠稳定的时钟。

本项目中,使用的是Altera公司的DE2开发板。在得到控制器代码后,首先通过Debussy工具对SDRAM控制器的工作时序进行仿真验证,在验证其正确性之后,又在Quartus 11.1的开发环境中使用Verilog语言进行了设计输入和编译,并将设计代码下载到Cyclone IV E:EP4CE115F29C7的FPGA芯片上。

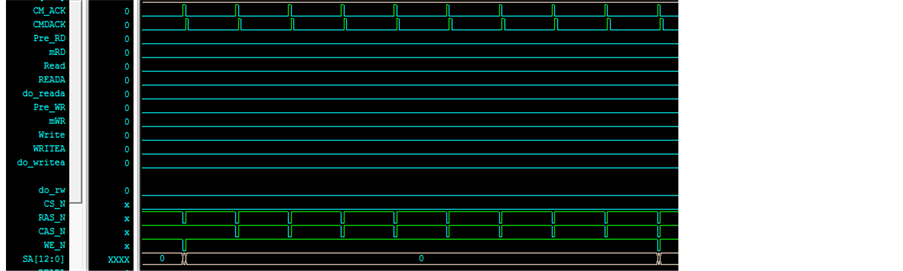

从初始化时序图3中可以看出,初始化的过程中,控制器先进行了200 us的空操作,然后预充电,8个刷新周期,最后是Mode Register Set。这是一套完整的初始化流程。

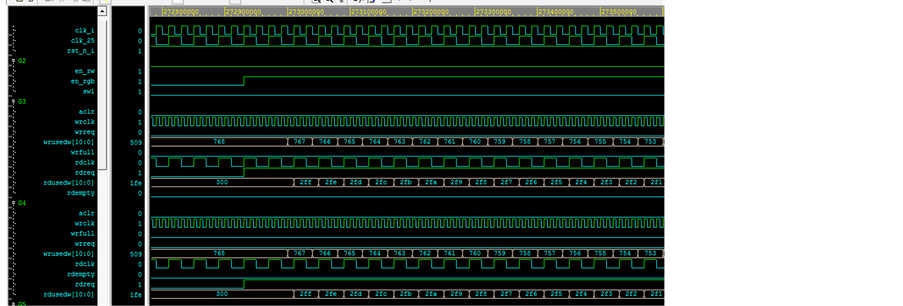

从读时序图4中可以看出,在读操作过程中,SDRAM的突发模式是全页(full page) 突发。在Read fifo中可以读出的数据量达到一定界限时,即可进行全页模式的数据读操作。

根据Debussy仿真结果来看,各控制信号满足相应时序要求,各种状态间能够有效进行跳转,并有效实现了SDRAM的初始化和读写操作。以上时序分析验证了设计的正确性,可以将代码下载到FPGA。

当我们向SDRAM的数据写入完成后,关闭DE2开发板的控制面板,用VGA接口线将开发板与显示屏相连。然后打开编译成功的工程,选择Programmer,在Jtag模式下将工程编译后得到的sof文件加载至开发板,最终实现SDRAM的输出控制,在VGA显示屏上显示出正确的彩色图像。此时我们就实

表1. SDRAM主要操作指令

Figure 3. The initialization timing diagram of SDRAM

图3. SDRAM的初始化工作时序

Figure 4. The reading timing diagram of SDRAM

图4. SDRAM的读时序

现了本设计的预期功能。

本文SDRAM控制器的设计具有很大的实用价值。SDRAM作为实用的高速数据缓存,在基于现场可编程门阵列FPGA的控制下,将在高速、高端、高密度的数字电路领域中得到更加广泛的应用。

中央高校基本科研业务费专项资金资助(No. 2013JBM010)。

- [1] 杨映辉 (2007) 基于FPGA的SDRAM控制器设计及应用. 兰州大学, 兰州.

- [2] 宋一鸣, 谢奕, 李春茂 (2003) 基于FPGA的SDRAM控制器设计. 电子工程师, 9, 11-13.

- [3] 曹华, 邓彬 (2005) 使用Verilog实现基于FPGA的SDRAM控制器. 今日电子, 1, 11-14.

- [4] 樊京, 张宏伟 (2006) 使用FPGA 操作SDRAM的RTL级代码实现. 仪表技术, 3, 52-53.