Open Journal of Circuits and Systems

Vol.3 No.04(2014), Article

ID:14530,5

pages

DOI:10.12677/OJCS.2014.34009

Design of High-Speed Driving Board for Integrated Circuit of Burn-In Test System

School of Communication Engineering, Hangzhou Dianzi University, Hangzhou

Email: *1404769719@qq.com

Copyright © 2014 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received: Oct. 29th, 2014; revised: Nov. 13th, 2014; accepted: Nov. 29th, 2014

Abstract

With the rapid development of production technology for large-scale integrated circuits, applications of multi-pin package chip, large capacity memory and large scale of embedded microprocessor are more and more widely used [1] . Domestic integrated circuit of dynamic burn-in system has been unable to meet the demand. In this paper, taking advantages of FPGA/CPLD high integration, flexible design, etc., it designs and implements high-speed driving board system applied in a new generation of dynamic burn-in system. The system takes the EPM570T144I5N of MAXII series chip in Altera Company as the core. Through the verification of FPGA/CPLD hardware platform, each module of the system works normally and can meet the requirements of driving ability.

Keywords:Integrated Circuit, Dynamic Burn-In, Driving Board, FPGA

集成电路动态老化测试系统中高速驱动板设计

曾 榕*,张福洪,楼津甫

杭州电子科技大学通信工程学院,杭州

Email: *1404769719@qq.com

收稿日期:2014年10月29日;修回日期:2014年11月13日;录用日期:2014年11月29日

摘 要

随着大规模集成电路生产技术的迅猛发展,多引脚封装的芯片、大容量的存储器及大规模嵌入式微处理器的广泛应用,国内现有的集成电路动态老化测试系统已不能满足需求[1] 。该文针对FPGA/CPLD集成度高、设计灵活等优点,设计并实现了一种应用于新一代动态老化系统的高速驱动板系统。该系统以Altera公司的MAXII系列CPLD芯片EPM570T144I5N为核心。通过FPGA/CPLD软硬件平台验证,该系统各个模块均工作正常,并能满足驱动能力的需求。

关键词

集成电路,动态老化,驱动板,现场可编程逻辑门阵列

1. 引言

集成电路的动态老化理论上要求电路在其最高温度工作条件下完全模拟实际工作状态,电路内部的逻辑单元都有机会得到翻转,对于一般数字集成电路都需要外部提供功能测试信号来驱动电路工作。而动态老化又被分为动态激励老化和功能性老化。动态激励老化由不同频率的时钟信号对被测器件进行动态激励,功能性老化是模拟使用状态对被测器件施加信号。本系统采用功能性老化,其典型的表现形式为老化中测试TDBI (Test During Burn-in),它是指将老化与电性能测试有效结合在一起的方法[2] 。此外,本文主要设计了一种基于IR2010S驱动芯片的新型驱动电路,并通过相关软件验证了该电路的优越性。该系统主要包括SPI接口、驱动模块、电平转换,测试信号回检等功能的实现。

2. 驱动板系统总体设计框图

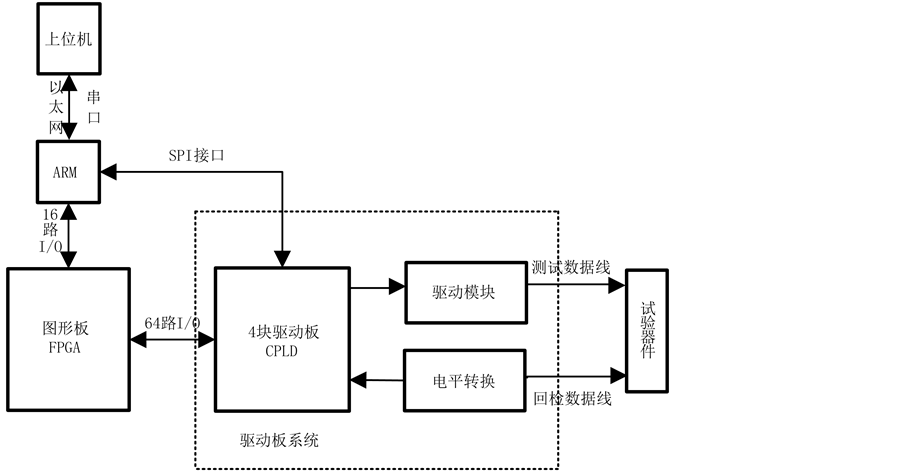

本文所设计的驱动板系统体系总体框图如下图1所示。

Figure 1. System design diagram

图1. 系统总体设计框图

嵌入式系统ARM是整个老化测试系统中的核心部分,负责在对试验器件(DUT)进行老化工作之前,向FPGA传送老化工作过程中所需参数(指令、I/O配置参数,波形数据等)。ARM与驱动板之间采用的是SPI通信接口,驱动板将根据所接受的指令配置相对应的I/O口(测试数据线与回检数据线),进而为后续波形数据回检做好充分准备[3] 。

图形板主要负责接收嵌入式系统提供的16位数据。根据指令模式的不同16路数据具有不同的功能含义,通过FPGA最多可以产生64路数字信号,经过驱动板进行相应处理,再通过金手指加载到试验器件中。在该系统中共有四块驱动板,每一块驱动板负责对16路数字波形信号进行处理,最多可同时驱动64路数字信号。经驱动板上CPLD处理后的数字信号再通过电流电压驱动电路进行电流驱动和电压放大。

数字信号波形回检采用上位机观察。回检信号经过电平转换后再回传给驱动板CPLD与图形板FPGA,然后由图形板传给ARM,最终在上位机进行器件失效率情况的分析处理。

3. 驱动板内部模块的功能介绍与设计

3.1. SPI通信接口模块

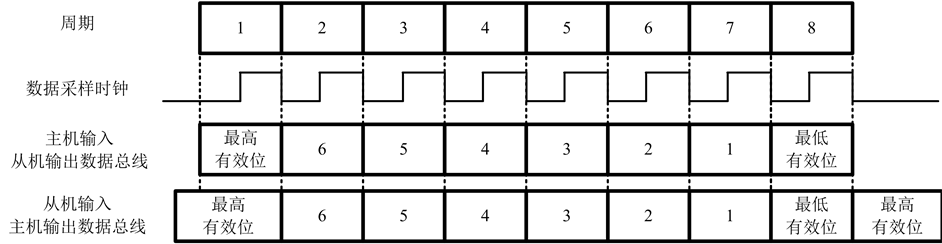

串行外设接口(Serial Peripheral Interface,SPI)总线是Motorola公司提出的一种同步串行外设接口协议,包括主机/从机2种模式,它可以使MCU与各种外围设备以串行方式进行通信以交换信息[4] 。驱动板与ARM之间就使用该通信接口,信号时序如图2所示。

在此通信接口中,ARM为主设备,驱动板为从设备,包括MOSI、MISO、CLK、SSEL四路信号线,其中SSEL为片选信号,低电平有效,持续一帧数据;MOSI为主机输出,从机输入数据总线;MISO为主机输入,从机输出数据总线;CLK是由主设备产生的数据采样时钟信号,上升沿有效。老化参数配置过程中,ARM通过3-8译码器选中四块驱动板中的一块,并且通过SPI接口向驱动板发送16路I/O口状态,总共完成64路I/0口状态配置。

3.2. 驱动模块

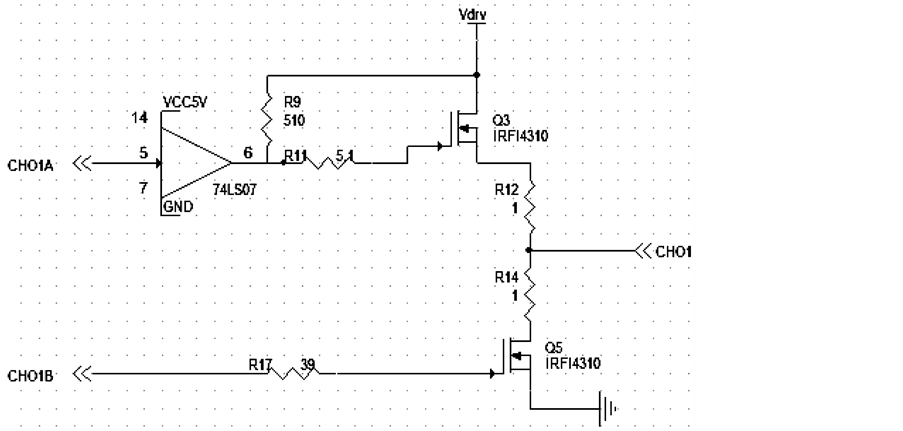

驱动模块是整个驱动板系统中的核心部分。为了满足测试信号输出电压范围为0~18 V的技术指标,这就需要驱动电路对测试信号进行电流驱动和电压放大。本测试系统中,任意一路测试信号线CH1经驱动板CPLD处理后输出两路控制信号(CH01A,CHO1B),通过这组控制信号的高低电平变化来控制驱动电路的最终输出CHO1 [5] ,其中控制信号CHO1A与测试信号CH1同频同相,而CH01B与CH1同频反相。

为了将控制信号3.3 V的TTL电平转换成MOS管标准电平,传统的驱动电路原理图如图3所示。上图中采用TI公司生产的74LS07作为驱动芯片,该芯片是集电极开路输出的六缓冲器/驱动器。此外,为了保证输出端与输入端是同相位,输出端需要通过上拉电阻外接到正电压上。此电路主要有两个不足;第一,当74LS07输出18 V驱动电压时大约只有30 mA的驱动电流,这将大大延长MOS管的冲放电时间和提高开关损耗,进而提高开关损耗;第二,当CHO1A为高电平,CHO1B为低电平时,MOS管Q3导通,MOS管Q2截止,CHO1为高电平,由于MOS管内部的电压降,驱动电路输出电压CHO1与Vdrv之间存在1.5 V左右的损耗电压VS,这不满足驱动电压指标的需求。

为了实现高速驱动系统的功能,针对传统驱动电路中的不足,本文提出并设计了一种新型的高速驱动电路,具体的电路设计原理图如图4所示。与传统的驱动电路相比,上图用IR2010S驱动芯片取代74LS07芯片。IR2010S是由国际整流器公司(International Rectifier)生产的一款高电压,高速功率的MOSSET/IGBT驱动器。同时,IR的芯片具有自举功能,可以驱动H桥高端的MOSFET而不需要加隔离电路。本文所设计的驱动电路克服了传统驱动电路的不足。首先,IR芯片输出18 V驱动电压时大约

Figure 2. Signal timing diagram of SPI

图2. SPI信号时序图

Figure 3. Schematic diagram of traditional driving circuit

图3. 传统的驱动电路原理图

Figure 4. Schematic diagram of driving circuit designed in this paper

图4. 本文所设计的驱动电路原理图

有480 mA的驱动电流,可以保证MOSFET快速的开通,降低MOSFET的开关损耗;其次,驱动电路输出电压CHO1与Vdrv之间的损耗电压VS约为0.05 V,能很好地满足驱动电压的需求。

4. 验证与仿真

4.1. SPI通信接口模块

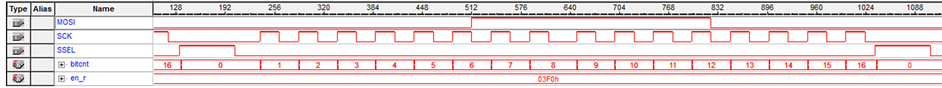

本模块采用Altera公司MAXII系列的EPM570T144I5N芯片,使用verilog HDL语言和Quartus 9.1开发环境进行功能实现。使用嵌入式逻辑分析仪SignalTapII抓实际电路信号的时序如图5所示。ARM传送过来的配置数据MOSI用二进制可表示为0000_0011_1111_0000,而该模块最终输出en_r的值用十六进制表示为03F0。

4.2. 驱动模块

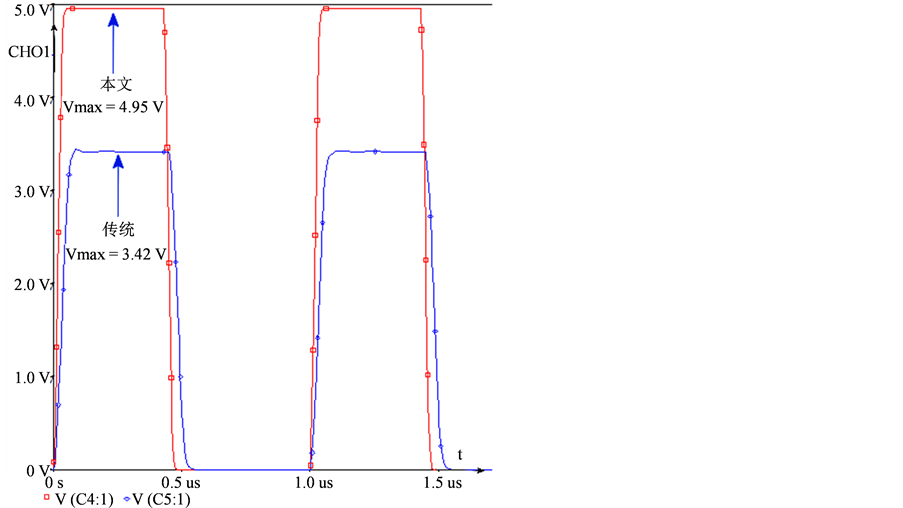

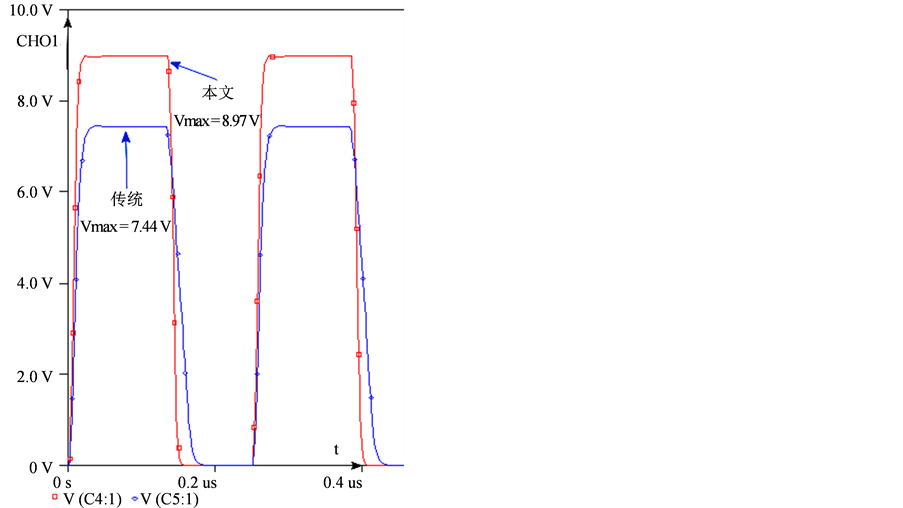

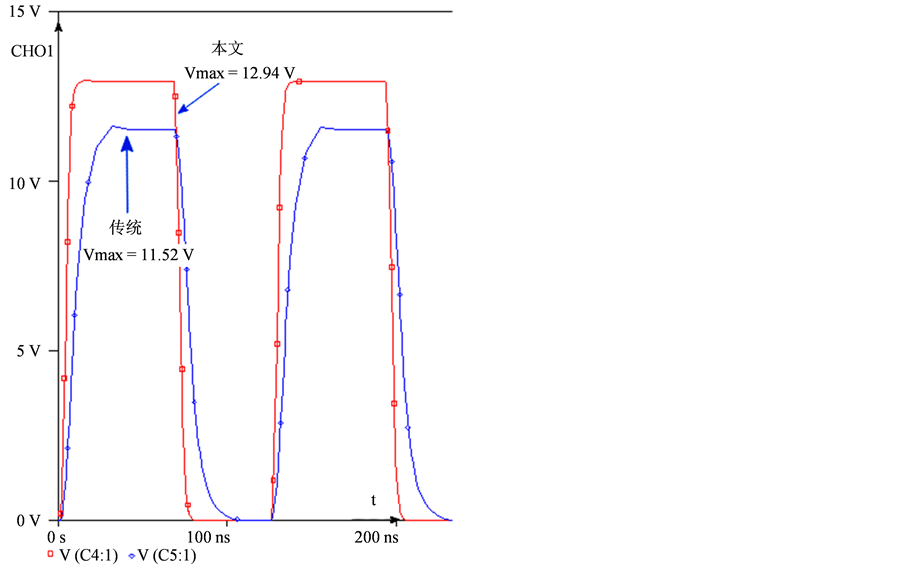

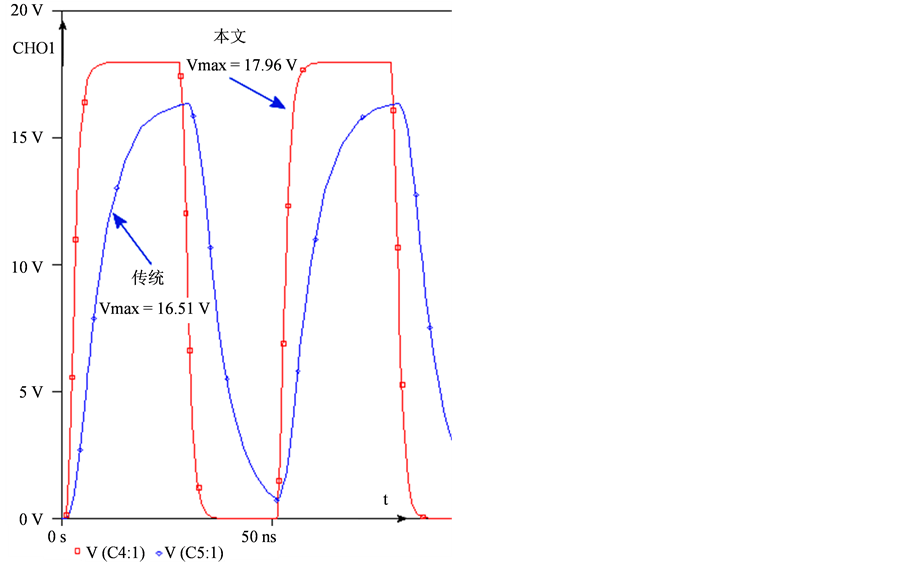

为了验证本文所提出的驱动电路性能优于传统电路,采用Cadence16.3的PSpice AD软件进行模拟电路功能仿真。在仿真电路图中,控制信号CH01A与CHO1B为相同频率,相位相反的方波信号,并将100欧姆电阻和1000皮法电容并联后作为输出端CH01的负载。根据控制信号频率F与驱动电压Vdrv的取值不同,驱动电路的输出电压CHO1如图4所示。

在图6中,定义Vmax为最大峰值电压,Vmax与Vdrv之间的差值为损耗电压VS,t1为上升沿(充电)所需时间,t2为下降沿(放电)所需时间。由上图可以看出,与传统驱动电路相比,本文所设计的驱动电路中的损耗电压VS降低了1.4 V左右,进而反映驱动电路性能高;此外,由于传统驱动电路中MOSFET

Figure 5. Timing diagram of SPI module

图5. SPI模块时序图

(a)

(a) (b)

(b) (c)

(c) (d)

(d)

Figure 6. Output voltage CHO1 of driving circuit (a) F = 1 MHz, Vdrv = 5 V; (b) F = 4 MHz, Vdrv = 9 V; (c) F = 8 MHz, Vdrv = 13 V; (d) F = 20 MHz, Vdrv = 18 V

图6. 驱动电路输出电压CH01。(a) F = 1 MHz,Vdrv = 5 V;(b) F = 4 MHz,Vdrv = 9 V;(c) F = 8 MHz,Vdrv = 13 V;(d) F = 20 MHz,Vdrv = 18 V

的充电/放电电流过小,t1与t2的值随着控制信号频率F的增大而增大,这也间接反映出MOS管正常工作状态下开关切换的速率越慢,当F = 20 MHz时,传统驱动电路的输出波形已不能满足要求,而本文所设计的驱动电路输出波形仍能够满足相应频率的方波特性。综上所述,可以得出本文所设计的驱动电路性能优于传统驱动电路性能结论。

5. 结束语

在本文设计的高速驱动板系统中,涉及到SPI通信接口设计、驱动电路设计、Verilog HDL编程、嵌入式逻辑分析仪Signal TapII与PSpice软件的使用等。经软件与硬件电路验证,基于本文所设计的驱动电路的驱动板能很好地完成对测试信号驱动的任务,并且应用效果良好,完全能够满足大多数用户对集成电路高温老化系统的要求。

参考文献 (References)

- [1] 冉立新 (2003) 大规模集成电路高温动态老化测试嵌入式图形发生系统的可编程ASIC实现. 仪器仪表学报, 24, 27-27.

- [2] 温平平, 焦慧芳, 贾新章等 (2004) VLSI老化筛选试验技术的挑战. 电子产品可靠性与环境验, 5, 22-23.

- [3] 马进峰, 张福洪, 石学诚 (2013) 集成电路高温动态老化系统硬件研制. 电子制作, 11, 226-226.

- [4] 贾伟, 邵左文, 张玉猛等 (2007) 基于SPI总线的高速串行数据采集系统设计. 研发与开发, 4, 37-37.

NOTES

*通讯作者。