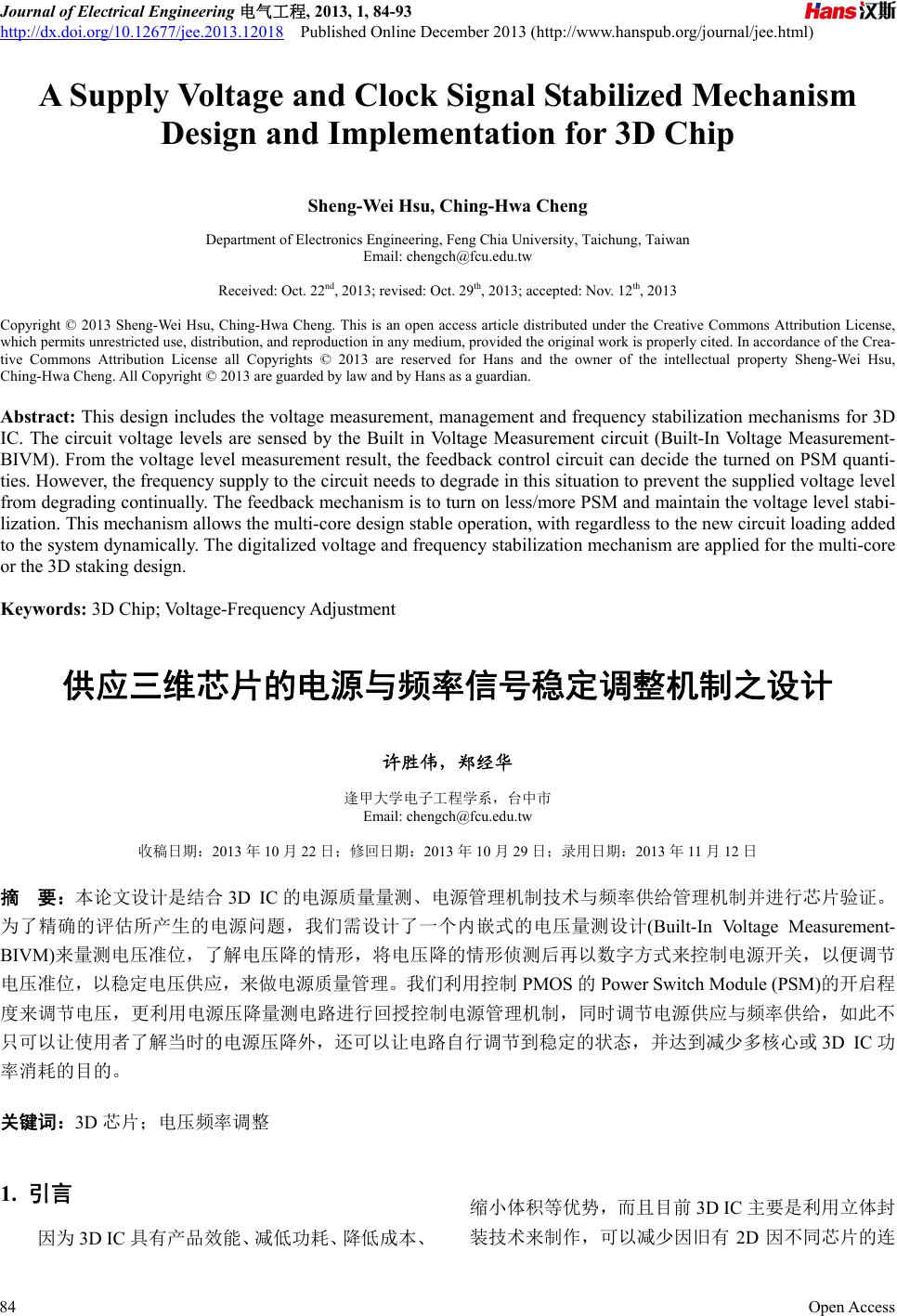

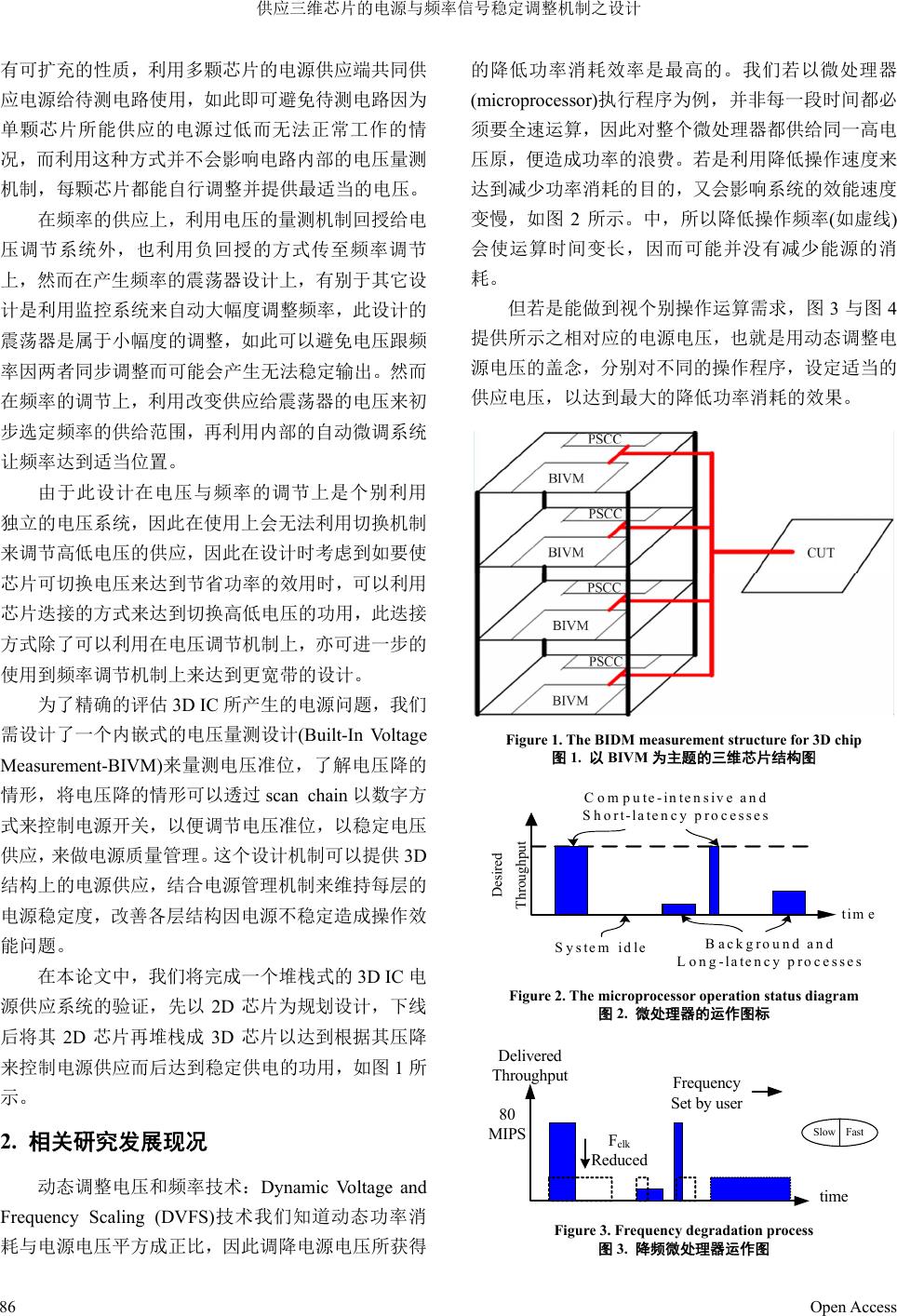

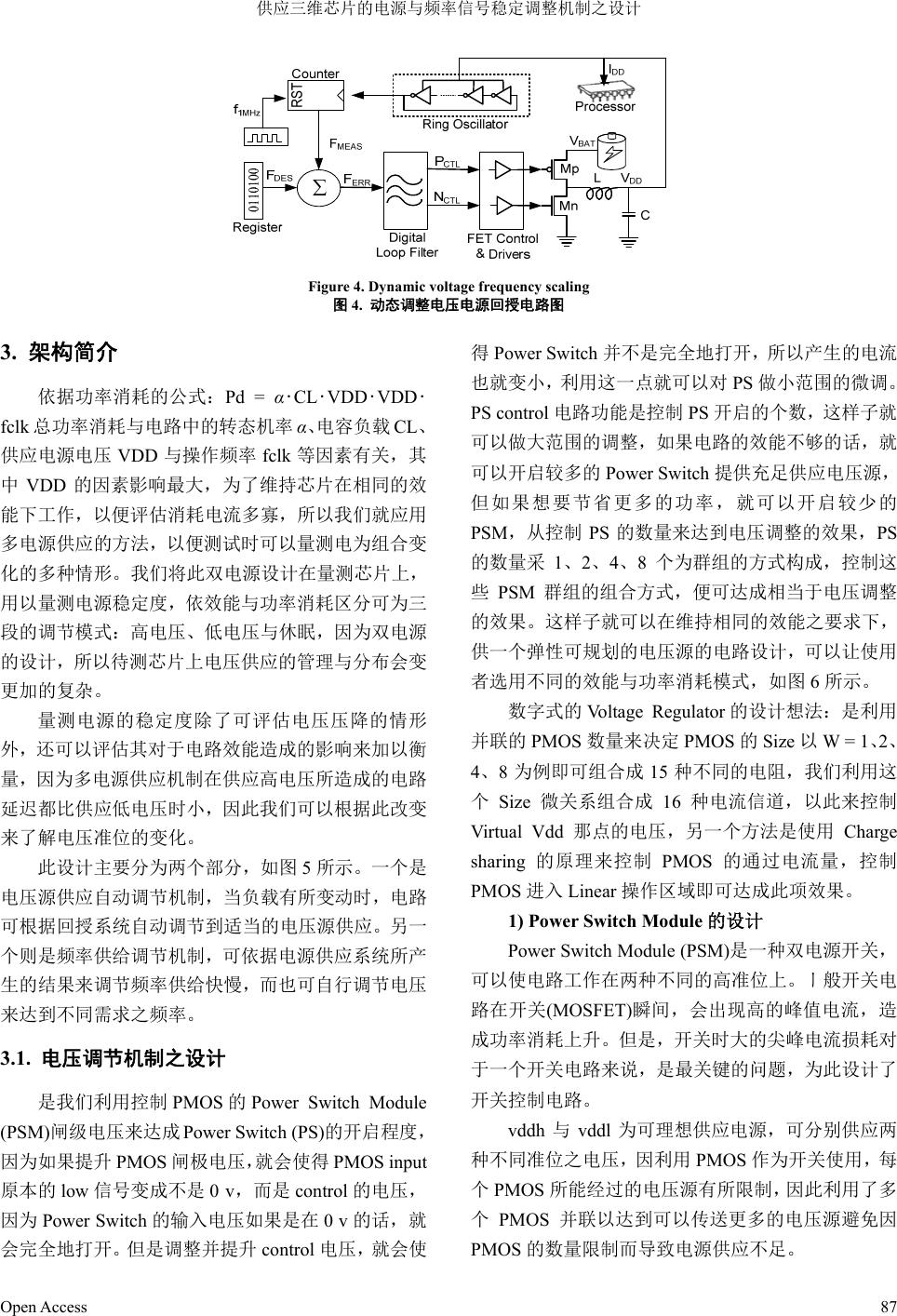

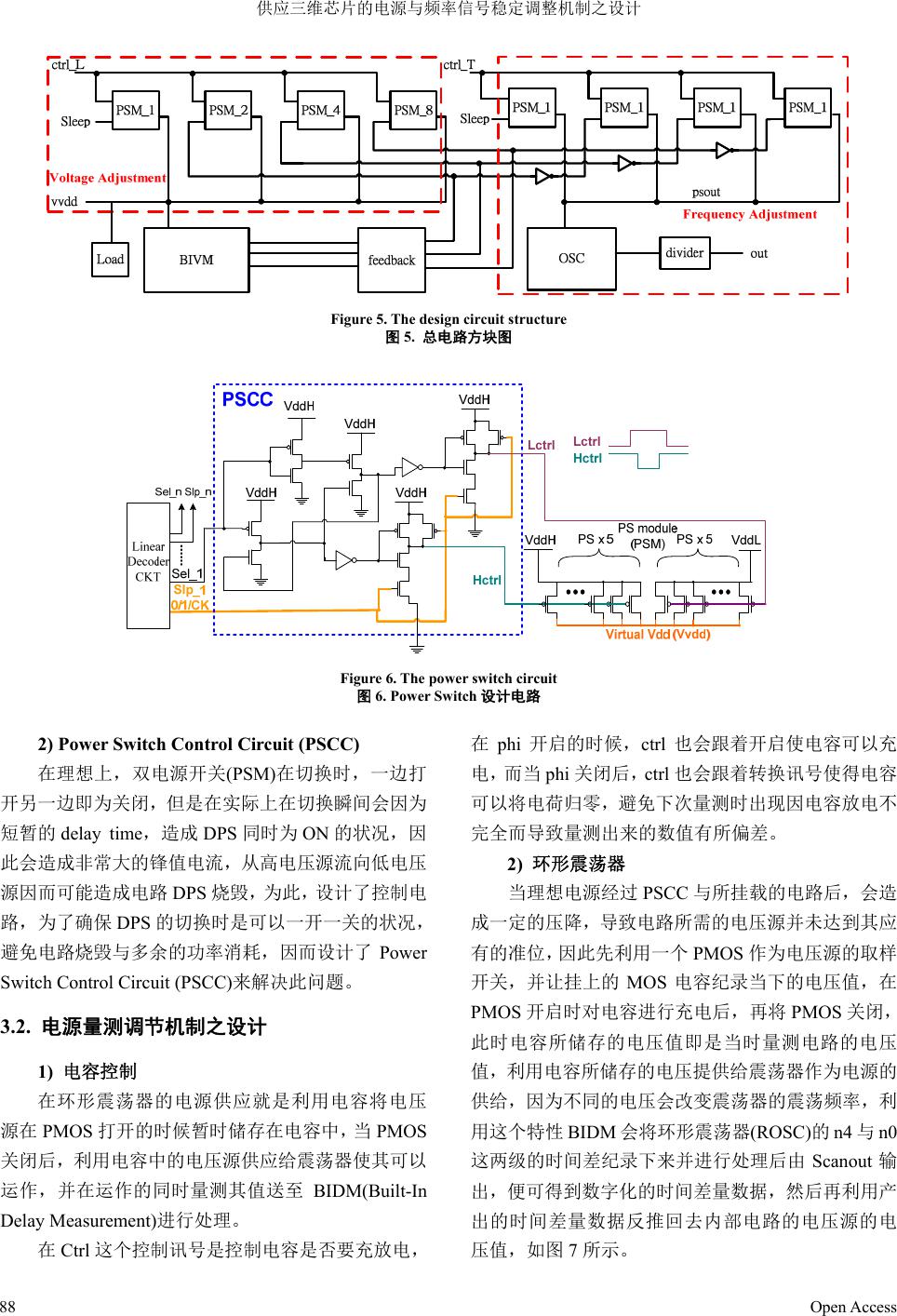

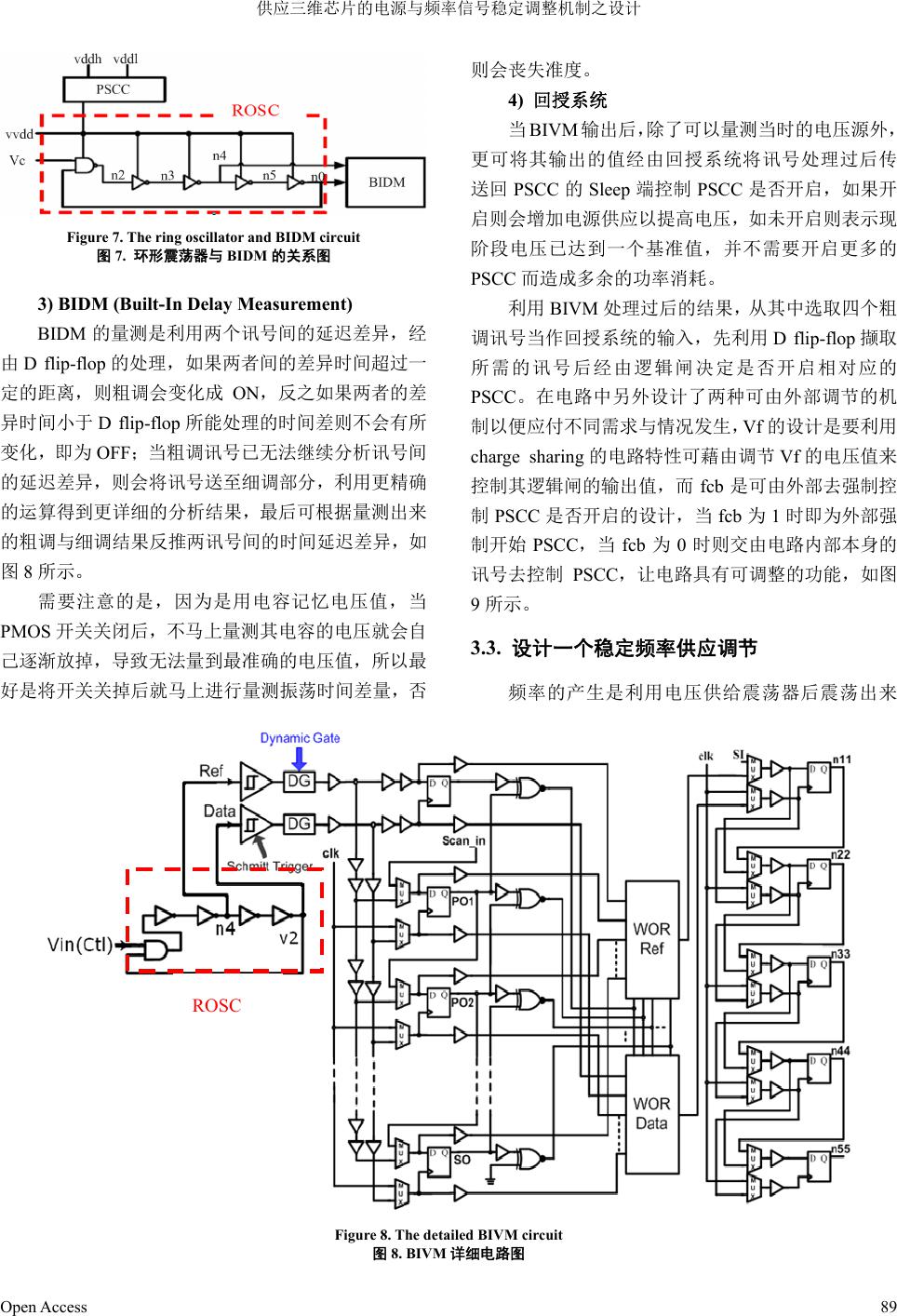

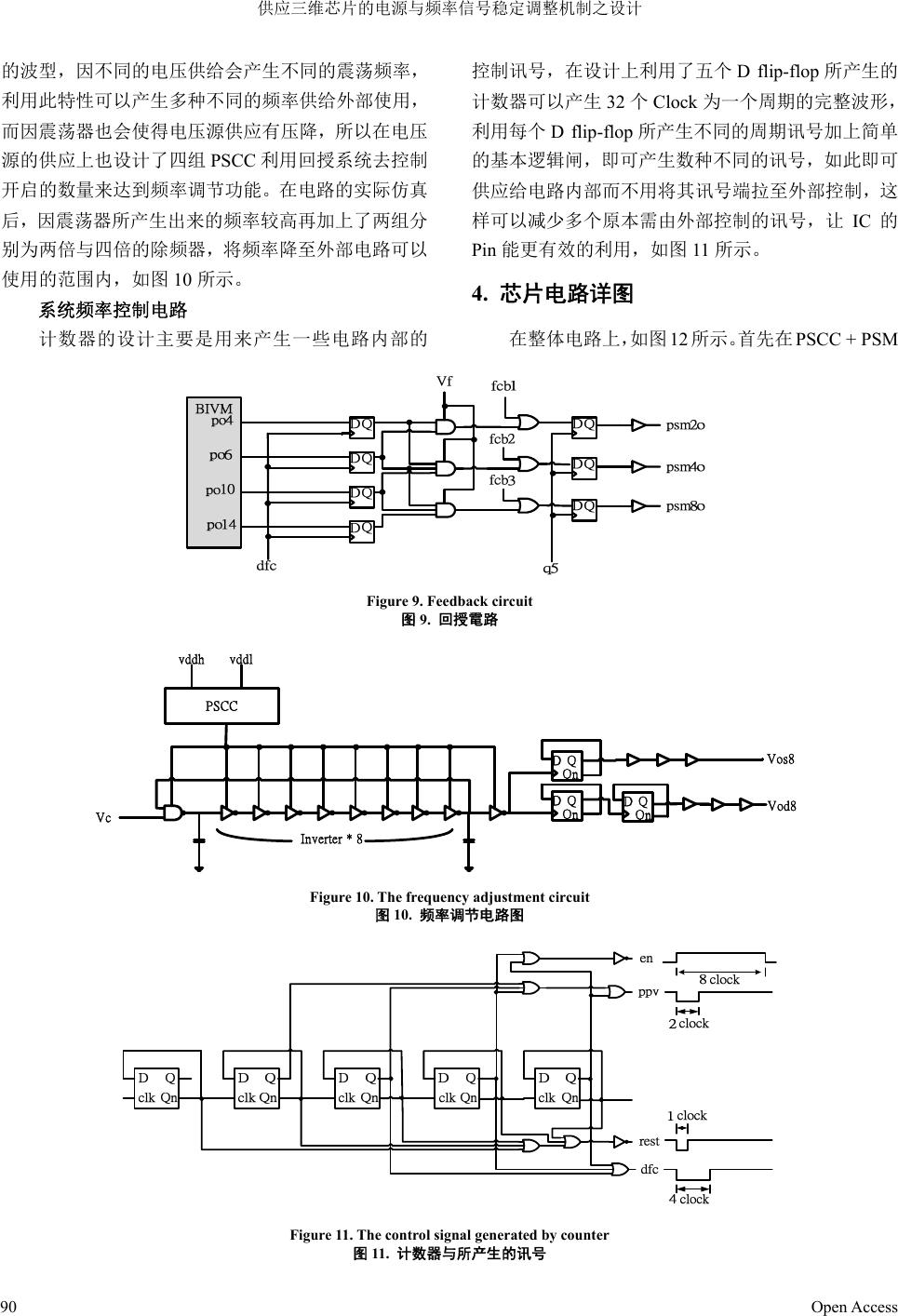

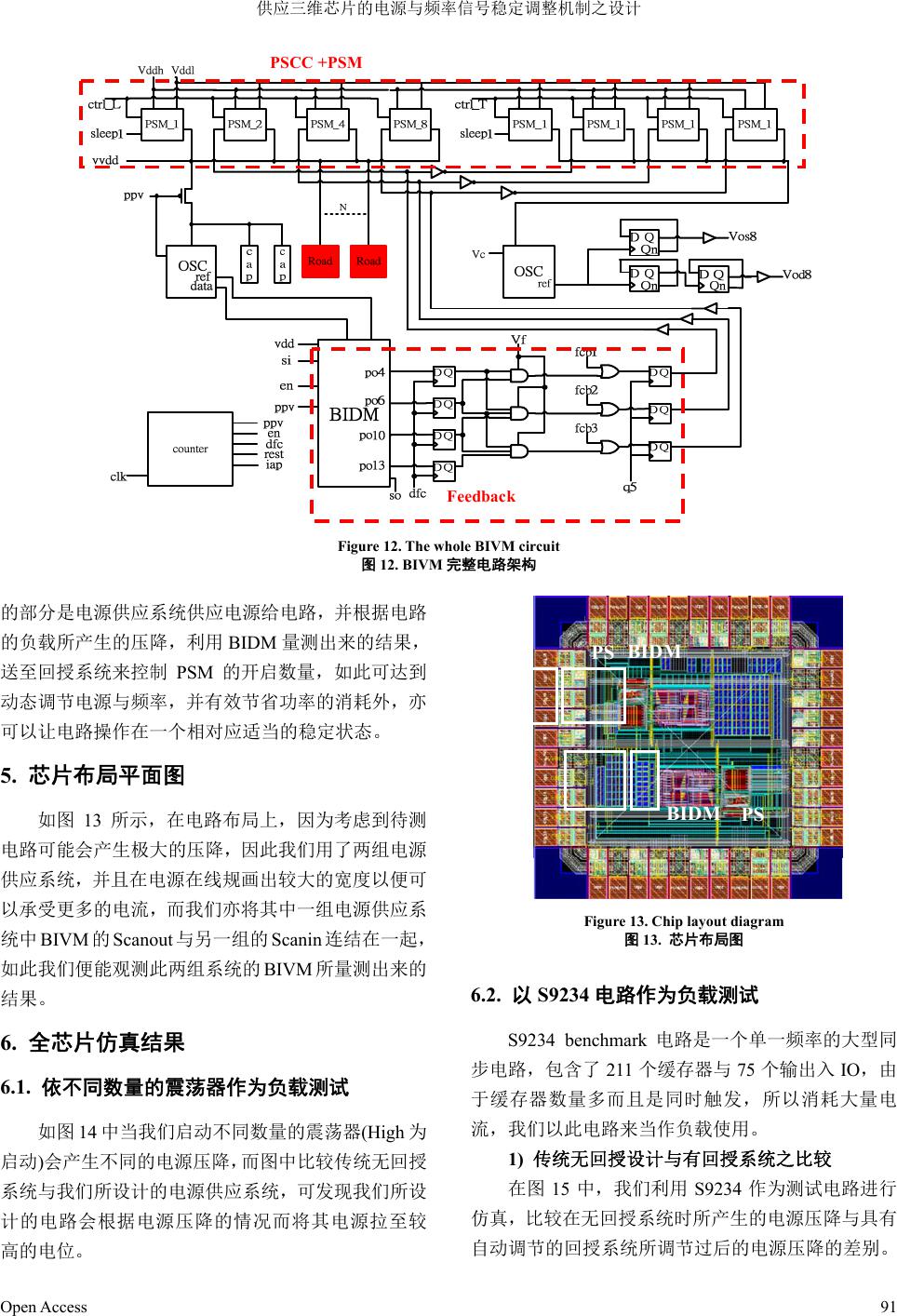

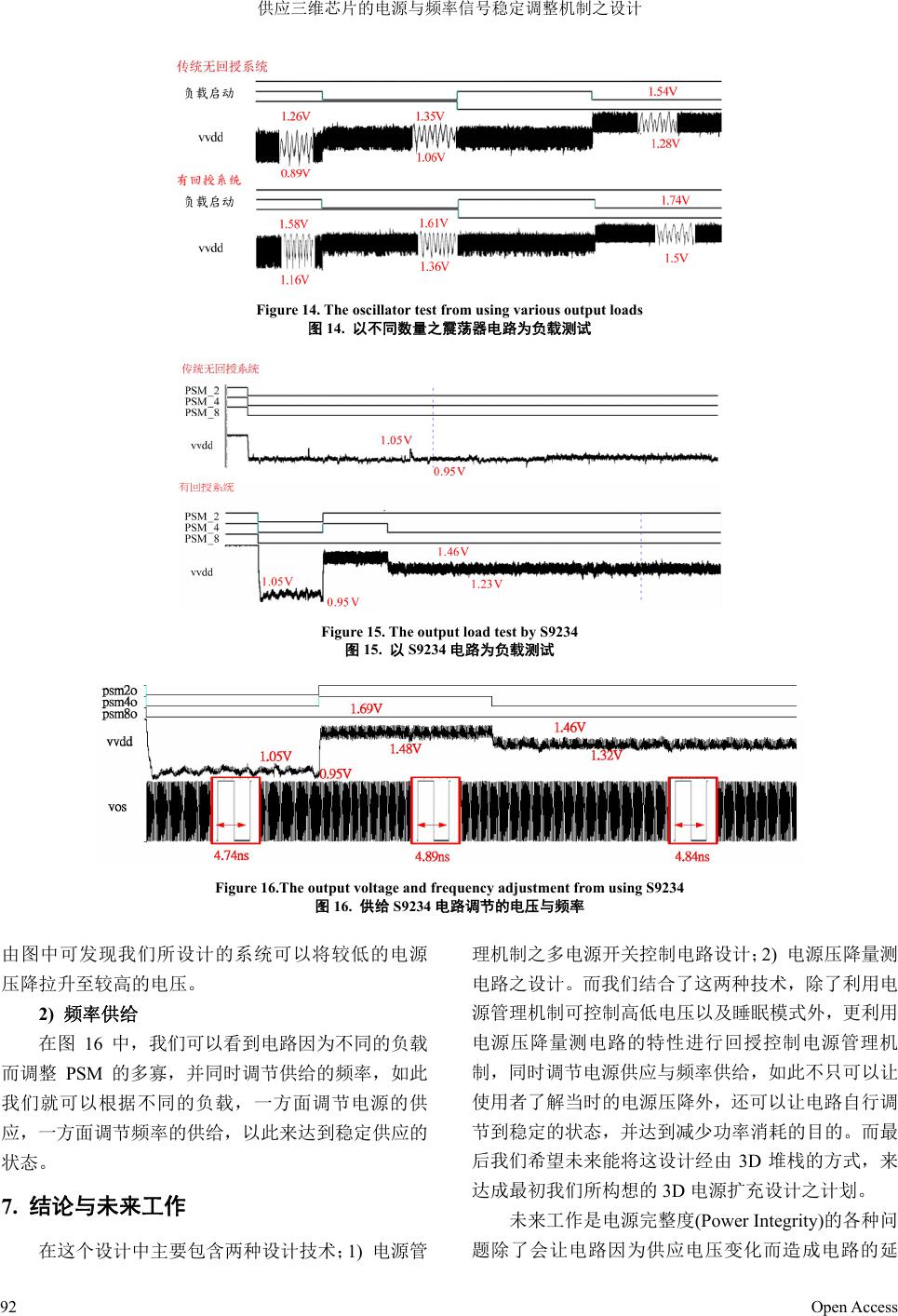

Journal of Electrical Engineering电气工程, 2013, 1, 84-93 http://dx.doi.org/10.12677/jee.2013.12018 Published Online December 2013 (http://www.hanspub.org/journal/jee.html) Open Access 84 A Supply Voltage and Clock Signal Stabilized Mechanism Design and Implementation for 3D Chip Sheng-Wei Hsu, Ching-Hwa Cheng Department of Electronics Engineering, Feng Chia University, Taichung, Taiwan Email: chengch@fcu.edu.tw Received: Oct. 22nd, 2013; revised: Oct. 29th, 2013; accepted: Nov. 12th, 2013 Copyright © 2013 Sheng-Wei Hsu, Ching-Hwa Cheng. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. In accordance of the Crea- tive Commons Attribution License all Copyrights © 2013 are reserved for Hans and the owner of the intellectual property Sheng-Wei Hsu, Ching-Hwa Cheng. All Copyright © 2013 are guarded by law and by Hans as a guardian. Abstract: This design includes th e voltage measurement, management and frequency stabilization mechanisms for 3D IC. The circuit voltage levels are sensed by the Built in Voltage Measurement circuit (Built-In Voltage Measurement- BIVM). From the voltage level measurement result, the feedback control circuit can decide the turned on PSM quanti- ties. However, the frequency supply to th e circuit need s to degrade in th is situation to prev ent the supplied vo ltage level from degrading con tinually. The feedb ack mechanism is to turn on less/more PSM and maintain th e voltage level stab i- lization. This mechanism allows the multi-core design stable operation, with regardless to the new circuit loading add ed to the system dynamically. The digitalized voltage and frequenc y stabilization mechanism are applied for the multi-core or the 3D staking design. Keywords: 3D Chip; Voltage-Frequency Adjustment 供应三维芯片的电源与频率信号稳定调整机制之设计 许胜伟,郑经华 逢甲大学电子工程学系,台中市 Email: chengch@fcu.edu.tw 收稿日期:2013 年10 月22 日;修回日期:2013 年10 月29 日;录用日期:2013 年11 月12 日 摘 要:本论文设计是结合 3D IC 的电源质量量测、电源管理机制技术与频率供给管理机制并进行芯片验证。 为了精确的评估所产生的电源问题,我们需设计了一个内嵌式的电压量测设计(Built-In Voltage Measurement- BIVM)来量测电压准位,了解电压降的情形,将电压降的情形侦测后再以数字方式来控制电源开关,以便调节 电压准位,以稳定电压供应,来做电源质量管理。我们利用控制 PMOS的Power Switch Module (PSM)的开启程 度来调节电压,更利用电源压降量测电路进行回授控制电源管理机制,同时调节电源供应与频率供给,如此不 只可以让使用者了解当时的电源压降外,还可以让电路自行调节到稳定的状态,并达到减少多核心或 3D IC 功 率消耗的目的。 关键词:3D 芯片;电压频率调整 1. 引言 因为 3D IC具有产品效能、减低功耗、降低成本、 缩小体积等优势,而且目前 3D IC主要是利用立体封 装技术来制作,可以减少因旧有 2D 因不同芯片的连  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 85 接所需较长的联机距离,如此可节省更多的空间,更 可节省打线,并带来更好的效能。目前随着三维芯片 的发展,其堆栈方式的不同主要可分为三种类别,第 一种是利用封装式堆栈,利用封装的技巧将多层芯片 封装在一起;第二种方式是利用wire bonding的方式 将多个裸晶串接在一起;第三种方式则是透过 TSV (through-the-silicon vias)直接将芯片穿孔,在芯片与芯 片间形成内部的金属联机,此方式有别于第二种方式 的外部联机,利用此方式可以有效降低金属导线长度 与复杂度,有利于芯片效能的提升与功率的减少。但 三维结构的各层间的频率、电源共享,因为各层间距 离近,以致各层晶粒间彼此间运作的干扰大,测试尚 须考虑其它层彼此间的关系,前人研究的测试功率问 题,频率歪斜的问题,在三维设计时更形严重。因此 电源与信号完整度及电源与频率管理机制设计是否 正常,便成为在三维芯片设计中极为重要的考虑。 因为 3D 结构将产生比传统的 2D 芯片有更为严 重的电源压降与电源干扰的电源完整性问题,该问题 主要探讨 IR-Drop、Ground-Bounce 等现象,其中瞬间 过大的尖峰电流所引起的 IR-Drop(Voltage drop)会造 成电路错误或延迟,并产生电子迁移(Electro migra- tion,EM)等现象而衍生可靠性问题。因此设计过程除 了要保证芯片的功能无误外,需要再额外考虑如电压 源下降 (Voltage drop)及地电弹跳 (Ground-Bounce)干 扰等问题,综合来说这些问题都是电流或电压源大幅 变化,以致造成电路功能不正确的问题。瞬间过大的 尖峰电流所引起的电压降的问题,除会严重影响组合 逻辑电路延迟时间的变化外,并引发循序电路产生时 间违反(Setup/Hold Time Violation)的情形。因为电源 完整度(Power Integrity)的各种问题除了会让电路因为 供应电压变化而造成电路的延迟或功能错误外,并进 而引起功率不当耗损,衍生出可靠性等种种缺失。 对于三维封装芯片的电源完整度的评估测试,未 找到合适的相关参考文献,文献索寻以功率为主的测 试技术仍然很少,有很好机会能做到创新研究。文献 [1-3]为现行使用电流镜暨红外线方式的电压降量测 方法两个方法,他们都可提供相当准确的量测结果, 但是此两设计的 Area overhead都很大,而且不易由芯 片外部进行观察。 在3D IC设计中的一个主要问题便是功率消耗大 的问题,依据功率消耗的公式:Pd = α‧CL‧VDD‧VDD ‧fclk 总功率消耗与电路中的转态机率 α、电容负载 CL、供应电源电压 VDD 与操作频率fclk 等因素有关, 其中 VDD 的因素影响最大。有效的低功率设计技术 是应用多电源供应的方法,我们将此双电源设计于 3D 芯片上,可依效能与功率消耗区分可为三段的调节模 式:高电压、低电压与休眠,因为双电源的设计,所 以3D 芯片上电压供应的管理与分布会更加的复杂。 因三维结构芯片(3D IC)将产生比传统的 2D 芯片 有更为严重的电源压降、电源干扰与频率信号偏移的 问题,因此如何有效的供应堆栈的芯片所需的各种电 源与维持稳定的频率信号便是极待解决的问题。3D IC 之电源因为各层不是一直在持续工作(有的进入休 眠模式,有的功能单元未使用),以至负载一直改变, 导致电源不稳定变化,频率信号偏移。 在论文中,我们提出一种新式的多电源与频率信 号供应机制,达成可控制的稳定电源与频率供给 3D IC 使用,使整个 3D IC设计电路的消耗功率得以有效 降低,及维持系统稳定工作。我们将设计一个可以针 对3D IC多电源结构的低功率设计技术,与电压质量 进行量测及调节稳定的稳定供给机制,此机制可根据 不同负载数量,而自动调节至所适合之电压供给三维 结构上的各芯片使用。 在稳定频率信号供给的部份系采用负回授的方 法,可稳定维持频率,不因负载数量变化而有大的改 变,而频率的调节部份则从控制另一组电压着手,可 提供较宽的频率调节范围给 3D IC使用。 为了解决 3D结构中的功率消耗与散热问题,我 们设计了新式的多电源管理机制,来使 3D 设计电路 的消耗功率得以有效降低。这个设计一个可以针对 3D 多电源结构的低功率设计技术与电压质量进行量测 的机制。本设计是结合电源质量量测、电源管理机制 技术与频率供给管理机制并进行芯片验证。电源质量 的量测机制具有灵敏的线性特性,电源管理机制可由 量测机制控制电源供给达到根据不同负载而自动调 节至所适合之电源供给,而频率供给的部份则具有不 错的调节范围可供使用。 在电源的供应上,因为每个芯片所能提供的电源 是有限的,所以可能会发生负载过大导致供应的电压 不足。为了解决这个问题,在我们所设计的芯片是具  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 86 有可扩充的性质,利用多颗芯片的电源供应端共同供 应电源给待测电路使用,如此即可避免待测电路因为 单颗芯片所能供应的电源过低而无法正常工作的情 况,而利用这种方式并不会影响电路内部的电压量测 机制,每颗芯片都能自行调整并提供最适当的电压。 在频率的供应上,利用电压的量测机制回授给电 压调节系统外,也利用负回授的方式传至频率调节 上,然而在产生频率的震荡器设计上,有别于其它设 计是利用监控系统来自动大幅度调整频率,此设计的 震荡器是属于小幅度的调整,如此可以避免电压跟频 率因两者同步调整而可能会产生无法稳定输出。然而 在频率的调节上,利用改变供应给震荡器的电压来初 步选定频率的供给范围,再利用内部的自动微调系统 让频率达到适当位置。 由于此设计在电压与频率的调节上是个别利用 独立的电压系统,因此在使用上会无法利用切换机制 来调节高低电压的供应,因此在设计时考虑到如要使 芯片可切换电压来达到节省功率的效用时,可以利用 芯片迭接的方式来达到切换高低电压的功用,此迭接 方式除了可以利用在电压调节机制上,亦可进一步的 使用到频率调节机制上来达到更宽带的设计。 为了精确的评估 3D IC所产生的电源问题,我们 需设计了一个内嵌式的电压量测设计(Built-In Voltage Measurement-BIVM)来量测电压准位,了解电压降的 情形,将电压降的情形可以透过 scan chain以数字方 式来控制电源开关,以便调节电压准位,以稳定电压 供应,来做电源质量管理。这个设计机制可以提供 3D 结构上的电源供应,结合电源管理机制来维持每层的 电源稳定度,改善各层结构因电源不稳定造成操作效 能问题。 在本论文中,我们将完成一个堆栈式的 3D IC电 源供应系统的验证,先以 2D 芯片为规划设计,下线 后将其 2D 芯片再堆栈成 3D 芯片以达到根据其压降 来控制电源供应而后达到稳定供电的功用,如图 1所 示。 2. 相关研究发展现况 动态调整电压和频率技术:Dynamic Voltage and Frequency Scaling (DVFS)技术我们知道动态功率消 耗与电源电压平方成正比,因此调降电源电压所获得 的降低功率消耗效率是最高的。我们若以微处理器 (microprocessor)执行程序为例,并非每一段时间都必 须要全速运算,因此对整个微处理器都供给同一高电 压原,便造成功率的浪费。若是利用降低操作速度来 达到减少功率消耗的目的,又会影响系统的效能速度 变慢,如图 2所示。中,所以降低操作频率(如虚线) 会使运算时间变长,因而可能并没有减少能源的消 耗。 但若是能做到视个别操作运算需求,图 3与图 4 提供所示之相对应的电源电压,也就是用动态调整电 源电压的盖念,分别对不同的操作程序,设定适当的 供应电压,以达到最大的降低功率消耗的效果。 Figure 1. The BIDM measurement structure for 3D chip 图1. 以BIVM 为主题的三维芯片结构图 Desired Throughput tim e S y ste m id leB ackground and Long-latency processes C om pute-intensive and Short-latency processes Figure 2. The microprocessor operation status diagram 图2. 微处理器的运作图标 Delivered Throughput time Frequency Set by user 80 MIPS Slow Fast Fclk Reduced Figure 3. Frequency degradation process 图3. 降频微处理器运作图  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 87 Figure 4. Dynamic voltage frequency scaling 图4. 动态调整电压电源回授电路图 3. 架构简介 依据功率消耗的公式:Pd = α‧CL‧VDD‧VDD‧ fclk 总功率消耗与电路中的转态机率 α、电容负载CL、 供应电源电压 VDD 与操作频率 fclk 等因素有关,其 中VDD 的因素影响最大,为了维持芯片在相同的效 能下工作,以便评估消耗电流多寡,所以我们就应用 多电源供应的方法,以便测试时可以量测电为组合变 化的多种情形。我们将此双电源设计在量测芯片上, 用以量测电源稳定度,依效能与功率消耗区分可为三 段的调节模式:高电压、低电压与休眠,因为双电源 的设计,所以待测芯片上电压供应的管理与分布会变 更加的复杂。 量测电源的稳定度除了可评估电压压降的情形 外,还可以评估其对于电路效能造成的影响来加以衡 量,因为多电源供应机制在供应高电压所造成的电路 延迟都比供应低电压时小,因此我们可以根据此改变 来了解电压准位的变化。 此设计主要分为两个部分,如图 5所示。一个是 电压源供应自动调节机制,当负载有所变动时,电路 可根据回授系统自动调节到适当的电压源供应。另一 个则是频率供给调节机制,可依据电源供应系统所产 生的结果来调节频率供给快慢,而也可自行调节电压 来达到不同需求之频率。 3.1. 电压调节机制之设计 是我们利用控制 PMOS 的Power Switch Module (PSM)闸级电压来达成 Power Switch (PS)的开启程度, 因为如果提升 PMOS 闸极电压,就会使得 PMOS input 原本的 low 信号变成不是0 v,而是 control 的电压, 因为 Power Switch的输入电压如果是在 0 v的话,就 会完全地打开。但是调整并提升 control 电压,就会使 得Power Switch并不是完全地打开,所以产生的电流 也就变小,利用这一点就可以对 PS做小范围的微调。 PS control电路功能是控制 PS 开启的个数,这样子就 可以做大范围的调整,如果电路的效能不够的话,就 可以开启较多的 Power Switch提供充足供应电压源, 但如果想要节省更多的功率,就可以开启较少的 PSM,从控制 PS的数量来达到电压调整的效果,PS 的数量采 1、2、4、8个为群组的方式构成,控制这 些PSM 群组的组合方式,便可达成相当于电压调整 的效果。这样子就可以在维持相同的效能之要求下, 供一个弹性可规划的电压源的电路设计,可以让使用 者选用不同的效能与功率消耗模式,如图 6所示。 数字式的 Voltage Regulator的设计想法:是利用 并联的 PMOS 数量来决定 PMOS的Size 以W = 1、2、 4、8为例即可组合成 15 种不同的电阻,我们利用这 个Size 微关系组合成16 种电流信道,以此来控制 Virtual Vdd那点的电压,另一个方法是使用 Charge sharing 的原理来控制PMOS 的通过电流量,控制 PMOS 进入 Linear 操作区域即可达成此项效果。 1) Power Switch Module的设计 Power Switch Module (PSM)是一种双电源开关, 可以使电路工作在两种不同的高准位上。ㄧ般开关电 路在开关(MOSFET)瞬间,会出现高的峰值电流,造 成功率消耗上升。但是,开关时大的尖峰电流损耗对 于一个开关电路来说,是最关键的问题,为此设计了 开关控制电路。 vddh 与vddl 为可理想供应电源,可分别供应两 种不同准位之电压,因利用 PMOS作为开关使用,每 个PMOS 所能经过的电压源有所限制,因此利用了多 个PMOS 并联以达到可以传送更多的电压 源避 免因 PMOS 的数量限制而导致电源供应不足。  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 88 Figure 5. The design circuit structure 图5. 总电路方块图 Figure 6. The power switch circuit 图6. Power Switch设计电路 2) Power Switch Control Circuit (PSCC) 在理想上,双电源开关(PSM)在切换时,一边打 开另一边即为关闭,但是在实际上在切换瞬间会因为 短暂的 delay time,造成 DPS同时为 ON的状况,因 此会造成非常大的锋值电流,从高电压源流向低电压 源因而可能造成电路 DPS 烧毁,为此,设计了控制电 路,为了确保 DPS 的切换时是可以一开一关的状况, 避免电路烧毁与多余的功率消耗,因而设计了 Power Switch Control Circuit (PSCC)来解决此问题。 3.2. 电源量测调节机制之设计 1) 电容控制 在环形震荡器的电源供应就是利用电容将电压 源在 PMOS打开的时候暂时储存在电容中,当 PMOS 关闭后,利用电容中的电压源供应给震荡器使其可以 运作,并在运作的同时量测其值送至 BIDM(Built-In Delay Measurement)进行处理。 在Ctrl 这个控制讯号是控制电容是否要充放电, 在phi 开启的时候,ctrl也会跟着开启使电容可以充 电,而当 phi 关闭后,ctrl 也会跟着转换讯号使得电容 可以将电荷归零,避免下次量测时出现因电容放电不 完全而导致量测出来的数值有所偏差。 2) 环形震荡器 当理想电源经过 PSCC 与所挂载的电路后,会造 成一定的压降,导致电路所需的电压源并未达到其应 有的准位,因此先利用一个 PMOS 作为电压源的取样 开关,并让挂上的 MOS 电容纪录当下的电压值,在 PMOS 开启时对电容进行充电后,再将 PMOS 关闭, 此时电容所储存的电压值即是当时量测电路的电压 值,利用电容所储存的电压提供给震荡器作为电源的 供给,因为不同的电压会改变震荡器的震荡频率,利 用这个特性 BIDM 会将环形震荡器(ROSC)的n4 与n0 这两级的时间差纪录下来并进行处理后由 Scanout 输 出,便可得到数字化的时间差量数据,然后再利用产 出的时间差量数据反推回去内部电路的电压源的电 压值,如图 7所示。  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 89 Figure 7. The ring oscillator and BID M c ircuit 图7. 环形震荡器与 BIDM 的关系图 3) BIDM (Built-In Delay Measureme nt) BIDM 的量测是利用两个讯号间的延迟差异,经 由D flip-flop的处理,如果两者间的差异时间超过一 定的距离,则粗调会变化成ON,反之如果两者的差 异时间小于 D flip-flop所能处理的时间差则不会有所 变化,即为 OFF;当粗调讯号已无法继续分析讯号间 的延迟差异,则会将讯号送至细调部分,利用更精确 的运算得到更详细的分析结果,最后可根据量测出来 的粗调与细调结果反推两讯号间的时间延迟差异,如 图8所示。 需要注意的是,因为是用电容记忆电压值,当 PMOS 开关关闭后,不马上量测其电容的电压就会自 己逐渐放掉,导致无法量到最准确的电压值,所以最 好是将开关关掉后就马上进行量测振荡时间差量,否 则会丧失准度。 4) 回授系统 当BIVM输出后,除了可以量测当时的电压源外, 更可将其输出的值经由回授系统将讯号处理过后传 送回 PSCC 的Sleep 端控制 PSCC 是否开启,如果开 启则会增加电源供应以提高电压,如未开启则表示现 阶段电压已达到一个基准值,并不需要开启更多的 PSCC 而造成多余的功率消耗。 利用 BIVM 处理过后的结果,从其中选取四个粗 调讯号当作回授系统的输入,先利用 D flip-flop撷取 所需的讯号后经由逻辑闸决定是否开启相对应的 PSCC。 在电路中 另外设计了 两种可由外 部调节的机 制以便应付不同需求与情况发生,Vf 的设计是要利用 charge sharing 的电路特性可藉由调节Vf 的电压值来 控制其逻辑闸的输出值,而fcb 是可由外部去强制控 制PSCC 是否开启的设计,当fcb 为1时即为外部强 制开始 PSCC,当fcb 为0时则交由电路内部本身的 讯号去控制PS CC,让电路具有可调整的功能,如图 9所示。 3.3. 设计一个稳定频率供应调节 频率的产生是利用电压供给震荡器后震荡出来 ROSC Figure 8. The detailed BIVM circuit 图8. BIVM详细电路图  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 90 的波型,因不同的电压供给会产生不同的震荡频率, 利用此特性可以产生多种不同的频率供给外部使用, 而因震荡器也会使得电压源供应有压降,所以在电压 源的供应上也设计了四组PSCC 利用回授系统去控制 开启的数量来达到频率调节功能。在电路的实际仿真 后,因震荡器所产生出来的频率较高再加上了两组分 别为两倍与四倍的除频器,将频率降至外部电路可以 使用的范围内,如图 10所示。 系统频率控制电路 计数器的设计主要是用来产生一些电路内部的 控制讯号,在设计上利用了五个D flip-flop所产生的 计数器可以产生 32 个Clock为一个周期的完整波形, 利用每个 D flip-flop所产生不同的周期讯号加上简单 的基本逻辑闸,即可产生数种不同的讯号,如此即可 供应给电路内部而不用将其讯号端拉至外部控制,这 样可以减少多个原本需由外部控制的讯号,让 IC 的 Pin 能更有效的利用,如图 11 所示。 4. 芯片电路详图 在整体电路上,如图 12所示。首先在PSCC + PSM Figure 9. Feedback circuit 图9. 回授電路 Vc DQ DQ Qn Qn DQ Qn Vos8 Vod8 Inverter * 8 PSCC vddh vddl Figure 10. The frequency adjustment circuit 图10. 频率调节电路图 Figure 11. The control signal generated by coun ter 图11. 计数器与所产生的讯号  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 91 PSCC +PSM Feedback Figure 12. The whole BIVM circuit 图12. BIVM完整电路架构 的部分是电源供应系统供应电源给电路,并根据电路 的负载所产生的压降,利用 BIDM量测出来的结果, 送至回授系统来控制 PSM 的开启数量,如此可达到 动态调节电源与频率,并有效节省功率的消耗外,亦 可以让电路操作在一个相对应适当的稳定状态。 5. 芯片布局平面图 如图 13 所示,在电路布局上,因为考虑到待测 电路可能会产生极大的压降,因此我们用了两组电源 供应系统,并且在电源在线规画出较大的宽度以便可 以承受更多的电流,而我们亦将其中一组电源供应系 统中 BIVM的Scanout与另一组的 Scanin连结在一起, 如此我们便能观测此两组系统的 BIVM所量测出来的 结果。 6. 全芯片仿真结果 6.1. 依不同数量的震荡器作为负载测试 如图 14 中当我们启动不同数量的震荡器(High 为 启动)会产生不同的电源压降,而图中比较传统无回授 系统与我们所设计的电源供应系统,可发现我们所设 计的电路会根据电源压降的情况而将其电源拉至较 高的电位。 PS BIDM BIDM PS Figure 13. Chip layout diagram 图13. 芯片布局图 6.2. 以S9234 电路作为负载测试 S9234 benchmark电路是一个单一频率的大型同 步电路,包含了211 个缓存器与 75 个输出入IO,由 于缓存器数量多而且是同时触发,所以消耗大量电 流,我们以此电路来当作负载使用。 1) 传统无回授设计与有回授系统之比较 在图 15 中,我们利用 S9234作为测试电路进行 仿真,比较在无回授系统时所产生的电源压降与具有 自动调节的回授系统所调节过后的电源压降的差别。  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 92 Figure 14. The oscillator test from using various output loads 图14. 以不同数量之震荡器电路为负载测试 Figure 15. The output load test by S9234 图15. 以S9234 电路为负载测试 Figure 16.The output voltage and frequency adjustment from using S9234 图16. 供给S9234 电路调节的电压与频率 由图中可发现我们所设计的系统可以将较低的电源 压降拉升至较高的电压。 2) 频率供给 在图 16 中,我们可以看到电路因为不同的负载 而调整 PSM 的多寡,并同时调节供给的频率,如此 我们就可以根据不同的负载,一方面调节电源的供 应,一方面调节频率的供给,以此来达到稳定供应的 状态。 7. 结论与未来工作 在这个设计中主要包含两种设计技术;1) 电源管 理机制之多电源开关控制电路设计;2) 电源压降量测 电路之设计。而我们结合了这两种技术,除了利用电 源管理机制可控制高低电压以及睡眠模式外,更利用 电源压降量测电路的特性进行回授控制电源管理机 制,同时调节电源供应与频率供给,如此不只可以让 使用者了解当时的电源压降外,还可以让电路自行调 节到稳定的状态,并达到减少功率消耗的目的。而最 后我们希望未来能将这设计经由 3D 堆栈的方式,来 达成最初我们所构想的 3D 电源扩充设计之计划。 未来工作是电源完整度(Power Integrity)的各种问 题除了会让电路因为供应电压变化而造成电路的延  供应三维芯片的电源与频率信号稳定调整机制之设计 Open Access 93 迟或功能错误外,并进而引起功率不当耗损,衍生出 可靠性等种种缺失,因此在测试时,利用此论文介绍 电路去分辨电源完整度的电源管理机制设计是否正 常,便成为在三维芯片三维封装芯片设计中极为重要 的考虑。 参考文献 (References) [1] Fukazawa, M., Noguchi, K., Nagata, M. and Taki, K. (2006) A built-in power supply noise probe for digital LSIs. IEEE Asia and South Pacific Design Automation Conference, Yokohama, 24-27 January 2006, 106-107. [2] Rusu, S., Seidel, S., Woods, G., Grannes, D., Muljono, H., Row- lette and Petrosky, K. (2001) Backside infrared probing for static voltage drop and dynamic timing measurements. Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC. 2001 IEEE International, San Francisco, 7 February 2001, 276-277. [3] Shimazaki, K., Nagata, M., Okumoto, T., Hirano, S. and Tsuji- kawa (2005) Dynamic power-supply and well noise measure- ments and analysis for low power body biased circuits. IEICE Transaction on Electronics, E88-C, 589-596. |