Optoelectronics

Vol.06 No.02(2016), Article ID:17751,8

pages

10.12677/OE.2016.62007

Research of Brain EEG Wireless Radio Transmitter IC System for Wearable Application

Jianhui Sun1,2*, Juntao Liu1,2, Mixia Wang1,2, Shengwei Xu1,2, Xinxia Cai1,2#

1State Key Laboratory of Transducer Technology (North Base), Institute of Electrics, Chinese Academy of Sciences, Beijing

2Chinese Academy Sciences of University, Beijing

Received: May 20th, 2016; accepted: Jun. 3rd, 2016; published: Jun. 6th, 2016

Copyright © 2016 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

Focus on the brain EEG (electroencephalograph) transducer network short range transmitting and wearable application, the design gives an integrated wireless controlling system which is composed by analog circuit (eight-channel EEG low-noise amplifier and intermediate speed SAR-ADC), wireless channel coding EEG-DSP accelerator, low-power and robust radio frequency chip. At the ISM-2.4 GHz frequency band, the radio frequency chip uses the radio frequency direct-up-conversion architecture, with FSK/OOK data modulation method. The design has optimized the frequency synthesizer based on PLL, the PA’s outputting power (4 - 5 dBm), PAE (power added efficiency: 25%), S-Parameters have been optimized too. The pipeline EEG-DSP is responsible for the whole system’s controlling, data storage, reduced wireless channel coding and bit-stream outputting. The design uses the Cadence Co’s SpectreRF, Synopsys Co.’s serial logic-design tools, Caliber Co.’s tool to complete the function verify/physical layout signoff. These chips have been manufactured by the SmicRF180 nm analog/digital mixed technology, and the back’s chips test results show that the EEG-DSP and RF chip’s critical parameters satisfy the expected proposed requirements.

Keywords:Brain EEG, Mixed Analog/Digital IC Design, FSK/OOK, Radio Frequency Direct-up-Conversion, Phase Noise, Pipeline DSP Hardware Accelerator

脑电可穿戴无线射频发射芯片系统的研究

孙建辉1,2*,刘军涛1,2,王蜜霞1,2,徐声伟1,2,蔡新霞1,2#

1中国科学院电子学研究所,传感技术联合国家重点实验室(北方基地),北京

2中国科学院大学,北京

收稿日期:2016年5月20日;录用日期:2016年6月3日;发布日期:2016年6月6日

摘 要

针对脑电EEG (electroencephalograph)传感网络近距离无线传输与可穿戴应用的需要,给出了一款无线射频电路控制系统:集成了模拟电路(8通道低噪声脑电放大器与中速SAR-ADC模数转换)、信道编码EEG-DSP加速器、射频发射芯片。在ISM-2.4 GHz波段,射频物理层使用射频直接上变频架构,通过FSK/OOK (on-off-keying)的数据调制方式;重点优化基于PLL的频率综合器(PLL-FS)与可开关的E类功率放大器(PA-E);PLL-FS具有低相位噪声(−119 dBc/Hz@1 MHz)、锁定时间短(28~60 us)、环路特性好的特点;PA优化了输出功率(4~5 dBm)、功率增加效率PAE(25%)、S-参数等。流水EEG-DSP负责整体系统控制、数据缓存、精简无线信道编码以及输出码流调制射频电路。设计利用Cadence Co.的SpecterRF软件、Synopsys Co.的系列数字软件/Caliber软件进行了功能仿真/物理版图验收,设计使用SmicRF180 nm数模混合工艺进行了加工,流片回来的测试结果表明EEG-DSP与射频发射芯片可以满足实际应用。

关键词 :脑电EEG,数模混合芯片设计,FSK/OOK,射频直接上变频,相位噪声,DSP流水硬件加速器

1. 引言

由于国家“脑健康”的要求,针对癫痫、抑郁等脑疾病的预警治疗的要求 [1] [2] ,自主研发了该款“多通道无线EEG脑电检测芯片”。随着移动生物医疗的发展,人体医疗数据的实时安全高效的无线传输成为研究的热点。传统的设备没有考虑检测的脑电数据可以无线发送到附近基站或者手机上,导致使用者不能够随意移动。此外,可穿戴要求脑电设备的体积要小,但是,传统的设备的体积很大,其没有把尽可能多的IP集成在一起。例如,Neural Scan公司的脑电检测产品,体积庞大,不适合可穿戴场景使用;传统的设备,也没有把系统的能量消耗,作为重要的设计因素进行考虑,由于设备电池的续航时间越长越好的要求,低功耗的设备或者系统变得越来越重要。例如,ADI公司的ADS1299芯片里面使用了8路放大器,每路后面连接着一路ADC电路,功耗变大 [3] 。同时,随着智能脑电穿戴设备的迅速发展,服务于脑电传感数据处理的DSP硬件加速器芯片已经具有迫切的需求。例如,麻省理工大学在2009年,针对癫痫病在线分析,设计了一款集成了chopper-LNA、ADC、processor的SOC,进行癫痫病特征波形的提取,以降低发射功耗,这类芯片是未来的智能脑电设备的发展趋势;目前国内类似智能脑电SOC产品的研发处于起步阶段。该文针对以上存在的几个主要问题,自主研发了面向可穿戴应用的高性能普适性脑电检测编码发射器。该文对射频电路的一系列关键指标进行了优化,包括面积、能耗、噪声抑制、带宽、效率、数字可调、抗干扰能力等,同时兼顾硬件电路的设计复杂程度和成本。EEG-DSP加速器芯片,则可以灵活对系统整体进行灵活控制管理与参数重新配置,弥补了模拟与射频电路固化不变的缺点。同时,考虑数字逻辑,会对模拟射频造成很大的信号耦合干扰,因此在设计时考虑信号完整性。

2. 无线射频控制电路

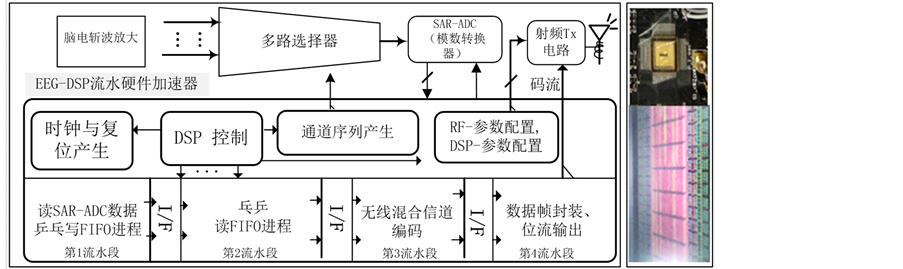

如图1所示,其为脑电检测与无线发射整体结构。前端脑电传感器连接到低噪声脑电斩波放大器,斩波放大器用于去掉低频1/f闪烁与输入失调等噪声,以提高脑电微弱小信号(10~100 uV, <100 Hz)检测精度;8通道放大后的几百mV级的模拟信号送到SAR-ADC (逐渐寄存器逼近–模数转换器),进行后续的模拟到数字转换操作;转换后的数字信息通过EEG-DSP进行FIFO缓存、乒乓矩阵切换写入/读出,混合信道编码后的有效数据添加帧头、帧尾、同步字、CRC校验字后、输出基带码流,以调制射频电路的PLL-FS或者PA-E电路,进行射频领域的FSK或者OOK的调节。

2.1. 流水EEG-DSP硬件加速度器

2.1.1. 流水EEG-DSP的介绍

如图2左侧所示,其为EEG-DSP的整体架构。4段流水EEG-DSP负责选择某路放大后的模拟脑电EEG信号,送到ADC进行数字量化。EEG-DSP为ADC提供工作时钟,获取ADC输出的数字总线数据,存储在本地近似无穷大FIFO。DSP 对射频电路进行参数重新配置(包括OOK/FSK模式选择、PA的带宽配置、PLL-FS的频率带选择、特定频带的频点配置、分频器的分频字配置、功率放大幅度配置)。4段流水线分别是:阶段-1:获取来自ADC的数据;阶段-2:乒乓读出FIFO数据;阶段-3:无线信道编码;阶段-4:数据帧封装。EEG-DSP加速度芯片对于以后的海量脑电数据提速以及流水段指令化处理有益。图2右侧下方是EEG-DSP芯片的版图,上方是芯片封装后照片。

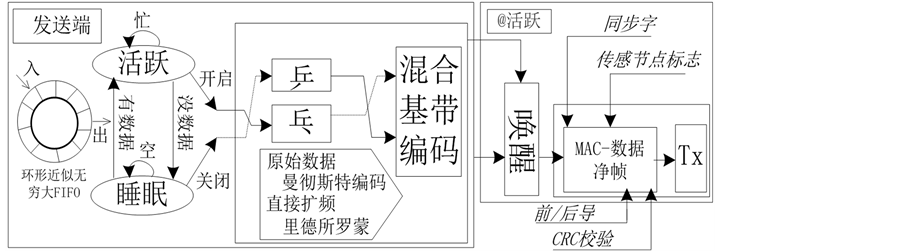

如图3所示,其为设计的精简点对点通信网络的架构;其工作原理是:当FIFO内部数据半满,则传感网络唤醒,其处于活跃状态,否则,网络处于睡眠状态;唤醒后,利用乒乓矩阵切换机制,交叉分时把乒或乓的数据发射到混合信道编码模块,进行后续信道增益编码;编码后的数据进入后续MAC(媒体访问层)进行数据封装(对原始净数据,添加同步字、前/后导、CRC校验字、传感节点标识),最终,码流输出以调制射频电路PLL-FS的频率控制字(FSK)或PA-E(OOK)的开关管。

2.1.2. EEG-DSP混合信道编码

如图3中间所示,EEG-DSP采用自行设计的精简的信道编码策略:1) 不进行有效数据的信道冗余

Figure 1. Micro EEG signal high resolution detection, analog/digital conversion and wireless radio transmitter chip system

图1. 微弱脑电检测、模数转换与无线射频发射芯片系统整体

Figure 2. EEG-DSP controlling circuit, 4-stage pipeline structure

图2. EEG-DSP控制电路、4段流水线结构

Figure 3. Brain neural reduced wireless network architecture

图3. 脑电精简无线网络架构

编码,只添加前/后缀、帧头同步字、数据包采用CRC-16冗余校验码;2) 净数据采用曼彻斯特编码,数据编码效率是50%;3),使用直接序列扩频 (DSSS:Direct Sequence Spectrum Spread)方法进行去相关扩频编码,该方法通过搜寻存储在本地的LUT-(4bits索引,16bits扩频后码长),以节省硬件资源,提高速度,编码效率是25%;4),利用前向纠错编码采用(1symbol = r bits = 6 bits,N = 31 = 2r − 1,K = 19,t = N − K = 2 t = 12)的里德–索罗蒙(Reed-Solomn)编码,每个符号占据6 bits (r = 6),其可以纠正6(t = 6)个不连续的错误符号,编码效率是19/31 = 61.3%。EEG-DSP硬件加速编码器在以上4种方案中采取一种进行信道编码实现。

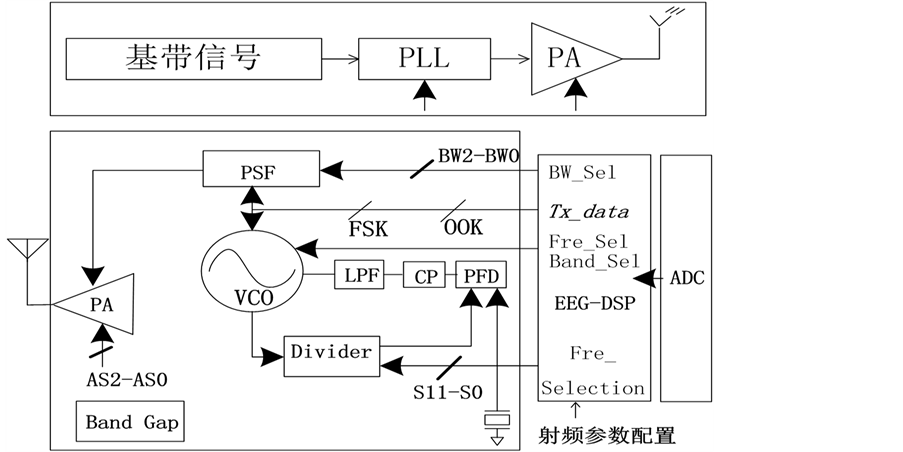

2.2. 直接上变频架构的射频发射芯片

如图4所示,直接上变频的物理层射频电路结构 [4] ,主要模块包括PLL-FS与PA。该设计的脑电可穿戴设备的感知节点需要布置在人体头部表面,其需要使用电池供电;考虑系统复杂度与硬件成本,低功耗、高速率、高集成度是射频电路设计的目标。VCO通过频率控制字(Fre_sel[2:0])进行8个频带的选择,此外,通过6位频率控制字(FSK调制)进行特定频段上的工作频点的选择 [5] ;此外,分频字(Fre_sele., S11-S0)进行分频器分频比的控制。PA-E的输出功率通过功率控制字进行PA-E输出幅度的控制。

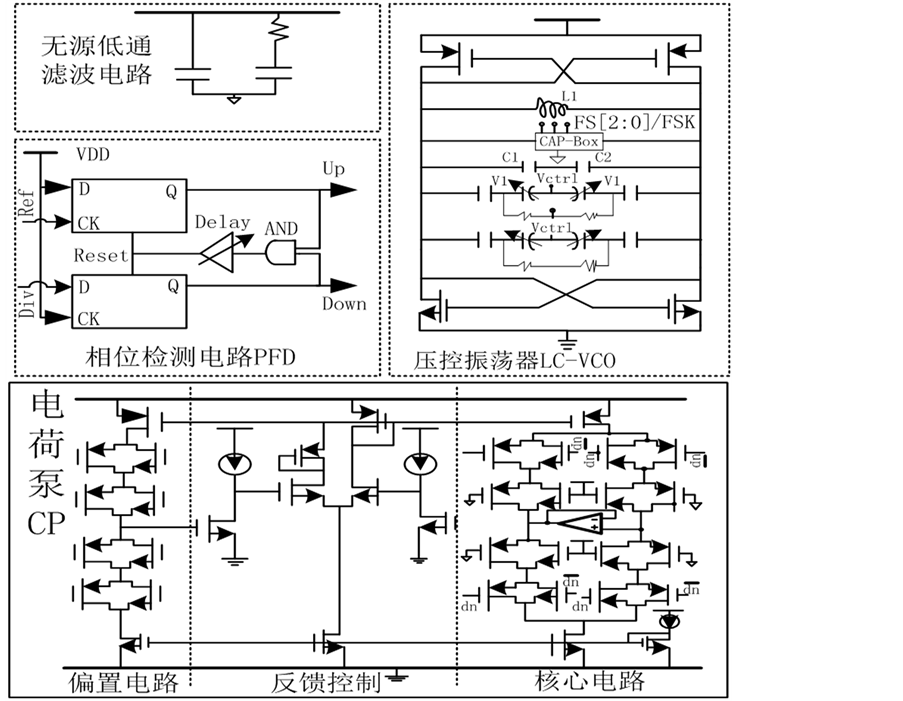

2.2.1. PLL-FS电路的设计

PLL-FS具有频谱纯净、易于集成、功耗低等特点 [6] 。如图5右上角所示,FSK调制通过关断锁相环内的开环VCO电容阵列,VCO的变容管电容随着控制电压Vctrl改变而改变,进而改变输出信号的频率与相位。VCO通过增加电容阵列的数目来扩大VCO的调频范围,从而避免Vctrl控制变容器引起的非线性问题。分频器输出的频率与输入参考频率进行相位比较,相位差通过PFD转换为开关时间差,经过

Figure 4. Radio frequency directed up-conversion structure based on OOK/FSK modulation mechanism

图4. 直接上变频结构的OOK/FSK调制射频电路

Figure 5. PLL’s PFD, LPF, VCO and CP circuit

图5. PLL的相位检测、低通滤波器、压控振荡器、电荷泵电路

CP转换为模拟电荷量,再经过LPF转换为Vctrl。PLL内部的反馈机制,调节VCO的输出,使得相位差减小,最终达到锁定状态。在稳定状态,Vctrl保持固定,VCO输出信号频率与输入信号相位、频率一致。VCO互补型结构采用两对交叉耦合的PMOS与NMOS管提供负阻,电路利用率提高,输出电压幅度较大且对称性较好,因此可以很好的均衡功耗与相位噪声2个指标。LC-VCO的振荡信号是PLL的最终,通过减少VCO中有源器件的闪烁噪声、提升振荡信号能量、降低1/f3区域噪声的拐角频率和增加谐振网络的品质因子Q来降低VCO相位噪声。锁定时间与环路带宽呈正相关;设计的PLL是个三阶系统,具有三个极点与一个零点。其传输函数可以简化为自动控制理论形式,如公式(1)所示,其中ωn为自然频率,ζ为阻尼因子。

(1)

(1)

如图5左上角所示,PFD需要对差分信号Up、Down进行延时平衡;同时,在PFD的复位回路中添加延时单元,避免环路在锁定状态下的死区。考虑沟道长度调制、电荷注入、时钟馈通、电荷共享等效应,CP电路的充放电电流需要进行充分匹配。PLL的总相位噪声由各部分噪声源叠加而成,总噪声决定输出频谱以外的频谱能量,将频偏处的相位噪声定义,如公式(2)所示:

(2)

(2)

如公式(2)所示,P1表示频偏1 Hz带宽内的能量,P0表示载波能量。PLL的相位噪声:输入噪声Θn,i、鉴频鉴相PFD(Θn,pfd)、电荷泵CP噪声(Θn,cp)、分频器Divider噪声(Θn,div)呈现低通特性,而压控振荡器VCO噪声呈现高通特性;由于PLL环路带宽较大时,相位噪声决定于VCO;PLL环路带宽较小时,相位噪声决定于CP与PFD。PLL环路带宽越大,越可抑制VCO与LPF的相位噪声;PLL-FS采用LC振荡器,其相位噪声性能较好,因此PLL-FS采用较低的环路带宽抑制CP和PFD的相位噪声。CP的泄露电流与失配、PFD时域失配均可引起参考频率整数倍处的参考杂散;通过降低环路带宽,增加Icp,降低Kvco,改善参考杂散(位于参考频率整数倍处的噪声)。

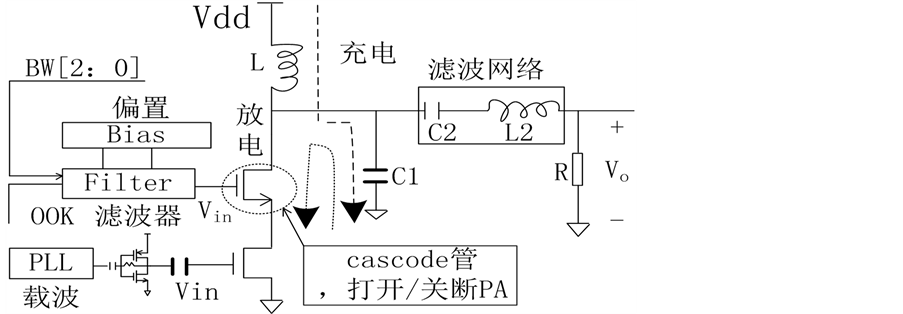

2.2.2. PA-E电路设计

OOK调制通过控制功率放大器内部级联管(cascode管)实现,调制速率通过改变BW[2:0]来改变滤波器带宽。

低功耗的脑电传感网络应用场景要求低输出功率并且高的功率增加效率PAE,要求小的尺寸;如图6所示,电感L提供了MOS管至电源的通路,电容C2与电感L2组成滤波网络,C1与MOS管并联,并且在开关模式下实现充电与放电过程。PA-E导通角为180度,增益小,输出功率大,最大效率100%,线性度较差,适用于调频FSK模式,集成度好。选择的3阶巴特沃斯滤波器具有阻带抑制高,通带平坦,相位特性接近线性等特点;通过电容阵列实现滤波器的多带通调节。输入通过缓冲BUF为第二级提供一个大摆幅输入信号;第二级为放大级,包含放大管、OOK调制管与阻抗匹配网络。阻抗匹配网络由片上电感L、片上电容C、片外键和电感L2、片外键和电感C2组成。偏置由片上电路组成,一方面,避免了电阻分压引入的热噪声,同时减少了电流抖动;另一方面,提高了集成度,降低了功耗。如图7左侧所示,其为基于PLL-FS与PA-E电路模块的射频发射芯片版图;如图7右侧所示,其为设计的射频发射电路。

2.3. 信号完整性考虑

射频电路设计使用深N阱工艺,以消除衬底噪声;对于数字逻辑部分,由于其很大的噪声容限,对射频电路产生很大的干扰,因此需要进行对射频部分进行单独的隔离环(Guard-Ring)隔离。由于射频电路

对稳定性与噪声系数更加敏感,因此使用更加鲁帮可靠的偏置产生电路。

3. PLL-FS、PA-E电路的仿真、测试

3.1. PLL-FS、PA-E电路版图后仿真结果

利用Cadence的SpecterRF软件在不同工艺角(tt, ss, sf, ff, fs)下进行了版图后寄生参数提取与仿真;如表1所示,其左侧、右侧分别是设计的PLL-FS、PA-E电路的一些关键指标。

如表2所示,其是设计的射频电路系统的关键指标与其余文献中相关设计的对比 [7] - [9] 。

3.2. 射频芯片(PLL-FS、PA-E)的测试介绍

对射频发射芯片施加控制电压与稳定的电源电压,利用Agilent 86100A信号示波器(观察输出射频波

Figure 6. PA-E circuit’s architecture

图6. PA-E电路结构

Figure 7. Circuit layout photograph of radio PLL-FS and PA-E circuits

图7. 射频PLL-FS、PA-E版图缩微照

Table 1. Key parameters of PA-E and PLL-FS circuits

表1. PA-E、PLL-FS关键指标

Table 2. Key parameters comparison in this paper V.S. related papers’

表2. 该文的射频发射机与相关文献设计的性能对比

形)、Agilent E4440频谱分析仪(分析相位噪声、频谱纯度、杂散),通过芯片外管调试管脚对片内的PLL-PS的多频点输出进行了分析,符合预期设计要求;对芯片内部的PA-E电路模块也进行了测试,利用网络分析仪,测试得到了其S散射参数,也符合预期设计指标。

4. 结论

该文的4段流水的精简无线编码加速器EEG-DSP芯片,可以完成对整个脑电检测系统的控制,以及实现对无线信道的编码;直接上变频架构的射频芯片使用FSK/OOK调制在多个参数之间进行了权衡设计,射频电路参数在不同工艺角下的严格后仿真满足预期设计指标,实际芯片测试也满足设计要求。该文的无线射频芯片可以应用于可穿戴脑电传感节点数据的无线发射,以满足近距离通信的要求。

基金项目

国家自然科学基金(No. 61527815, No. 31500800, No. 61501426, No. 61471342),国家重点基础研究发展计划(2014CB744600),北京市科技计划(Z141100000214002),中科院重点部署项目(KJZD-EW-L11-2)资助项目。

文章引用

孙建辉,刘军涛,王蜜霞,徐声伟,蔡新霞. 脑电可穿戴无线射频发射芯片系统的研究

Research of Brain EEG Wireless Radio Transmitter IC System for Wearable Application[J]. 光电子, 2016, 06(02): 39-46. http://dx.doi.org/10.12677/OE.2016.62007

参考文献 (References)

- 1. 郭春生. 388例偏头痛临床与EEG分析[J]. 现代生理学杂志, 2007, 14(2): 75-77.

- 2. 李迎军, 崔清芳. 112例妇科内分泌紊乱的EEG与临床[J]. 临床老点血杂志, 1995, 4(2): 79-80.

- 3. ADS1299 Datasheet, TI CO. Low-Noise, 8-Channel, 24-Bit Analog Front-End for Biopotential Measurements.

- 4. 池保勇. CMOS射频集成电路分析与设计[M]. 北京: 清华大学出版社, 2006.

- 5. Chen, J.J., Liu, W.Y., Feng, P., Wang, H.Y. and Wu, N.J. A 2.4GHz Energy-Efficient 18-Mbps FSK Transmitter in 0.18um CMOS.

- 6. 张辉. 基于标准CMOS工艺的可重构锁相环关键技术研究[M]. 北京: 中国科学院电子学研究所, 2012.

- 7. Harison, R.R., et al. (2007) A Low-Power Integrated Circuits for Wireless 100-Electrode Neural Recording System. IEEE Journal of Solid-State Circuits, 42, 123-133.

- 8. Chi, B., Yao, J., Han, S., et al. (2007) Low Power Transceiver Analog Front End Circuits for Bidirectional High Data Rate Wireless Telemetry. IEEE Transactions on Biomedical Engineering, 54, 199.

- 9. Bonfanti, A., Ceravolo, M., Zambra, G., Gusmeroli, R., et al. (2010) A Multi-Channel Low-Power IC for Neural Spike Recording with Data Compression and Narrowband 400-MHz MC-FSK Wireless Transmission. IEEE European Solid- State Circuits Conference (ESSCIRC).