Software Engineering and Applications

Vol.

12

No.

02

(

2023

), Article ID:

63899

,

12

pages

10.12677/SEA.2023.122021

基于77 GHz逆合成孔径雷达的二维成像系统

徐杨1,吴佳伟2

1上海理工大学健康科学与工程学院,上海

2上海理工大学光电信息与计算机工程学院,上海

收稿日期:2023年2月28日;录用日期:2023年3月31日;发布日期:2023年4月14日

摘要

针对逆合成孔径雷达(ISAR)成像分辨率和成像速度要求较高的问题,设计了一个77 GHz ISAR二维成像系统。采用距离–多普勒(RD)算法进行成像,中控采集系统采用以FPGA为核心的ADC采集板卡,信号源采用19 GHz宽屏带射频源,收发模块采用倍频放大结构。上位机发送指令控制信号,中控采集板卡控制转台旋转以及射频源产生扫频信号,经发射天线倍频至77 GHz,然后接收天线将回波信号下变频至中频信号进入采集板卡,最后将采样数据传输至上位机中通过算法成像。测试结果表明,该系统实现了77 GHz雷达信号发生、系统时钟同步精度为78 ps、最大采样率为250 MSPS、最大传输速率为5 Gb/s,且单通道ADC采集的中频数字信号可以使二维成像满足理论分辨率,即6.9 cm × 4.0 cm;在实际工程中其信号带宽大、采样速率快、成像速度快和成像分辨率高等特性,满足了对物体进行二维成像的需求。

关键词

逆合成孔径雷达,距离多普勒,FPGA,高分辨率成像

Two-Dimensional Imaging System Based on 77 GHz Inverse Synthetic Aperture Radar

Yang Xu1, Jiawei Wu2

1School of Health Science and Engineering, University of Shanghai for Science and Technology, Shanghai

2School of Optical-Electrical and Computer Engineering, University of Shanghai for Science and Technology, Shanghai

Received: Feb. 28th, 2023; accepted: Mar. 31st, 2023; published: Apr. 14th, 2023

ABSTRACT

A 77 GHz ISAR two-dimensional imaging system was designed to address the problems of high imaging resolution and speed requirements in inverse synthetic aperture radar (ISAR). The imaging was performed using the range-doppler (RD) algorithm, while an ADC acquisition board with an FPGA core was employed in the central control acquisition system. A wideband RF source with a frequency of 19GHz and a transmit/receive module adopting a multiplier amplification structure were used. The central control acquisition board controlled the rotation of the turntable and generated a sweep signal via the RF source, in response to the instruction signal sent from a host computer. After being doubled to 77 GHz by a transmitting antenna, the echo signal was received by another antenna and down-converted into an intermediate frequency signal that entered the acquisition board. The sampled data was eventually transmitted to the host computer for reconstruction through algorithms. The testing results indicate that this system achieved 77 GHz radar signal generation, a clock synchronization accuracy of 78 ps, the highest sampling rate of 250 MSPS, the maximum transmission rate of 5 Gb/s, and that the intermediate frequency digital signals collected by a single channel ADC could satisfy the theoretical resolution, i.e. 6.9 cm × 4.0 cm, for two-dimensional imaging. This system had high signal bandwidth, fast sampling rate, high imaging speed, and resolution, which met the demand for two-dimensional object imaging in practical engineering.

Keywords:Inverse Synthetic Aperture Radar, Range Doppler, FPGA, High-Resolution Imaging

Copyright © 2023 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

1. 引言

逆合成孔径雷达(ISAR)能够提供对目标的详细信息,可以使用它来判断目标的位置、方向及其移动的速度。ISAR可以用于对飞机、舰船和空间目标进行图像成像,在军事和民用领域都具有重要的意义。ISAR成像系统通过增大发射信号带宽来提高成像分辨率,高带宽的回波信号对成像系统的采样、传输速率和成像算法提出了较高的要求 [1] [2] 。一方面,回波数据采样的准确性会直接影响成像结果,所以需要设计高速、高精度采集电路完成回波信号的采集 [3] 。另一方面,回波信号频率比较高,带宽比较大,对系统中的数据传输要求比较高,需要保证数据传输的实时性和准确性 [4] 。最后,在实际工程中由于ISAR回波数据量较多,成像系统对于雷达成像算法的计算效率和抗干扰能力要求较高 [5] [6] [7] [8] 。目前,王硕等人(2022)实现了基于FPGA的24 GHz FMCW雷达收发机系统,完成目标的信号采集和测距功能 [9] ,由于其信号采样速率过低,数据通过串口传输,无法完成回波信号的高精度采样和高速传输。程轼博(2020)和祝昇翔等(2022)提出了在雷达系统中存在计时时钟误差和由时钟引起的通道同步误差,Dario Russo和Stefano Ricci (2019)等人提出了信号在采样过程中存在同步误差,此类误差会影响回波数据采集,从而影响最终的成像结果,所以需要对采集系统的时钟进行同步 [10] [11] [12] 。胥秋(2016)实现了基于ZYNQ的ISAR成像系统,采用射频收发模块芯片,该芯片集成了AD/DA、滤波、放大、增益控制、频率合成器等模块 [13] ,但由于其工作频率在70 MHz~6 GHz,工作带宽在200 KHz~56 MHz,无法完成高分辨率的二维成像。

为了综合改善成像系统的高速采样、采样时钟同步和高分辨率成像等问题,本文设计的二维成像系统通过使用频综信号为19.25 G ± 500 MHz的射频源,经发射模块和天线倍频放大至77 GHz ± 2 GHz,天线和接收模块接收回波信号并且将其混频至中频,随后信号进入FPGA中控板卡完成时钟同步后,进行同步数据采集并传输至上位机,以距离多普勒(Distance Doppler, RD)算法成像,最后通过实际工程验证二维成像系统在方位向和距离向的分辨率是否符合预期理论分辨率。

2. RD成像算法

RD成像是一种用于回波测量的一维距离压缩成像算法。通过将回波信号分割为不同的振幅和频率区域,每个区域代表了目标物体在一段特定距离内反射回来的信号 [14] 。ISAR利用多普勒原理从反射信号中推断出目标物体的运动方向和速度。RD算法可以节省雷达映射遍历量,减少雷达成像时间。它可以准确地检测天线信号的起始位置和轨迹,减少了球形假相干现象。多普勒扩展可以显示延误干扰和信号丢失,并具有更好的干扰抵抗能力,ISAR转台模型如图1所示。

Figure 1. ISAR turntable model

图1. ISAR转台模型

ISAR系统的信号源发射带宽线性调频信号,接收机接收到回波后,对回波信号进行解线性调频(Dechirp)完成距离压缩的信号可表示为

(1)

对压缩后的信号做距离向快速傅里叶变换(Fast Fouirer Transform, FFT)可得目标点的纵向位置,可表示为

(2)

其中c为光速,λ为发射信号的波长,Tp为信号脉宽,γ为信号调频率,Rp(tm)为目标点与雷达天线之间的距离,fr为距离向的频率,sinc()为辛格函数。由式(1)中的后三个相位项分别代表多普勒频率生成项、剩余视频相位和包络斜置项。其中第一项在方位处理可生成多普勒频率,后两项会影响多普勒频率的测量,该部分需要设置补偿函数进行消除

(3)

将式(2)与补偿函数式(3)相乘,消除多余项,结果可表示为

(4)

由式(2)可知fr = 2γr/c以及信号调频率γ = B/Tp,带入式(4)得

(5)

其中ΔRp(tm)可拆分为平动分量ΔRT(tm)和转动分量ΔRR(tm),ΔRp(tm)可改写为ΔRT(tm) + ΔRR(tm)。平动分量可导致回波信号出现高阶多普勒项,大范围的包络偏移,对于回波的二维成像具有较大影响。RD算法采用平动补偿的方式,首先进行对包络进行对齐可以消除平动带来的许多虚假散射点的影响,使得同一散射点分散在多个不同的距离单元内的峰值重新聚集在同一个距离单元内。随后通过相位补偿校正平动分量ΔRT(tm)带来的相位偏移。平动补偿后的信号可表示为

(6)

目标点P与雷达天线的斜距可表示为

(7)

其中αp(tm)表示在tm时刻,目标点P与原点的距离OP与X正半轴的夹角; 表示在初始时刻,OP与X正半轴的夹角;R0表示原点O与雷达天线间的距离。可通过极坐标将式(7)改写为

(8)

利用麦克劳林级数展开式将sin(ωtm)和cos(ωtm)一阶展开,将高阶项忽略不计得:

(9)

初始时刻的转动分量表示为ΔRT(t0)≈yp(m),将式(9)代入式(6)得,

(10)

其中ΔRR(t0)为初始时刻得转动分量,约等于yp(m)。fm为方位向频率,对式(9)做方位向FFT,信号可表示为

(11)

其中方位向频率fm与距离ra的关系可表示为

(12)

将式(12)代入式(10)并去取幅值,得到ISAR图像表达式为

(13)

算法流程如图2所示:

Figure 2. SD algorithm flow chart

图2. SD算法流程图

3. 系统硬件设计

3.1. 整体设计

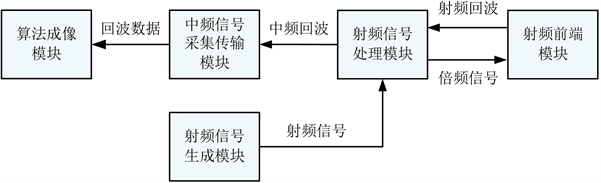

目前,ISAR二维成像系统现状研究的主要的硬件缺陷集中于:射频源发射信号带宽小,导致成像分辨率低和回波信号的高精度同步采样存在困难。综合考量上述问题,对ISAR二维成像系统进行功能设计,如图3所示,包括射频前端模块、射频信号处理模块、射频信号生成模块、中频信号采集模块和算法成像模块。

Figure 3. Functional block diagram of the ISAR imaging system

图3. ISAR成像系统功能框图

射频前端模块主要由天线实现倍频信号的功率放大、发射和接收。射频信号处理模块主要通过收发模块实现射频信号的倍频、差频和滤波。射频信号生成模块实现射频信号的载频、带宽、脉宽和参考基频的配置和生成,需要性能指标较好;具有良好的频率稳定度的雷达发射机。中频信号采集传输模块主要由ADC完成信号采样并将回波数据回传至上位机,算法成像模块在PC端对数据完成RD算法后成像。

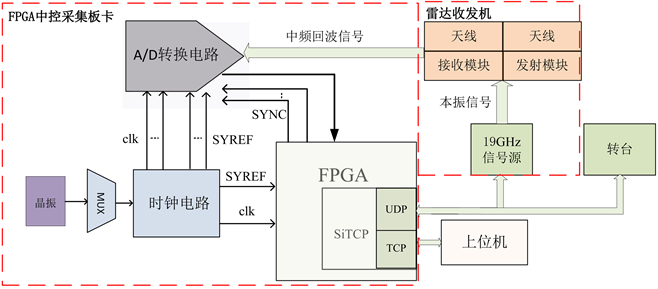

系统整体硬件电路设计由FPGA中控采集板卡、雷达发射机、回波接收模块、天线、转台和上位机组成。如图4所示。雷达发射机主要包括射频源和发射模块,由于雷达回波信号的带宽决定了成像分辨率,使用更高带宽的信号可以在更小的距离内显示出更多的细节,所以本系统雷达发射机采用19.25 GHz ± 500 MHz线性调频信号(Linear Frequency Modulated, LMF)发射机,输出功率较低,频率稳定度较高的大带宽射频信号,利用收发模块对信号进行逐级倍频放大至77 GHz ± 2 GHz,经发射天线放大后得到大功率的雷达信号。回波信号经接收天线进入接收模块,接收模块以倍频后的77 GHz ± 2 GHz信号作为本振,与回波信号经过差频电路后得到中频回波信号。

Figure 4. ISAR imaging system hardware circuit design

图4. ISAR成像系统硬件电路设计

中控采集板卡基于Xilinx公司Kintex7系列的7k325tffg900-2FPGA,该芯片内部具备丰富的逻辑资源以及足够大的吞吐量,能够可靠地完成模块应用开发。板卡电路整体包括ADC模块、时钟电路和数据传输模块。为了满足高速高精度采集的需求,采用ADI公司的AD9250芯片,它拥有最高250 MSPS采样速率,14 bit采样精度。此外,时钟电路使用TI公司LMK04610 PLL时钟芯片,它具有低抖动和高精度,并且可通过SPI协议进行内部配置,保证了系统稳定的工作时钟。数据传输模块使用TCP/IP协议,其接口是千兆电口SFP光模块,最大传输速率125 MB/s,实现了数据的高速传输。

系统的工作流程为:上位机向FPGA中控采集板卡发出指令,板卡解析该指令后,首先将射频配置指令发送到射频源,以控制发射射频信号;随后,将控制指令发送至转台,以控制转台旋转,同时雷达回波信号经接收模块处理后,中频信号输入板卡ADC通道进行采样,数据缓存在FPGA。最后通过TCP/IP协议发送至上位机保存后进行二维成像。

3.2. 雷达收发机

雷达发射机的射频源采用国产主振放大式发射机RC22-02-46,该信号源能够在很宽的频段内收发信号并且调制层次可调,从而能够产生正常信号强度,具有噪声抑制强,效率高,可产生连续不变的功率输出并且可实现脉冲压缩,适用于宽带频率捷变工作等特点。宽带调频驱动源产生19.25 G ± 500 MHz频综信号,具备多种扫频功能,实现输出多路频综信号和扫频信号。其中心频率为19.25 GHz,带宽分250 MHz、500 MHz、1 GHz三种可调,输出功率范围为3~5 dBm。根据成像系统所需要的指标,可通过UDP协议配置扫频模式,将工作模式选择为扫频模式,并将扫频中心频率设置为19.25 GHz。设置相应的扫频周期为50 us,带宽为250 MHz。驱动源检测触发信号为高时响应当前指令即可发射扫频信号。

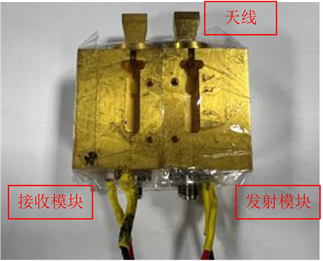

收发模块采用国产模块AMC-7292-14,发射模块射频信号输入带宽范围为18~23 GHz,输出信号增益为14 dBm,端口包括本振信号输入和射频信号输入。接收模块接收射频信号带宽范围72~92 GHz,端口包括本振信号输入、射频信号输入、中频信号输出。收发模块实物如图5所示。

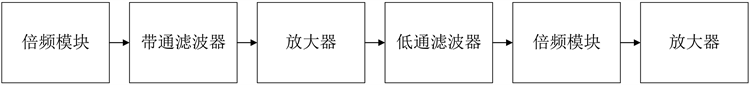

收发模块倍频放大的原理如图6所示,在收发模块中均采用零中频收发机结构,收发模块采用零中频接收机结构,其本振频率与射频信号频率相等。本振信号经过倍频模块将信号二倍频后,输入带通滤波器与前置放大器后,进入倍频模块将信号再次二倍频,随后通过低通滤波器与后置放大器后输出四倍频信号,将雷达信号倍频至77 GHz ± 2 GHz。其中带通滤波器有效地减少了近距离的目标回波幅度,防止调制信号泄露。同时,低通滤波器有助于保证当目标距离较远、信号弱时,使得有效信号得以保留,滤除混入系统中的高频干扰 [15] 。

接收模块是雷达信号采集中的关键部分,其性能会影响中频信号处理以及系统成像精度。当天线接收到射频信号,随后与本振信号混频、下变频到基带,再通过低通滤波器得到有效信号并放大后进行处理。但是零中频接收机很可能会受到由调制信号或高频噪声泄露信号导致的干扰。要有效地去除信号中的噪声干扰,并放大有效信号,接收模块必须使用有一定增益的滤波器 [16] 。

Figure 5. Physical picture of transceiver module

图5. 收发模块实物图

Figure 6. Frequency doubling method schematic diagram of transceiver module

图6. 收发模块倍频方法原理图

3.3. 时钟模块设计

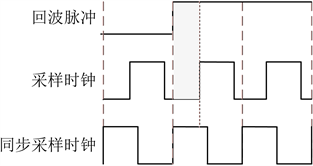

在ISAR二维成像系统中,由于硬件条件限制,信号源和采集板卡无法使用相同的时钟信号源,因此在采集雷达回波信号时会出现随机抖动。该抖动产生原因是:当以系统采样时钟频率fs对回波脉冲采样时,会产生随机分布在采样时钟周期T = 1/fs的不确定度 [17] ,如图7所示。采样时钟在下一个采样时钟上升沿时刻开始采样 [18] 。在这个过程中的随机误差对应于一个标准差的误差计算公式为:

(14)

Figure 7. Diagram of random synchronization error

图7. 随机抖动示意图

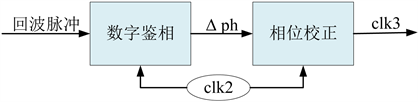

例如采样时钟为250 MHz,则会产生4 ns的不确定度,雷达回波信号的随机抖动的标准差σ ≈ 1.15 ns。该抖动会影响ISAR雷达接收天线通道的脉冲压缩位置,采集系统采集到的数据出现随机相位偏移,导致数据的每个采样点具有相同的相位移动。该误差使距离向回波信号发生变形展宽,从而影响ISAR二维成像分辨率。时钟同步模块的设计主要包括两个主要部分,数字鉴相模块和相位校正模块,如图8所示。其中clk2为中控板卡晶振生成的时钟,与输入进入采集系统的回波信号不相关。数字鉴相模块完成回波脉冲与采样时钟clk2之间的相位差Δph的测量。相位校正模块根据相位差对采样时钟进行补偿,补偿完成后生成时钟副本clk3并且输入PLL时钟芯片。时钟芯片扇出多路至各个模块,之后采集系统整体工作时钟与信号源时钟同相位,实现了采集时钟与信号源时钟的同步。

Figure 8. Clock synchronization module logic design block diagram

图8. 时钟同步模块逻辑设计框图

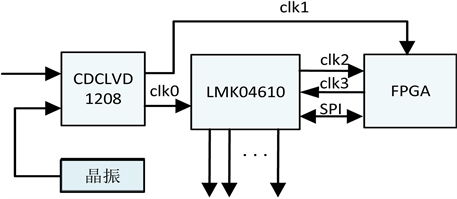

时钟电路整体设计思路如图9所示,晶振时钟进入CDCLVD扇出时钟芯片,扇出clk0、clk1两路时钟。其中clk0时钟信号输入到PLL时钟芯片中,作为该芯片的输入参考时钟,clk1时钟信号输入至FPGA,通过Xilinx提供的混合模式时钟管理器(MMCM)产生用于PLL时钟芯片寄存器的配置时钟。通过SPI协议配置PLL时钟芯片的寄存器后输出clk2,作为时钟同步前的采集时钟。在接收到回波脉冲后,FPGA内的随机同步误差校正模块根据回波脉冲与clk2的相位差对clk2进行相位补偿得到clk3,PLL时钟芯片将clk3扇出至ADC芯片作为新的采样时钟,实现信号源与采集系统的时钟同步。

Figure 9. Clock circuit design block diagram

图9. 时钟电路设计框图

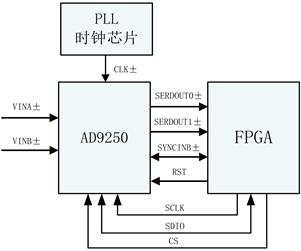

3.4. 数据采集模块设计

数据采集模块由FPGA、ADC、时钟电路电路实现,分别完成采集模块的控制、高速采样和时钟配置。采集模块运行流程如下:首先,FPGA通过UDP控制信号源输出脉冲,该脉冲将作为雷达采集系统的同步信号,接收天线接收到回波脉冲后,进入FPGA内对采集时钟进行随机误差校正,使得采集时钟与射频源时钟同步。随后上位机发送指令,控制信号源发射雷达扫频信号。ADC芯片对雷达回波信号高速采样,并通过高速串行传输协议JESD204B将采样数据传输至FPGA缓存。最后数据通过以太网协议将数据传输至上位机。片上数据传输接口为高速串行通信协议JESD204B,通过8b/10b编码格式进行数据传输,则最大串行链路速率为:

(15)

FPGA可通过AMDXilinx公司的吉比特收发器(Gigabit Transceiver, GTX)完成点对点的串行数据传输,其中采用了CML、CDR、线路编码和预加重使得接收串行数据率可达12.5 Gbps [19] [20] ,所以可满足JESD204B高速串行协议的需求,实现了FPGA与AD9250的高速通信。采样电路工作流程如图10所示,系统上电后,FPGA通过RST引脚对ADC芯片复位,然后通过SPI协议完成对AD9250片内寄存器的配置。由于AD9250支持可选的各种输入范围,所以PLL时钟芯片分配的采样时钟频率决定ADC芯片的采样率。最后AD9250将模拟差分的雷达回波信号数字化后,通过高速串行数据接口将采集信号通过JESD204B接口SERDOUT0±,SERDOUT1±差分输出线进入FPGA缓存 [21] 。

Figure 10. Schematic diagram of pin connection of high-speed sampling circuit

图10. 高速采样电路引脚连接示意图

3.5. 数据传输电路设计

数据传输电路采用以太网接口通信,实现了上位机与中控采集板卡的数据传输和指令交互。设计中为了简化系统电路设计,采用KEK日本高能加速器研发中心提供的以太网协议栈SiTCP [22] 。该模块包含了TCP和UDP模块,实现了MAC层协议通信,所以可直接实现与以太网PHY部分连接,简化了以太网通信的开发过程。

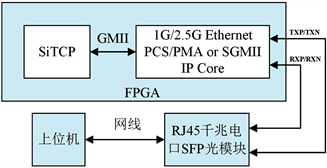

千兆以太网的电路结构由SiTCP协议栈和1G/2.5G Ethernet PCS/PMA or SGMII IP核物理层实现 [23] ,如图11所示。此IP核是利用FPGA中内置的高速串行收发器来实现以太网PHY部分,并把串行数字的接收结果转换成8 bit并行数据,之后与SiTCP核的GMII接口相连。中控采集板卡上采用是千兆电口SFP光模块,接口规格为RJ45。

Figure 11. Block diagram of Gigabit Ethernet communication circuit

图11. 千兆以太网通信电路实现框图

4. 系统测试

为了完整测试成像系统性能,测试可分为三个部分包括高速采样电路测试、时钟同步性能测试和二维成像测试。时钟同步性能测试思路如下:首先信号发生器用来模拟雷达回波脉冲信号,随机设置脉冲波频率。一路输出至示波器作为触发Trigger信号,另一路输出至FPGA中控采集板卡。然后FPGA分别输出采样时钟同步前后的脉冲信号至示波器,反映时钟同步模块的同步效果,在示波器的余辉模式下可得出在时钟同步前时钟信号相对于脉冲回波存在一个时钟周期的随机抖动,约4000 ps,如图12(a)所示。时钟同步后的随机抖动得到了明显的抑制,如图12(b)所示。测得采样时钟与回波脉冲的同步精度为78 ps rms。

Figure 12. Renderings of clock synchronization

图12. 时钟同步效果图

高速采样测试使用的信号发生器为NF公司的WF1968,高速采样电路测试了ADC的最大采样速率,使用信号发生器模拟固定频率的零中频信号验证ADC芯片采样速率,分析采样数据的时域和频域波形。测试结果表明,采样得到的数字信号连续完整,信号频率与预先设定的模拟信号频率相同,如图13所示。表明信号采样数据正确可靠。

Figure 13. Sample rate test results

图13. 采样率测试结果

将采样模块应用于ISAR二维成像系统,设置目标场景为单点和三点目标,中控系统配置转台旋转角度及速度,配置信号源的扫频周期为50 us、载频信号为77 GHz,带宽2 GHz,脉冲重复频率为1000 Hz,并且通过触发控制射频信号发生和扫频持续时间。根据射频源扫频脉宽,为了保证信号采集的完整性,设置单次ADC采样点数为5500个,共采样100组。采样传输模块完成对雷达回波信号的采样和数据传输。单点和三点采样目标频谱如图14所示,其中在三点目标频谱中,设置两点与雷达方向距离相同,所以只有两个频率值。三点目标成像结果如图15所示,其距离向×方位向分辨率为6.9 cm × 4.0 cm,满足二维成像实验的理论预期,表明该77 GHz ISAR成像系统满足实际工程需求。

Figure 14. Target sampling result plot

图14. 采样目标频谱图

Figure 15. Imaging renderings

图15. 成像效果图

5. 结论

本文设计了77 GHz ISAR雷达信号二维成像系统。主要介绍了RD成像算法的实现过程,雷达发射机及接收模块的工作原理和FPGA采集电路、时钟电路数据传输的电路设计,然后搭建实验测试平台,完成对时钟同步精度以及中频信号的采样性能的测试,最后对整体系统进行二维成像实验,实验结果表明,该ISAR二维成像系统具有信号带宽大、采样速率高、采集时钟同步精度高、传输速率快、成像速度快和成像分辨率高等特点。二维成像的分辨率和成像效果验证了该系统的正确性和可靠性。

文章引用

徐 杨,吴佳伟. 基于77 GHz逆合成孔径雷达的二维成像系统

Two-Dimensional Imaging System Based on 77 GHz Inverse Synthetic Aperture Radar[J]. 软件工程与应用, 2023, 12(02): 209-220. https://doi.org/10.12677/SEA.2023.122021

参考文献

- 1. 金胜, 朱天林. ISAR高分辨率成像方法综述[J]. 雷达科学与技术, 2016, 14(3): 251-260+266.

- 2. 周鹏, 郑佳辉, 张振华, 等. 逆合成孔径雷达三维成像综述[J]. 电波科学学报, 2023, 5(2): 1-16.

- 3. 张锐, 关炀. 数字相控阵雷达同步技术研究与实现[J]. 现代导航, 2021, 12(5): 358-362.

- 4. 林任烦, 赵福海, 吴侠义, 尹铭浩. FPGA的超高速数字采集系统设计与实现[J]. 单片机与嵌入式系统应用, 2022, 22(7): 66-70.

- 5. Li, C., Zhang, H., Deng, Y., et al. (2019) Focusing the L-Band Spaceborne Bistatic SAR Mission Data Using a Modified RD Algorithm. IEEE Transactions on Geoscience and Remote Sensing, 58, 294- 306. https://doi.org/10.1109/TGRS.2019.2936255

- 6. An, H., Wu, J., Sun, Z., et al. (2019) A Two-Step Nonlinear Chirp Scaling Method for Multichannel GEO Spaceborneairborne Bistatic Sar Spectrum Reconstructing and Focusing. IEEE Transactions on Geoscience and Remote Sensing, 57, 3713-3728. https://doi.org/10.1109/TGRS.2018.2886817

- 7. Wu, J., Pu, W., Huang, Y., et al. (2018) Bistatic Forward-Looking SAR Focusing Using ωk Based on Spectrum Modeling and Optimization. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 11, 4500-4512.

- 8. 何耀民, 何华锋, 徐永壮, 等. 基于改进wk算法的弹载SAR斜视成像[J]. 系统工程与电子技术, 2020, 42(2): 331-338.

- 9. 王硕, 张景璐, 岳增龙. 基于FPGA的FMCW雷达收发机系统[J]. 现代制造技术与装备, 2022, 58(4): 162-164.

- 10. 程轼博. 星载毫米波合成孔径雷达干涉测量误差分析[D]: [硕士学位论文]. 合肥: 合肥工业大学, 2020.

- 11. 祝昇翔, 何岷, 贺志毅, 等. 一种相控阵雷达多通道同步方法[J]. 现代防御技术, 2022, 50(1): 60-66.

- 12. Russo, D. and Ricci, S. (2020) FPGA Implementation of a Synchronization Circuit for Arbitrary Trigger Sequences. IEEE Transactions on Instrumentation and Measurement, 69, 5251-5259. https://doi.org/10.1109/TIM.2019.2952478

- 13. 胥秋. 基于ZYNQ的ISAR系统设计与实现[D]: [硕士学位论文]. 成都: 西南交通大学, 2016.

- 14. 吕金华, 唐扶光, 赵煦, 吴浩然. 一种小斜视多接收阵合成孔径声呐距离多普勒成像算法[J]. 舰船科学技术, 2019, 41(13): 124-129.

- 15. 何超, 徐洪. 船用导航雷达收发机测试系统的研究与设计[J]. 电子测量与仪器学报, 2009, 23(S1): 112-115.

- 16. 冯凯, 石春琦, 张旭, 等. 一种应用于24 GHz毫米波雷达系统的低功耗中频信号处理电路[J]. 固体电子学研究与进展, 2022, 42(5): 363-370. https://doi.org/10.19623/j.cnki.rpsse.2022.05.009

- 17. Kalashnikov, A.N., Challis, R.E., Unwin, M.E., et al. (2005) Effects of Frame Jitter in Data Acquisition Systems. IEEE Transactions on Instrumentation & Measurement, 54, 2177-2183. https://doi.org/10.1109/TIM.2005.858570

- 18. Kalashnikov, A.N. (2009) Waveform Measurement Using Synchronous Digital Averaging: Design Principles of Accurate Instruments. Measurement, 42, 18-27. https://doi.org/10.1016/j.measurement.2008.03.010

- 19. 邵杰, 万书芹, 叶明远, 盛炜. 基于JESD204B协议的发送端电路设计[J]. 电子器件, 2021, 44(2): 300-305.

- 20. 李武建, 吴兵, 彭卫. 基于AD9680的高速数据接口设计[J]. 山东工业技术, 2016(17): 109.

- 21. 孔玉礼, 陈婷婷, 万书芹, 等. 基于JESD204B协议的接收端电路设计[J]. 电子与封装, 2022, 22(12): 77-83.

- 22. Uchida, T. (2008) Hardware-Based TCP Processor for Gigabit Ethernet. IEEE Transactions on Nuclear Science, 55, 1631-1637. https://doi.org/10.1109/TNS.2008.920264

- 23. 王淑文, 沈仲弢, 王硕, 等. PandaX-nT暗物质探测实验读出电子学预研系统的研制[J]. 原子能科学技术, 2020, 54(6): 1018-1026.