Computer Science and Application

Vol.05 No.04(2015), Article ID:15249,7

pages

10.12677/CSA.2015.54016

Research on Mixed Encryption of DES and LFSR and FPGA Implementation

Yu Gang1,2, Yongjun Wen1,2*, Min Deng1,2, Weixuan Xia1,2, Feng Bin1,2, Wenpin Liao1,2, Lijun Tang1,2*

1Hunan Province Higher Education Key Laboratory of Modeling and Monitoring on the Near-Earth Electromagnetic Environments (Changsha University of Science & Technology), Changsha Hunan

2Department of Physics and Electronic Science, Changsha University of Science and Technology, Changsha Hunan

*通讯作者。

Email: *doudou.wen@163.com, *tanglj2000@263.net

Received: Apr. 28th, 2015; accepted: May 14th, 2015; published: May 20th, 2015

Copyright © 2015 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

ABSTRACT

With the growing of network information, the issue of information security has become the bottleneck of the development of network source application. This paper aimed at file’s security in the computer and Internet, and researched on DES encryption algorithm and the algorithm of LFSR. Based on above algorithms, we designed a mixed encrypted method realized by FPGA; according to the password combination that is inputted by the user, a bunch of keys will be produced by LFSR and sent to computer by USB. The function of software on the computer is communicating with USB chip and encrypting files with DES algorithm. The results showed that this scheme has good effect and high processing speed on encrypting any certain files, and has a good effect for protecting files on network space.

Keywords:DES Encryption Algorithm, LFSR, FPGA, Encrypting Files

DES和LFSR混合加密的研究与FPGA实现

刚 煜1,2,文勇军1,2*,邓敏1,2,夏伟轩1,2,宾 峰1,2,廖文平1,2,唐立军1,2*

1近地空间电磁环境监测与建模湖南省普通高校重点实验室(长沙理工大学),湖南 长沙

2长沙理工大学物理与电子科学学院,湖南 长沙

Email: *doudou.wen@163.com, *tanglj2000@263.net

收稿日期:2015年4月28日;录用日期:2015年5月14日;发布日期:2015年5月20日

摘 要

随着网络信息交流量日益增长,信息安全问题成了网络资源应用的发展瓶颈。本文针对计算机与网络上文件的安全性问题,对DES算法以及LFSR密码生成算法进行研究,设计了基于DES和线性反馈移位寄存器(LFSR)的混合加密算法并通过FPGA实现,FPGA根据用户输入的密码组合,通过线性反馈移位寄存器产生一串密钥,然后通过USB将这串密钥发送至计算机中。上位机软件实现与下位机的USB通讯、用DES算法对任意文件进行加密和解密的功能。结果表明,该方案对任意文件加密效果好、速度较快,对于网络空间文件保护有较好的效果。

关键词 :DES加密算法,LFSR,FPGA,文件加密

1. 引言

随着21世纪网络信息时代的到来,网络空间上的文件保护问题成为了人们应用网络空间的心病。如何保护文件里的信息不被泄漏、保证文件的保密性和安全性是各行各业都很重视的课题,无论是政府、企业还是个人都逐渐依赖计算机存储信息,并借助网络传递、交换重要资料和洽谈贸易。这些信息无论是私人信息还是部门信息,无论是军用信息还是商业信息,在进行处理和传递前要以电子文档的形式存储在单机、服务器或网络上任意一台客户机上,因此电子文档的安全存储成为实现信息安全的首要条件[1] 。

针对网络信息安全性问题,CESVMC (Computable Encryption Scheme based on Vector and Matrix Calculations)加密方案,提升了数据存储、运算过程中的安全性,但运算时间比较长,存储和通信的负载较大 [2] 。通过软件运算进行加密与使用硬件进行加密相比,软件加密更容易破解。本文利用软件硬件各自的优势,取长补短,将FPGA用于加密算法设计,探索一个以FPGA为核心加密方案。

2. DES和LFSR混合加密

2.1. DES算法介绍

数据加密标准(Data Encryption Standard, DES)是由IMB公司研究发表,美国国家标准与技术研究院于1977年标准化的,目前最广泛应用的用于加密机密信息的加密方法 [3] - [5] 。

DES算法的加密由四部分完成,分别为:初始置换函数IP、子密钥Ki、密码函数F、末置换函数IP-1 [6] [7] 。DES算法需要用户提供一共64位长度的密钥用于加密与解密。算法可以提供高质量的数据保护,具有相当高的复杂性,实行经济而且运行效率高 [8] 。

DES算法只用到了64位密钥中的其中56位,还有8位并未参与DES运算,随着计算机的发展计算机运行速度越来越快,使得使用暴力破解法破解DES密钥的时间越来越短。为了保证使用DES算法的安全性,一般需要采用多重DES算法和AES加密算法,加长密钥的长度,增强DES安全性。

2.2. 线性反馈移位寄存器(LFSR)

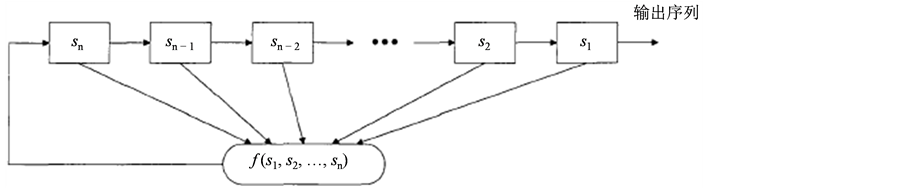

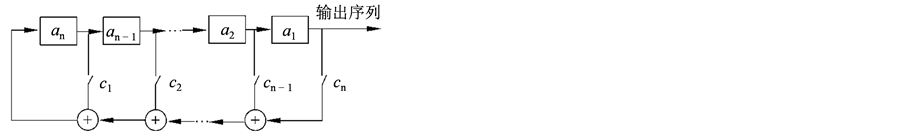

一个n级反馈移位寄存器如图1所示,其中 称为反馈函数,当

称为反馈函数,当 为一线性函数时,则称上图的反馈移位寄存器为线性反馈移位寄存器(Linear Feedback Shift Register, LFSR) [9] 。线性反馈移位寄存器具有非常适合硬件实现、能产生大的周期序列、能产生好的统计特性的序列、易于使用代数方法进行结构分析的特点 [10] - [12] 。

为一线性函数时,则称上图的反馈移位寄存器为线性反馈移位寄存器(Linear Feedback Shift Register, LFSR) [9] 。线性反馈移位寄存器具有非常适合硬件实现、能产生大的周期序列、能产生好的统计特性的序列、易于使用代数方法进行结构分析的特点 [10] - [12] 。

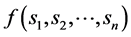

可设n级线性反馈移位寄存器的反馈函数:

(1)

(1)

其中 为0或者1,一般Cn都为1。

为0或者1,一般Cn都为1。

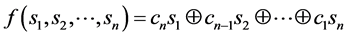

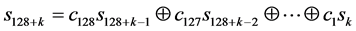

由于反馈函数是作为最后一级的输入,又根据移位寄存器的特点,反馈的结果会在n个时刻之后输出,于是可以推导出输出序列{si}:

(2)

(2)

可以看出Sn+k与过去最近的n个时刻的输出Si都有关系。

本设计的密钥生成模块采用带有适当的反馈函数的LFSR结构,使输出的56位密钥与128位的初始密钥都相关。当LFSR需要用作流密码器设计时,一般要求LFSR可以产生最大周期的密钥流,而当n级LFSR的反馈函数是本原多项式时,LFSR输出的可以达到最大周期2n - 1。这里LFSR的作用是令128位长度的初始密钥的每一位都至少与输出的56位长度的密钥中的一位相关。因此,可以根据需求设计LFSR的结构,而不必将其反馈函数设计成本原多项式。

本设计用户输入的原始密钥长度是128位,因此,需采用128级的LFSR结构。为了简化设计,可以令输出的56位密钥是连续输出的。基于这几个条件要求,式(2)中,n = 128, ,

, ,则式(2)可以改写成:

,则式(2)可以改写成:

(3)

(3)

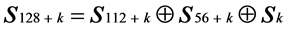

如果每一个环节都接一个反馈的话,程序的工作量会比较大,因此可以进行以下简化,由于k是连续递增变化的,可令反馈函数f在每连续56个环节之内至少有一个反馈环节,取c1,c57,c113,c128的值为1,其它ci值为0,因此,根据式(1)、式(2)以及式(3),本设计的LFSR的输出可以表示为:

(4)

(4)

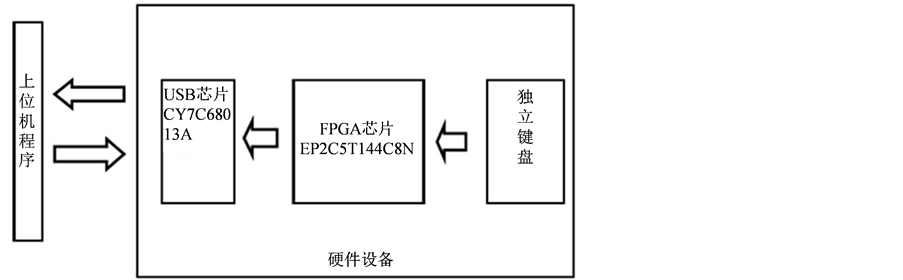

根据式(4),可以得出LFSR结构如图2所示。若输出的56位密钥在LFSR输出第128位之后,就可保证初始密钥每一位都与输出密钥相关。该方法的优点是产生密钥速度快,但直接加密会带来传输速度慢等问题。

2.3. DES算法与LFSR的混合加密方法

综合上述的方法,采取LFSR方法生成密钥,将LFSR与DES相结合进行加密的方案,即可提高速度,又可增加安全性。具体实现方法如下。

在硬件上,FPGA根据键盘输入的密码通过LFSR产生密钥之后,通过USB芯片传送给加/解密程序。软件上,加/解密程序将接受的密钥全部接受后再次通过DES算法产生子密钥,读取计算机上的文件然后进行加/解密,操作全部完成后删除原文件,从而完成对计算机上文件的加/解密,达到对计算机上文件的保护目的。

该方法允许用户输入密码组合长度最高可以达到16位,可能的密码组合的个数超过1016个。但是如果输入的密码长度是16位,由上面的描述可知,每一位密码都代表一个8位的KeyValue,16位的密

Figure 1. Linear feedback shift register

图1. 线性反馈移位寄存器

Figure 2. Framework of linear feedback shift register

图2. 线性反馈移位寄存器的结构

码长度代表整个密钥长度为128位,当攻击者不知道每一个键值所代表的KeyValue时,可能的组合就有2128 − 1个,因此,可以保证足够的安全性。

但128位长度超出了DES所需要的密钥长度,即用户输入的密码会有一部分无效。因此必须设计一种密钥生成方案,使输入的128位密钥中每一位至少与输出的56位长的密钥每一位相关的,这种方案可通过FPGA实现,但必须考虑尽量低的硬件复杂度,图3为加密系统结构框图。

3. FPGA实现方法

FPGA加密器由上位机程序以及硬件装置构成,硬件装置由FPGA最小系统电路、USB芯片工作电路、按键电路构成,相关电路设计方案如下。

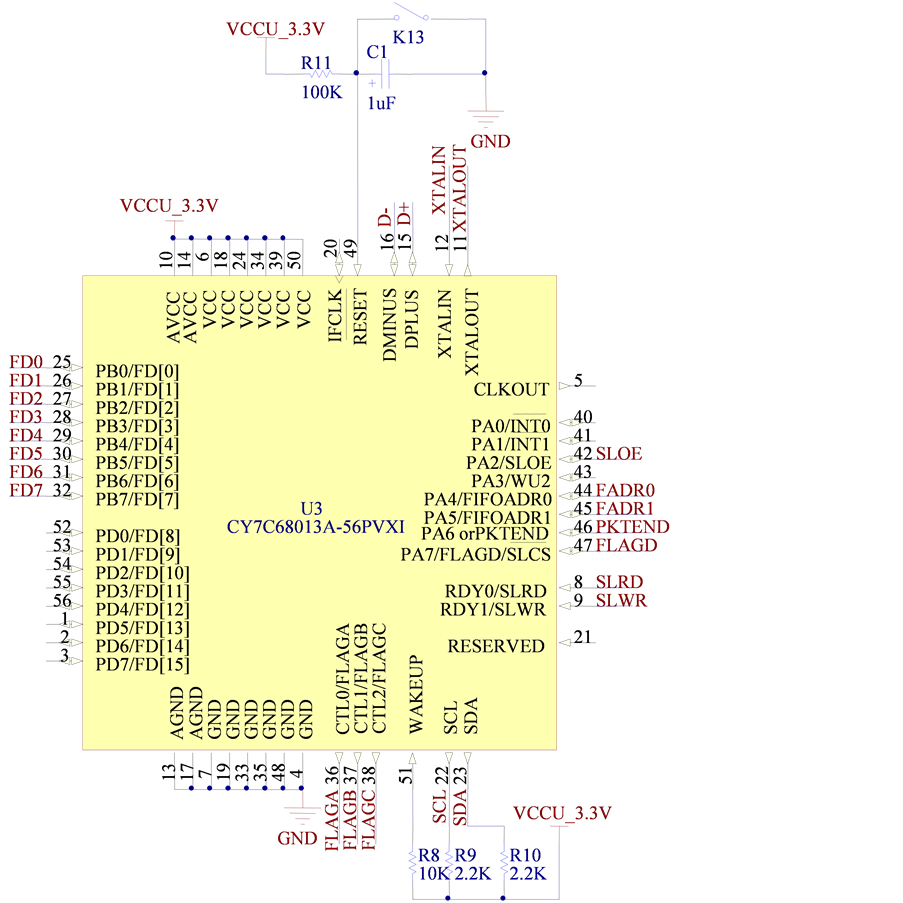

3.1. USB芯片CY

USB芯片CY

时钟信号是芯片正常工作的必要条件,24 MHz晶振电路为CY7C68013A芯片提供外部参考时钟信号。Mini USB接口通过D−和D+两个网络与CY7C68013A芯片相连接。通过这个Mini USB接口,用户可以用数据线将硬件装置与计算机连接起来。USB数据通过差分线路D−和D+在硬件装置和计算机之间传递。需要从计算机读取数据时,D−和D+的数据进入USB芯片后芯片会自行对数据进行解码,将解码后的数据存进FIFO缓冲区,供FPGA读出。当FPGA需要向计算机发送数据时,通过FD[0..7]向芯片发送数据,然后芯片会自动将接收到的数据编码,然后将编码后的数据通过D−和D+发送至计算机中。Mini USB接口的作用还有通过USB上的5 V供电为整个硬件装置提供电能。EEPROM电路用于储存每次复位或者上电后USB芯片读取的固件程序。

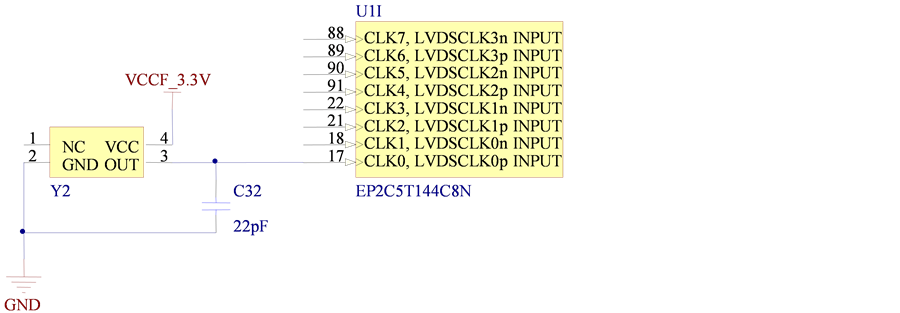

3.2. FPGA电路设计

本文采用的FPGA芯片是Altera公司Cyclone II系列的EP2C5T144C8N芯片,其电路由FPGA供电电路、JTAG电路、FPGA配置电路、FPGA外部时钟电路组成,其原理图如图5所示。

FPGA供电电路使用3.3 V电源为各个电源引脚提供电压,1.2 V电源为FPGA内部的逻辑元件提供

Figure 3. The overall design of encryption device

图3. 加密器系统结构框图

Figure 4. The schematic of CY

图4. CY7C68013电路原理图

Figure 5. The schematic of FPGA circuit

图5. FPGA电路原理图

电能。本设计使用的JTAG接口为10针JTAG接口,JTAG电路使已经被综合好的FPGA逻辑下载至FPGA上进行在线调试工作。在FPGA配置电路中,本文使用EPCS4SI8N作为FPGA的配置芯片,每次复位或者掉电之后,FPGA内储存配置信息的RAM里的数据便会丢失,所以需要配置芯片电路用于储存配置FPGA的配置信息,通过JTAG接口将由sof文件转化而来的JIC (JTAG Indirect Configuration)文件下载到配置芯片中,通过这种模式下载可以简化电路的整体设计。外部时钟源是一片50 MHz的有源晶振,FPGA时钟电路为FPGA提供参考时钟信号,以确保状态机、密钥生成、按键输入去抖等功能顺利实现。

3.3. FPGA逻辑设计

整个FPGA逻辑设计主要分3部分设计:控制模块设计、密码输入模块设计以及密钥生成模块设计。本文使用Verilog HDL作为硬件描述语言来进行FPGA编程。其工作流程图如图6所示。

控制模块用于执行上电后软件全局复位、接收从PC机上发来的指令(0x01)、根据指令做出相应的响应三个操作。软件全局复位是为了确保FPGA逻辑中所有模块都可以同时复位,不会产生不确定的结果。其操作是通过对50 MHz主时钟的脉冲进行计数,当计数值小于设定值时复位信号保持低电平,让全局保持复位状态;当计数值等于设定值时,复位信号拉高,所有模块进入工作状态。当FPGA收到的来自计算机的指令后,控制模块会先把密码输入模块打开,等待用户输入密码。当用户输入密码完毕后,控制模块会禁止密码输入功能,然后打开密钥生成模块。密钥发生模块会自动将生成的密钥发送到计算机中。

密码输入模块用于执行接收输入密码、将不同的键值编码成不同的编码值和按下确定键后将整个密钥送到PR (密钥生成模块)中三个操作。人按下按键的时候,按键可能会处在反复在按下和松开两个状态中来回切换的状态,密码输入模块先进行消抖操作,然后将接收到的按键进行编码操作,当密码全部输入完成后根据按下的是发送键还是清除键对密码进行发送或者清空处理。

密钥生成模块的作用是把按键输入模块输出的数据接收,根据此数据通过线性反馈移位寄存器产生伪随机数列,再将数据送往USB芯片的缓存区中。

4. 验证及测试

把FPGA加密设备连接至计算机之后,计算机的上位机能识别加密器的USB设备并读取相关的VID,PID。等待计算机使用者选择需要加密的文件之后,由使用者在独立键盘上输入密码,按下确认键之后FPGA将会把密钥通过USB芯片发至计算机中,计算机则开始进行加密操作,加密完成后计算机自动删除源文件并显示整个加密所消耗的时间,保留加密之后的文件,对于不同大小的文件其验证结果如表1所示。从表1可以看出,本加密器能够稳定的加密并还原计算机文件,加密和解密速度近1 M/s。

Figure 6. The working flow chart of FPGA

图6. FPGA的工作流程图

Table 1. The data of encryption rate

表1. 加密速度测试数据

5. 结论

本文提出了一种基于线性反馈移位寄存器的加密计算机文件的方案,从理论上证明了这种方案的可行性并且通过FPGA实现。该方案结合了软件和硬件加密优势,具有很高的安全性,可应用于网络文件存储和传输,有一定的应用价值。

基金项目

国家科技支撑计划项目(2014BAH28F04),湖南省重点学科,湖南省高校科技创新团队,湖南省教育厅科学研究项目(14C0031),湖南省教学改革研究项目(湘教通[2013]223号)。

文章引用

刚 煜,文勇军,邓 敏,夏伟轩,宾 峰,廖文平,唐立军, (2015) DES和LFSR混合加密的研究与FPGA实现

Research on Mixed Encryption of DES and LFSR and FPGA Implementation. 计算机科学与应用,04,125-132. doi: 10.12677/CSA.2015.54016

参考文献 (References)

- 1. 胡祥义, 徐冠宁, 杜丽萍 (2013) 基于云计算的文件加密传输方法. 网络安全技术与应用, 5, 18-22.

- 2. 黄汝维, 桂小林, 余思, 庄威 (2011) 云环境中支持隐私保护的可计算加密方法. 计算机学报, 12, 2391-2402.

- 3. 黄光明 (2013) 基于DES_RSA加密算法的改进与实现. 硕士论文, 东北师范大学, 沈阳.

- 4. 邱世中 (2013) 基于FPGA的DES混沌加密算法实现与改进. 硕士论文, 广东工业大学, 广州.

- 5. 吴明航 (2013) DES和RSA混合加密算法的研究. 硕士论文, 哈尔滨工业大学, 哈尔滨.

- 6. Hu, M.Y. (2014) Analysis and improvement of the security of DES algorithm. WIT Transactions on Information and Communication Technologies, 57, 317-324.

- 7. Alani, M.M. (2012) Neuro-cryptanalysis of des and triple-DES. Lecture Notes in Computer Science, 7667, 637-646.

- 8. 丁显信 (2013) DES算法的硬件实现方法研究及FPGA实现. 硕士论文, 青岛科技大学, 青岛.

- 9. 李鹏, 颜学龙, 孙元 (2014) 基于多配置LFSR的测试生成结构设计. 计算机工程与科学, 5, 814-820.

- 10. 朱楠 (2010 基于FPGA的流密码机设计. 硕士论文, 西安电子科技大学, 西安.

- 11. 肖旭韬, 张雪锋 (2013) 基于线性反馈移位寄存器和组合猫映射的伪随机序列生成方法. 计算机应用研究, 1, 161-164.

- 12. 潘晓英 (2015) 基于线性反馈移位寄存器和分组密码的伪随机数生成方法. 通信技术, 2, 228-231.