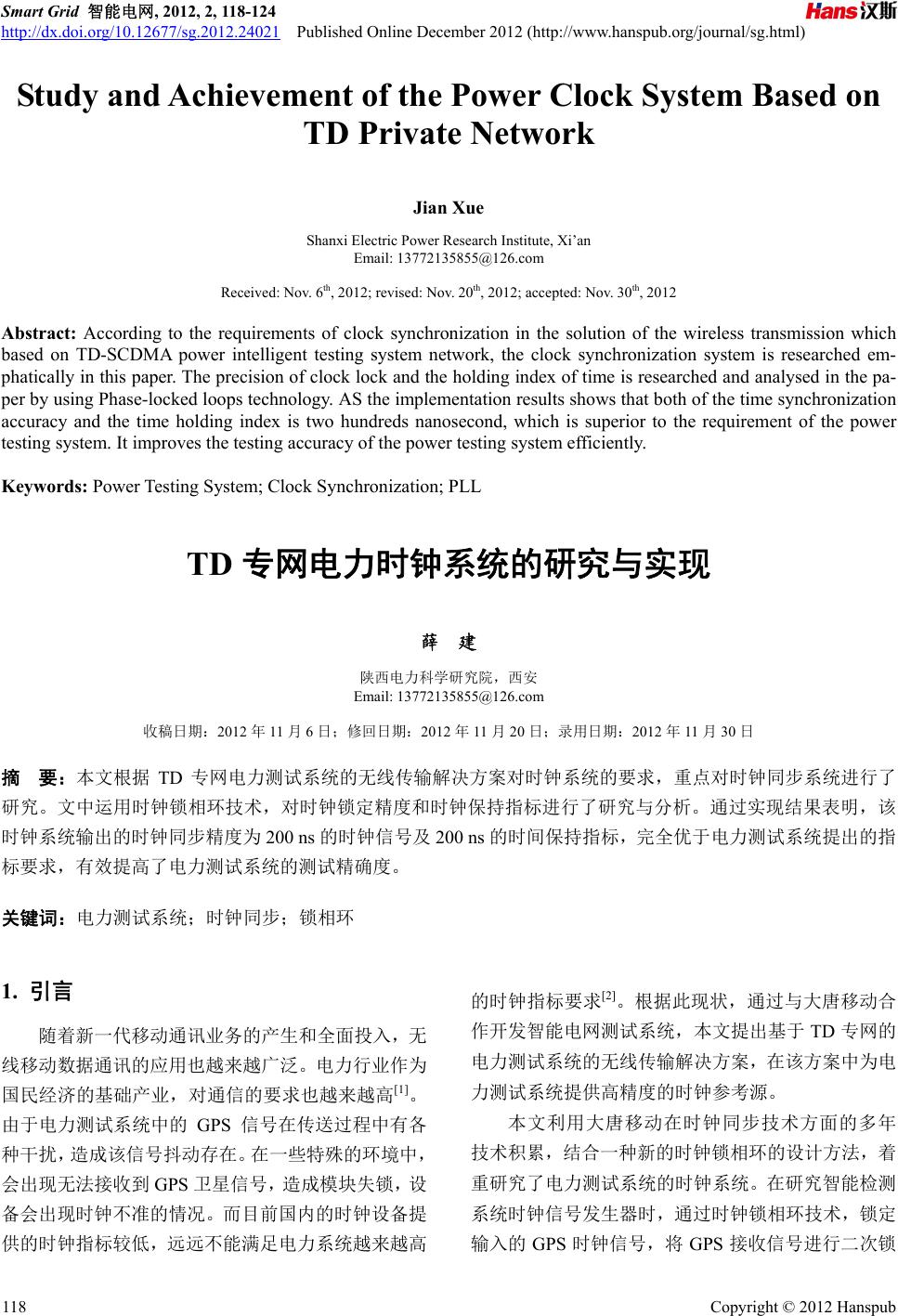

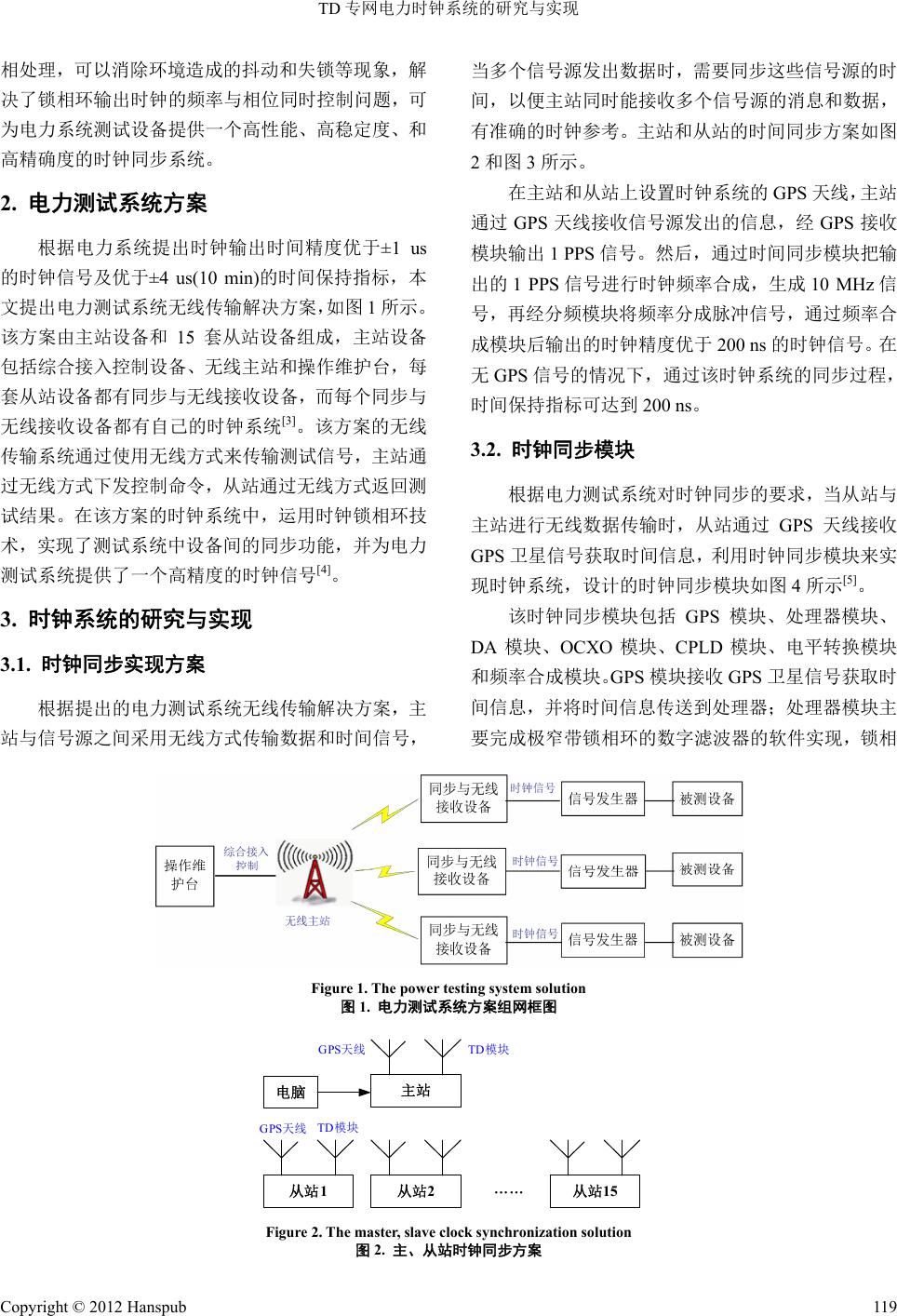

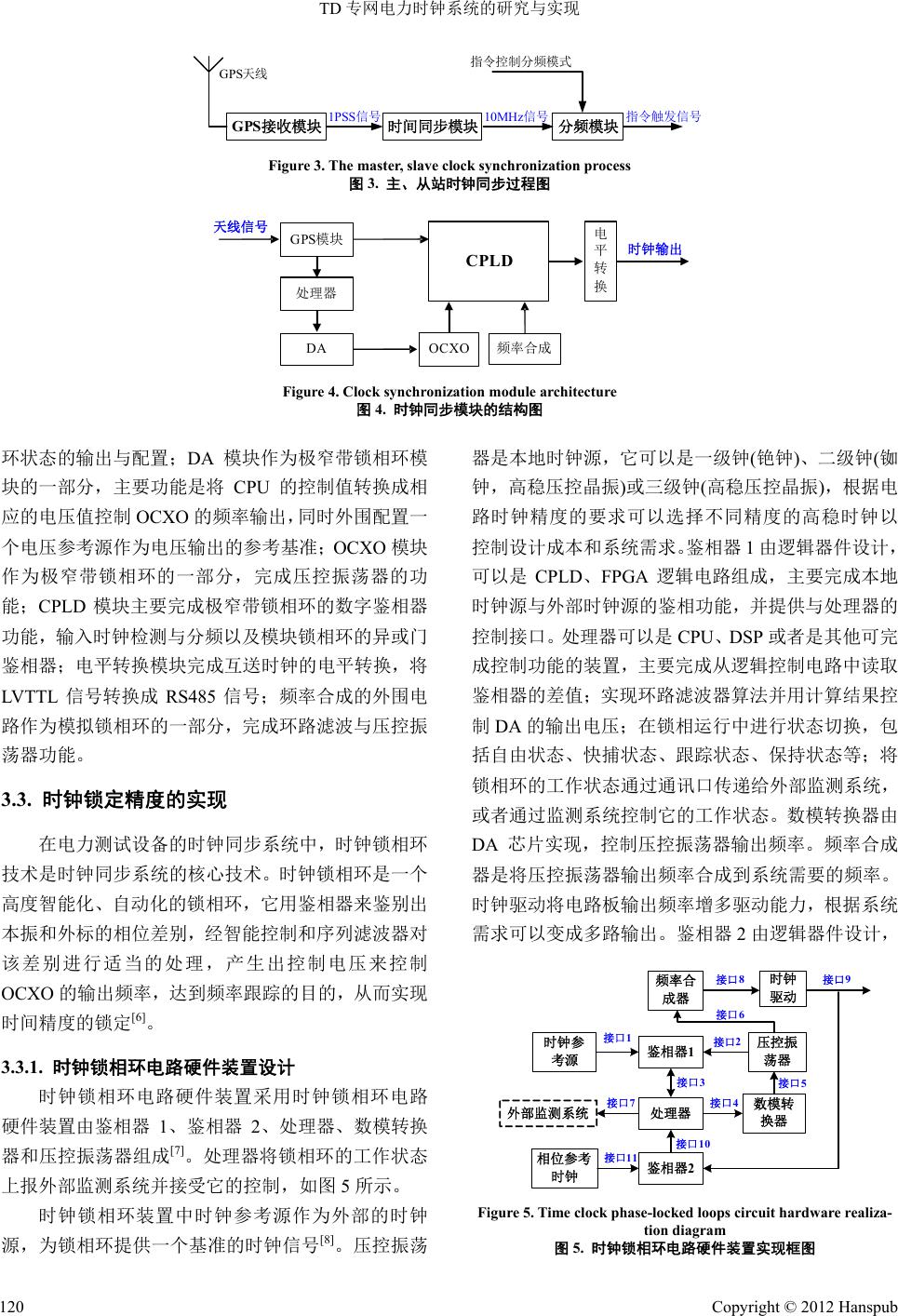

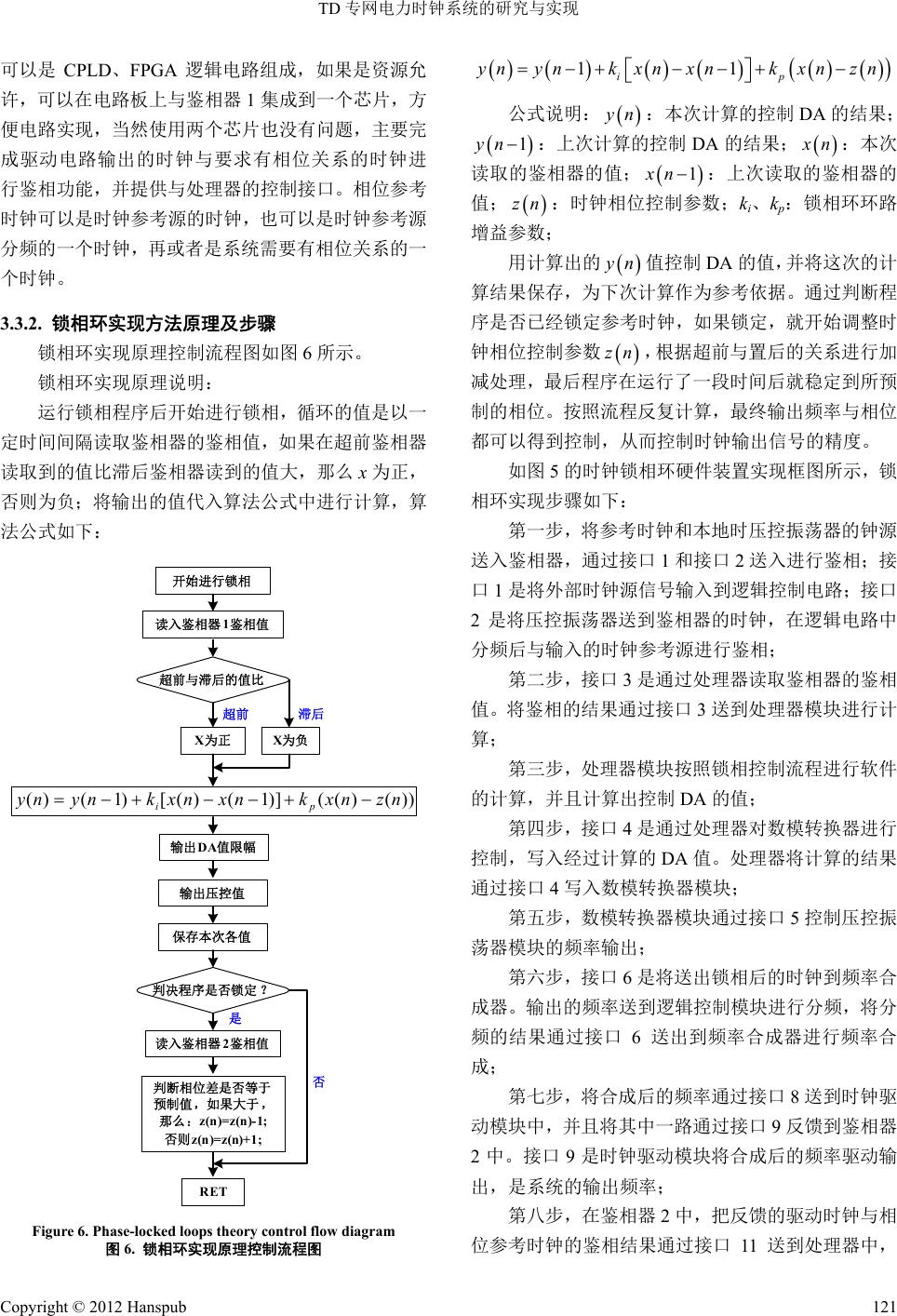

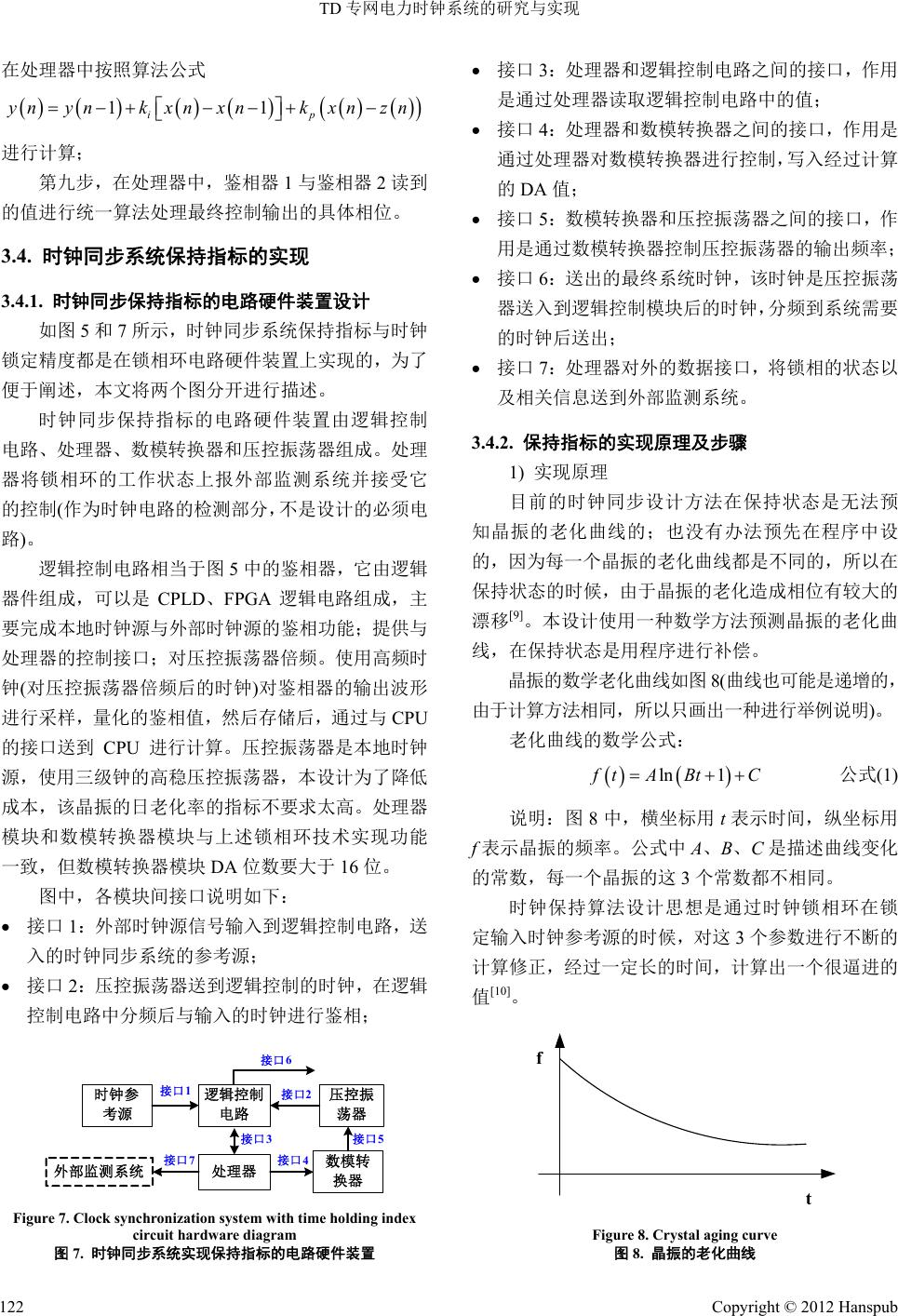

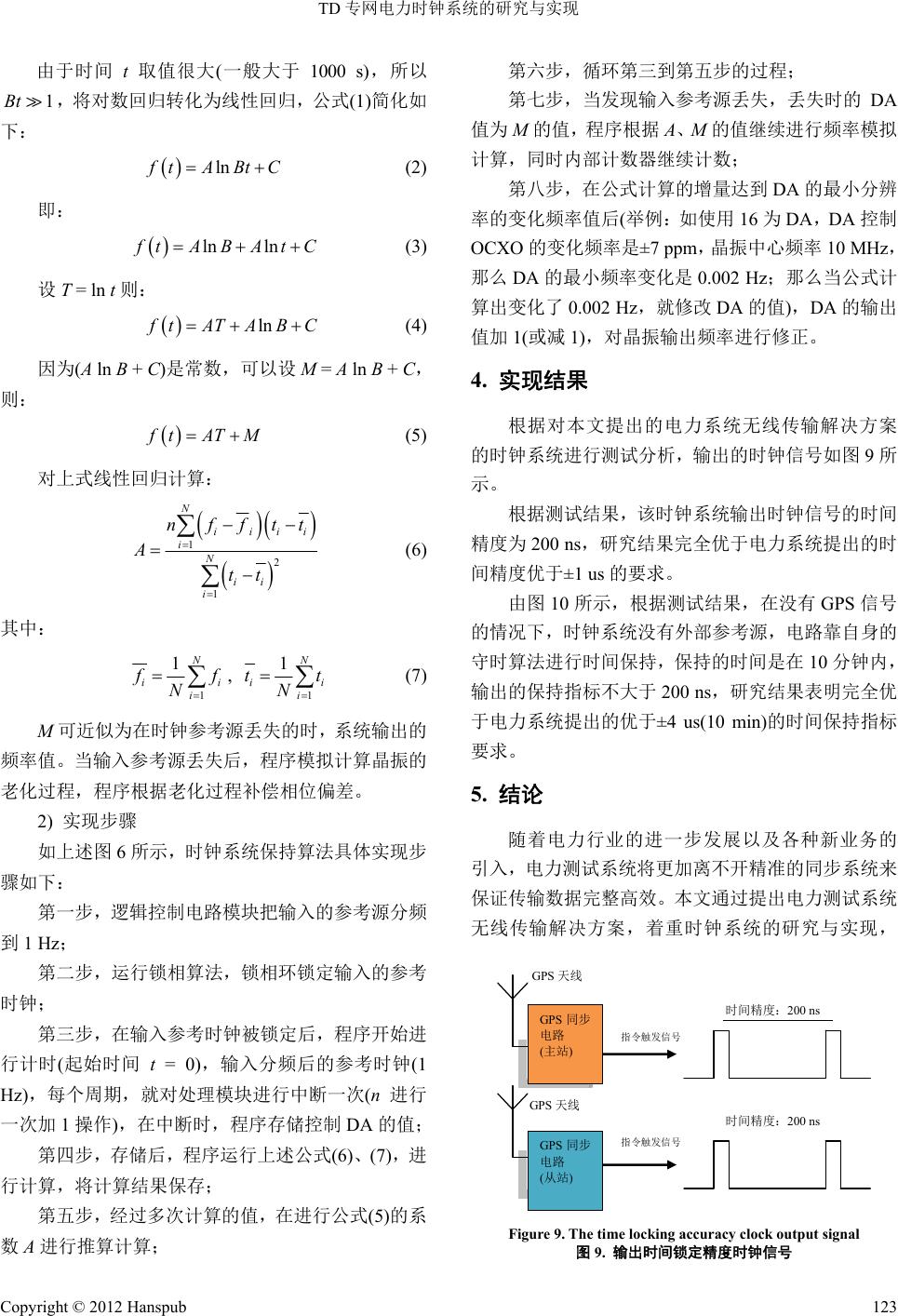

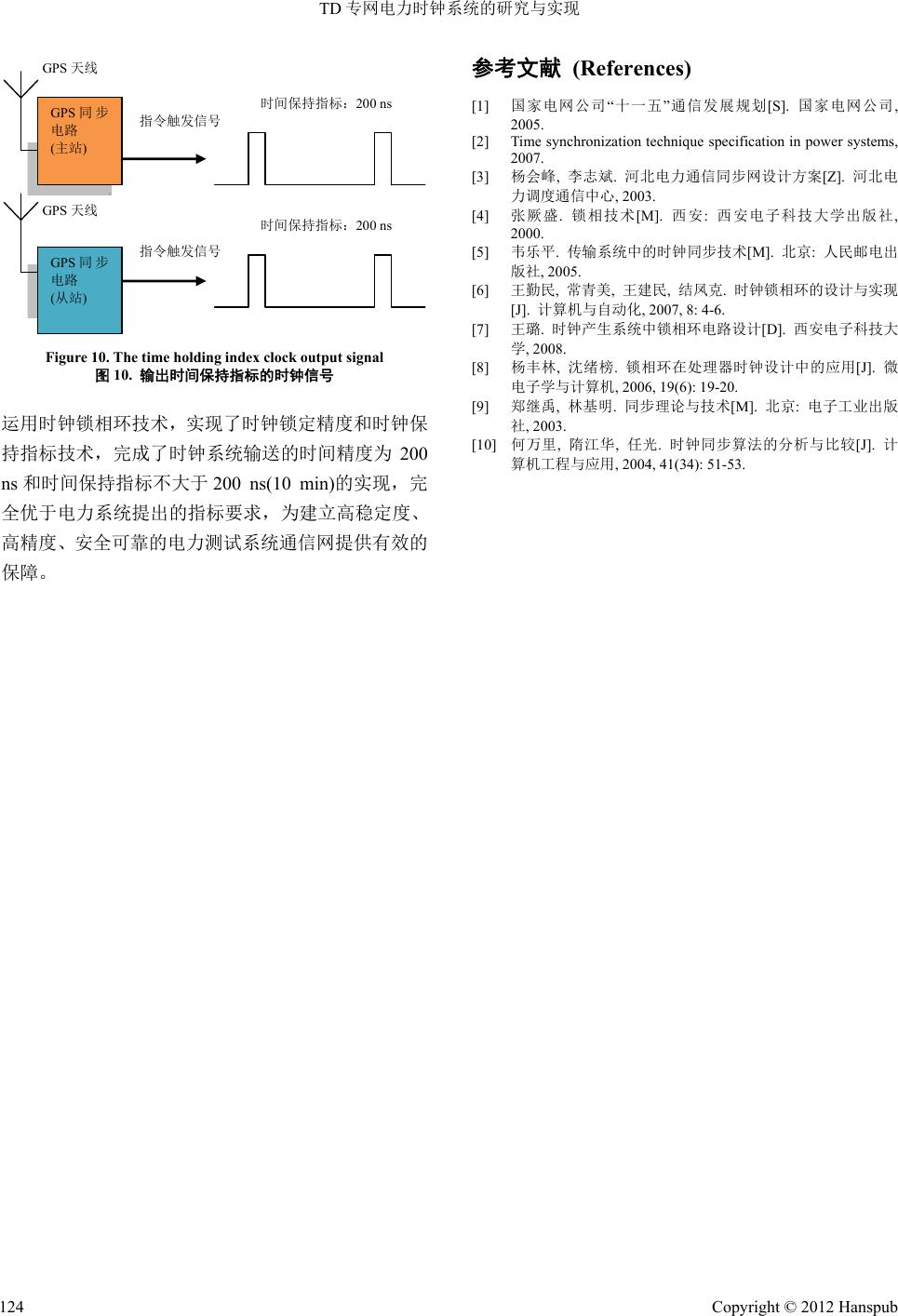

Smart Grid 智能电网, 2012, 2, 118-124 http://dx.doi.org/10.12677/sg.2012.24021 Published Online December 2012 (http://www.hanspub.org/journal/sg.html) Study and Achievement of the Power Clock System Based on TD Private Network Jian Xue Shanxi Electric Power Research Institute, Xi’an Email: 13772135855@126.com Received: Nov. 6th , 2012; revised: Nov. 20th, 2012; accepted: Nov. 30th, 2012 Abstract: According to the requirements of clock synchronization in the solution of the wireless transmission which based on TD-SCDMA power intelligent testing system network, the clock synchronization system is researched em- phatically in this paper. The precision of clock lock and the holding index of time is researched and analysed in the pa- per by using Phase-locked loops technology. AS the implementation results shows that both of the time synchronizatio n accuracy and the time holding index is two hundreds nanosecond, which is superior to the requirement of the power testing system. It improves the testing accuracy of the power testing system efficiently. Keywords: Power Testing System; Clock Synchronization; PLL TD 专网电力时钟系统的研究与实现 薛 建 陕西电力科学研究院,西安 Email: 13772135855@126.com 收稿日期:2012 年11 月6日;修回日期:2012 年11 月20 日;录用日期:2012 年11 月30 日 摘 要:本文根据 TD专网电力测试系统的无线传输解决方案对时钟系统的要求,重点对时钟同步系统进行了 研究。文中运用时钟锁相环技术,对时钟锁定精度和时钟保持指标进行了研究与分析。通过实现结果表明,该 时钟系统输出的时钟同步精度为 200 ns的时钟信号及 200 ns的时间保持指标,完全优于电力测试系统提出的指 标要求,有效提高了电力测试系统的测试精确度。 关键词:电力测试系统;时钟同步;锁相环 1. 引言 随着新一代移动通讯业务的产生和全面投入,无 线移动数据通讯的应用也越来越广泛。电力行业作为 国民经济的基础产业,对通信的要求也越来越高[1]。 由于电力测试系统中的 GPS 信号在传送过程中有各 种干扰,造成该信号抖动存在。在一些特殊的环境中, 会出现无法接收到 GPS卫星信号,造成模块失锁,设 备会出现时钟不准的情况。而目前国内的时钟设备提 供的时钟指标较低,远远不能满足电力系统越来越高 的时钟指标要求[2]。根据此现状,通过与大唐移动合 作开发智能电网测试系统,本文提出基于 TD 专网的 电力测试系统的无线传输解决方案,在该方案中为电 力测试系统提供高精度的时钟参考源。 本文利用大唐移动在时钟同步技术方面的多年 技术积累,结合一种新的时钟锁相环的设计方法,着 重研究了电力测试系统的时钟系统。在研究智能检测 系统时钟信号发生器时,通过时钟锁相环技术,锁定 输入的 GPS 时钟信号,将 GPS接收信号进行二次锁 Copyright © 2012 Hanspub 118  TD 专网电力时钟系统的研究与实现 相处理,可以消除环境造成的抖动和失锁等现象,解 决了锁相环输出时钟的频率与相位同时控制问题,可 为电力系统测试设备提供一个高性能、高稳定度、和 高精确度的时钟同步系统。 2. 电力测试系统方案 根据电力系统提出时钟输出时间精度优于±1 us 的时钟信号及优于±4 us(10 min)的时间保持指标,本 文提出电力测试系统无线传输解决方案,如图 1所示。 该方案由主站设备和 15 套从站设备组成,主站设备 包括综合接入控制设备、无线主站和操作维护台,每 套从站设备都有同步与无线接收设备,而每个同步与 无线接收设备都有自己的时钟系统[3]。该方案的无线 传输系统通过使用无线方式来传输测试信号,主站通 过无线方式下发控制命令,从站通过无线方式返回测 试结果。在该方案的时钟系统中,运用时钟锁相环技 术,实现了测试系统中设备间的同步功能,并为电力 测试系统提供了一个高精度的时钟信号[4]。 3. 时钟系统的研究与实现 3.1. 时钟同步实现方案 根据提出的电力测试系统无线传输解决方案,主 站与信号源之间采用无线方式传输数据和时间信号, 当多个信号源发出数据时,需要同步这些信号源的时 间,以便主站同时能接收多个信号源的消息和数据, 有准确的时钟参考。主站和从站的时间同步方案如图 2和图 3所示。 在主站和从站上设置时钟系统的 GPS 天线,主站 通过 GPS 天线接收信号源发出的信息,经 GPS接收 模块输出 1 PPS信号。然后,通过时间同步模块把输 出的 1 PPS信号进行时钟频率合成,生成 10 MHz信 号,再经分频模块将频率分成脉冲信号,通过频率合 成模块后输出的时钟精度优于200 ns的时钟信号。在 无GPS 信号的情况下,通过该时钟系统的同步过程, 时间保持指标可达到 200 ns。 3.2. 时钟同步模块 根据电力测试系统对时钟同步的要求,当从站与 主站进行无线数据传输时,从站通过 GPS 天线接收 GPS 卫星信号获取时间信息,利用时钟同步模块来实 现时钟系统,设计的时钟同步模块如图 4所示[5]。 该时钟同步模块包括GPS 模块、处理器模块、 DA 模块、OCXO 模块、CPLD模块、电平转换模块 和频率合成模块。GPS 模块接收 GPS 卫星信号获取时 间信息,并将时间信息传送到处理器;处理器模块主 完成极窄带锁相环的数字滤波器的软件实现,锁相 要 Figure 1. The power testing system solution 图1. 电力测试系统方案组网框图 电脑 主站 从站1从站2从站15 …… GPS天线 TD 模块 GPS天线 TD模块 Figure 2. The master, slave clock synchronization solution 图2. 主、从站时钟同步方案 Copyright © 2012 Hanspub 119  TD 专网电力时钟系统的研究与实现 GPS接收模块时间同步模块分频模块 指令触发信号1PSS信号 10MHz信号 GPS天线 指令控制分频模式 Figure 3. The master, slave clock synchronization process 图3. 主、从站时钟同步过程图 天线信号 时钟输出 GPS模块 处理器 DA OCXO CPLD 频率合成 电 平 转 换 Figure 4. Clock synchroniz ation module architecture 图4. 时钟同步模块的结构图 环状态的输出与配置;DA模块作为极窄带锁相环模 块的一部分,主要功能是将CPU 的控制值转换成相 应的电压值控制 OCXO 的频率输出,同时外围配置一 个电压参考源作为电压输出的参考基准;OCXO 模块 作为极窄带锁相环的一部分,完成压控振荡器的功 能;CPLD 模块主要完成极窄带锁相环的数字鉴相器 功能,输入时钟检测与分频以及模块锁相环的异或门 鉴相器;电平转换模块完成互送时钟的电平转换,将 LVTTL 信号转换成 RS485 信号;频率合成的外围电 路作为模拟锁相环的一部分,完成环路滤波与压控振 荡器功能。 3.3. 时钟锁定精度的实现 在电力测试设备的时钟同步系统中,时钟锁相环 技术是时钟同步系统的核心技术。时钟锁相环是一个 高度智能化、自动化的锁相环,它用鉴相器来鉴别出 本振和外标的相位差别,经智能控制和序列滤波器对 该差别进行适当的处理,产生出控制电压来控制 OCXO 的输出频率,达到频率跟踪的目的,从而实现 时间精度的锁定[6]。 3.3.1. 时钟锁相环电路硬件装置设计 时钟锁相环电路硬件装置采用时钟锁相环电路 硬件装置由鉴相器 1、鉴相器 2、处理器、数模转换 器和压控振荡器组成[7]。处理器将锁相环的工作状态 上报外部监测系统并接受它的控制,如图 5所示。 时钟锁相环装置中时钟参考源作为外部的时钟 源,为锁相环提供一个基准的时钟信号[8]。压控振荡 器是本地时钟源,它可以是一级钟(铯钟)、二级钟(铷 钟,高稳压控晶振)或三级钟(高稳压控晶振),根据电 路时钟精度的要求可以选择不同精度的高稳时钟以 控制设计成本和系统需求。鉴相器 1由逻辑器件设计, 可以是 CPLD、FPGA 逻辑电路组成,主要完成本地 时钟源与外部时钟源的鉴相功能,并提供与处理器的 控制接口。处理器可以是CPU、DSP 或者是其他可完 成控制功能的装置,主要完成从逻辑控制电路中读取 鉴相器的差值;实现环路滤波器算法并用计算结果控 制DA 的输出电压;在锁相运行中进行状态切换,包 括自由状态、快捕状态、跟踪状态、保持状态等;将 锁相环的工作状态通过通讯口传递给外部监测系统, 或者通过监测系统控制它的工作状态。数模转换器由 DA 芯片实现,控制压控振荡器输出频率。频率合成 器是将压控振荡器输出频率合成到系统需要的频率。 时钟驱动将电路板输出频率增多驱动能力,根据系统 需求可以变成多路输出。鉴相器 2由逻辑器件设计, 频率合 成器 时钟 驱动 时钟参 考源 鉴相器1压控振 荡器 数模转 换器 处理器 相位参考 时钟 鉴相器2 外部监测系统 接口1接口2 接口3 接口4 接口5 接口6 接口7 接口8接口9 接口11 接口10 Figure 5. Time clock phase-locked loops circuit hardware realiza- tion diagram 图5. 时钟锁相环电路硬件装置实现框图 Copyright © 2012 Hanspub 120  TD 专网电力时钟系统的研究与实现 可以是 CPLD、FPGA 逻辑电路组成,如果是资源允 许,可以在电路板上与鉴相器 1集成到一个芯片,方 便电路实现,当然使用两个芯片也没有问题,主要完 成驱动电路输出的时钟与要求有相位关系的时钟进 行鉴相功能,并提供与处理器的控制接口。相位参考 时钟可以是时钟参考源的时钟,也可以是时钟参考源 分频的一个时钟,再或者是系统需要有相位关系的一 个时钟。 3.3.2. 锁相环实现方法原理及步骤 锁相环实现原理控制流程图如图 6所示。 锁相环实现原理说明: 运行锁相程序后开始进行锁相,循环的值是以一 定时间间隔读取鉴相器的鉴相值,如果在超前鉴相器 读取到的值比滞后鉴相器读到的值大,那么 x为正, 否则为负;将输出的值代入算法公式中进行计算,算 法公式如下: 开始进行锁相 读入鉴相器 1鉴相值 超前与滞后的值比 X为正 X为负 ))()(()]1()([)1()( nznxknxnxknyny pi 输出DA值限幅 输出压控值 保存本次各值 判决程序是否锁定 ? 读入鉴相器 2鉴相值 判断相位差是否等于 预制值,如果大于 , 那么:z(n)=z(n)-1; 否则z(n)= z(n )+1; RET 是 否 超前 滞后 Figure 6. Phase-locked loops theory control flow diagram 图6. 锁相环实现原理控制流程图 11 ip ynynkxnxnkxnzn 公式说明: y n:本次计算的控制 DA 的结果; 1yn :上次计算的控制 DA的结果; x n:本次 读取的鉴相器的值; 1xn :上次读取的鉴相器的 值; zn:时钟相位控制参数;ki、kp:锁相环环路 增益参数; 用计算出的 y n值控制 DA 的值,并将这次的计 算结果保存,为下次计算作为参考依据。通过判断程 序是否已经锁定参考时钟,如果锁定,就开始调整时 钟相位控制参数 zn,根据超前与置后的关系进行加 减处理,最后程序在运行了一段时间后就稳定到所预 制的相位。按照流程反复计算,最终输出频率与相位 都可以得到控制,从而控制时钟输出信号的精度。 如图 5的时钟锁相环硬件装置实现框图所示,锁 相环实现步骤如下: 第一步,将参考时钟和本地时压控振荡器的钟源 送入鉴相器,通过接口 1和接口 2送入进行鉴相;接 口1是将外部时钟源信号输入到逻辑控制电路;接口 2是将压控振荡器送到鉴相器的时钟,在逻辑电路中 分频后与输入的时钟参考源进行鉴相; 第二步,接口 3是通过处理器读取鉴相器的鉴相 值。将鉴相的结果通过接口 3送到处理器模块进行计 算; 第三步,处理器模块按照锁相控制流程进行软件 的计算,并且计算出控制 DA 的值; 第四步,接口 4是通过处理器对数模转换器进行 控制,写入经过计算的 DA 值。处理器将计算的结果 通过接口 4写入数模转换器模块; 第五步,数模转换器模块通过接口 5控制压控振 荡器模块的频率输出; 第六步,接口 6是将送出锁相后的时钟到频率合 成器。输出的频率送到逻辑控制模块进行分频,将分 频的结果通过接口 6送出到频率合成器进行频率合 成; 第七步,将合成后的频率通过接口 8送到时钟驱 动模块中,并且将其中一路通过接口 9反馈到鉴相器 2中。接口 9是时钟驱动模块将合成后的频率驱动输 出,是系统的输出频率; 第八步,在鉴相器 2中,把反馈的驱动时钟与相 位参考时钟的鉴相结果通过接口11 送到处理器中, Copyright © 2012 Hanspub 121  TD 专网电力时钟系统的研究与实现 在处理器中按照算法公式 11 ip ynynkxnxnkxn zn 进行计算; 第九步,在处理器中,鉴相器 1与鉴相器 2读到 的值进行统一算法处理最终控制输出的具体相位。 3.4. 时钟同步系统保持指标的实现 3.4.1. 时钟同步保持指标的电路硬件装置设计 如图 5和7所示,时钟同步系统保持指标与时钟 锁定精度都是在锁相环电路硬件装置上实现的,为了 便于阐述,本文将两个图分开进行描述。 时钟同步保持指标的电路硬件装置由逻辑控制 电路、处理器、数模转换器和压控振荡器组成。处理 器将锁相环的工作状态上报外部监测系统并接受它 的控制(作为时钟电路的检测部分,不是设计的必须电 路)。 逻辑控制电路相当于图 5中的鉴相器,它由逻辑 器件组成,可以是CPLD、FPGA逻辑电路组成,主 要完成本地时钟源与外部时钟源的鉴相功能;提供与 处理器的控制接口;对压控振荡器倍频。使用高频时 钟(对压控振荡器倍频后的时钟)对鉴相器的输出波形 进行采样,量化的鉴相值,然后存储后,通过与CPU 的接口送到 CPU进行计算。压控振荡器是本地时钟 源,使用三级钟的高稳压控振荡器,本设计为了降低 成本,该晶振的日老化率的指标不要求太高。处理器 模块和数模转换器模块与上述锁相环技术实现功能 一致,但数模转换器模块 DA 位数要大于 16 位。 图中,各模块间接口说明如下: 接口 1:外部时钟源信号输入到逻辑控制电路,送 入的时钟同步系统的参考源; 接口 2:压控振荡器送到逻辑控制的时钟,在逻辑 控制电路中分频后与输入的时钟进行鉴相; 时钟参 考源 逻辑控制 电路 压控振 荡器 数模转 换器 处理器外部监测系统 接口1接口2 接口3 接口4 接口5 接口7 接口6 Figure 7. Clock synchroniz ation system with time holding index circuit hardware diagram 图7. 时钟同步系统实现保持指标的电路硬件装置 接口 3:处理器和逻辑控制电路之间的接口,作用 是通过处理器读取逻辑控制电路中的值; 接口 4:处理器和数模转换器之间的接口,作用是 通过处理器对数模转换器进行控制,写入经过计算 的DA 值; 接口 5:数模转换器和压控振荡器之间的接口,作 用是通过数模转换器控制压控振荡器的输出频率; 接口 6:送出的最终系统时钟,该时钟是压控振荡 器送入到逻辑控制模块后的时钟,分频到系统需要 的时钟后送出; 接口 7:处理器对外的数据接口,将锁相的状态以 及相关信息送到外部监测系统。 3.4.2. 保持指标的实现原理及步骤 1) 实现原理 目前的时钟同步设计方法在保持状态是无法预 知晶振的老化曲线的;也没有办法预先在程序中设 的,因为每一个晶振的老化曲线都是不同的,所以在 保持状态的时候,由于晶振的老化造成相位有较大的 漂移[9]。本设计使用一种数学方法预测晶振的老化曲 线,在保持状态是用程序进行补偿。 晶振的数学老化曲线如图 8(曲线也可能是递增的, 由于计算方法相同,所以只画出一种进行举例说明)。 老化曲线的数学公式: ln 1 f tABt C 公式(1) 说明:图 8中,横坐标用t表示时间,纵坐标用 f表示晶振的频率。公式中A、B、C是描述曲线变化 的常数,每一个晶振的这 3个常数都不相同。 时钟保持算法设计思想是通过时钟锁相环在锁 定输入时钟参考源的时候,对这 3个参数进行不断的 计算修正,经过一定长的时间,计算出一个很逼进的 值[10]。 f t Figure 8. Crystal aging curve 图8. 晶振的老化曲线 Copyright © 2012 Hanspub 122  TD 专网电力时钟系统的研究与实现 由于时间t取值很大(一般大于 1000 s),所以 ,将对数回归转化为线性回归,公式(1)简化如 下: 1Bt ln f tABtC (2) 即: ln ln f tABAtC (3) 设T = ln t则: ln f tATABC (4) 因为(A ln B + C)是常数,可以设 M = A ln B + C, 则: f tATM (5) 对上式线性回归计算: 1 2 1 N ii i iN ii i nfftt A tt i (6) 其中: 1 1N ii i f f N , 1 1N i i t N i t (7) M可近似为在时钟参考源丢失的时,系统输出的 频率值。当输入参考源丢失后,程序模拟计算晶振的 老化过程,程序根据老化过程补偿相位偏差。 2) 实现步骤 如上述图 6所示,时钟系统保持算法具体实现步 骤如下: 第一步,逻辑控制电路模块把输入的参考源分频 到1 Hz; 第二步,运行锁相算法,锁相环锁定输入的参考 时钟; 第三步,在输入参考时钟被锁定后,程序开始进 行计时(起始时间t = 0),输入分频后的参考时钟(1 Hz),每个周期,就对处理模块进行中断一次(n进行 一次加 1操作),在中断时,程序存储控制 DA的值; 第四步,存储后,程序运行上述公式(6)、(7),进 行计算,将计算结果保存; 第五步,经过多次计算的值,在进行公式(5)的系 数A进行推算计算; 第六步,循环第三到第五步的过程; 第七步,当发现输入参考源丢失,丢失时的DA 值为 M的值,程序根据 A、M的值继续进行频率模拟 计算,同时内部计数器继续计数; 第八步,在公式计算的增量达到 DA 的最小分辨 率的变化频率值后(举例:如使用 16 为DA,DA 控制 OCXO 的变化频率是±7 ppm,晶振中心频率 10 MHz, 那么 DA 的最小频率变化是0.002 Hz;那么当公式计 算出变化了 0.002 Hz,就修改 DA 的值),DA 的输出 值加 1(或减 1),对晶振输出频率进行修正。 4. 实现结果 根据对本文提出的电力系统无线传输解决方案 的时钟系统进行测试分析,输出的时钟信号如图 9所 示。 根据测试结果,该时钟系统输出时钟信号的时间 精度为 200 ns,研究结果完全优于电力系统提出的时 间精度优于±1 us的要求。 由图 10 所示,根据测试结果,在没有 GPS信号 的情况下,时钟系统没有外部参考源,电路靠自身的 守时算法进行时间保持,保持的时间是在 10 分钟内, 输出的保持指标不大于 200 ns,研究结果表明完全优 于电力系统提出的优于±4 us(10 min)的时间保持指标 要求。 5. 结论 随着电力行业的进一步发展以及各种新业务的 引入,电力测试系统将更加离不开精准的同步系统来 保证传输数据完整高效。本文通过提出电力测试系统 无线传输解决方案,着重时钟系统的研究与实现, 时间精度:20 0 ns 时间精度:20 0 ns 指令触发信号 指令触发信号 GPS 天线 GPS 天线 GPS 同步 电路 (主站) GPS 同步 电路 (从站) Figure 9. The time locking accuracy clock output signal 图9. 输出时间锁定精度时钟信号 Copyright © 2012 Hanspub 123  TD 专网电力时钟系统的研究与实现 Copyright © 2012 Hanspub 124 参考文献 (References) GPS 天线 GPS 同步 电路 (主站) GPS 天线 GPS 同步 电路 (从站) 指令触发信号 指令触发信号 时间保持指标:200 ns 时间保持指标:200 ns [1] 国家电网公司“十一五”通信发展规划[S]. 国家 电网公司, 2005. [2] Ti me synchronization technique specification in power systems, 2007. [3] 杨会峰, 李志斌. 河北电力通信同步网设计方案[Z]. 河北电 力调度通信中心, 2003. [4] 张厥盛. 锁相技术[M]. 西安: 西安电子科技大学出版社, 2000. [5] 韦乐平. 传输系统中的时钟同步技术[M]. 北京: 人民邮电出 版社, 2005. [6] 王勤民, 常青美, 王建民, 结凤克. 时钟锁相环的设计与实现 [J]. 计算机与自动化, 2007, 8: 4-6. [7] 王璐. 时钟产生系统中锁相环电路设计[D]. 西安电子科技大 学, 2008. Figure 10. The time holding index clock output signal [8] 杨丰林, 沈绪榜. 锁相环在处理器时钟设 计中的应用[J]. 微 电子学与计算机, 2006, 19(6): 19-20. 图10. 输出时间保持指标的时钟信号 [9] 郑继禹, 林基明. 同步理论与技术[M]. 北京: 电子工业出版 社, 2003. 运用时钟锁相环技术,实现了时钟锁定精度和时钟保 持指标技术,完成了时钟系统输送的时间精度为 200 ns 和时间保持指标不大于 200 ns(10 min)的实现,完 全优于电力系统提出的指标要求,为建立高稳定度、 高精度、安全可靠的电力测试系统通信网提供有效的 保障。 [10] 何万里, 隋江华, 任光. 时钟同步算法的分析与比较[J]. 计 算机工程与应用, 2004, 41(34): 51-53. |